I

Изобретение может быть использовано при передаче телекодовой информации по каналам связи.

Известен способ исправления многократных разнесенных и сосредоточенных в пакеты ошибок, заключаюп ийся в разбиении на передающей стороне информационной импульсной последовательности длиной п на п отдельных подблока длиной HI кодировании каждого подблока, обнаруживающим ошибки (яь ki)кодом, кодировании, в свою очередь, одноименпых разрядов всех подблоков, исправляющим ошибки (п2, 2)-кодом И поочередной передаче всех подблоков по каналу связи, а на приемной стороне - проверке на обнаружение ошибок каждого подблока, стирании подблоков с обнаруженными ошибками, исправлении ошибок и восстановлении стираний в одноименных разрядах всех HZ подблоков, вырабатывании сигнала о наличии неисправимого сочетания ошибок и стирании всей информационной импульсной последовательности длиной п.

С целью более полного использования корректирующих возможностей используемого кода и ограничения увеличения числа подблоков, пораженных ошибками, по предлагаемому способу на приемной стороне одновременно с выполнением проверки на обнаружение ошибок каждого подблока записывают с помощью блока памяти всю информационную импульсную последовательность длиной п, определяют восстанавливаемость комбинации искаженных подблоков, исправляют ошибки («2, 2)-кодом последовательно в каждом столбце записанной с помощью блока памяти информационной импульсной последовательности длиной п, затем все подблоки последовательно проверяют на наличие ошибок с фиксацией искаженных подблоков и проверкой восстанавливаемости комбинаций искаженных подблоков, причем для восстанавливаемых комбинаций искаженных подблоков выполняют операции стирания

подблоков с обнаруженными ошибками, исправление ошибок и восстановление стираний в oднoиLMвнныx разрядах всех «2 подблоков, а для невосстанавливаемых комбинаций искаженных подблоков выполняют операцию стирания всей информационной импульсной последовательности длиной п; кроме того, исправление ошибок в одноименных разрядах подблоков выполняют только в подблоках, зафиксированных как искаженные при проверке на обнаружение ошибок каждого подблока.

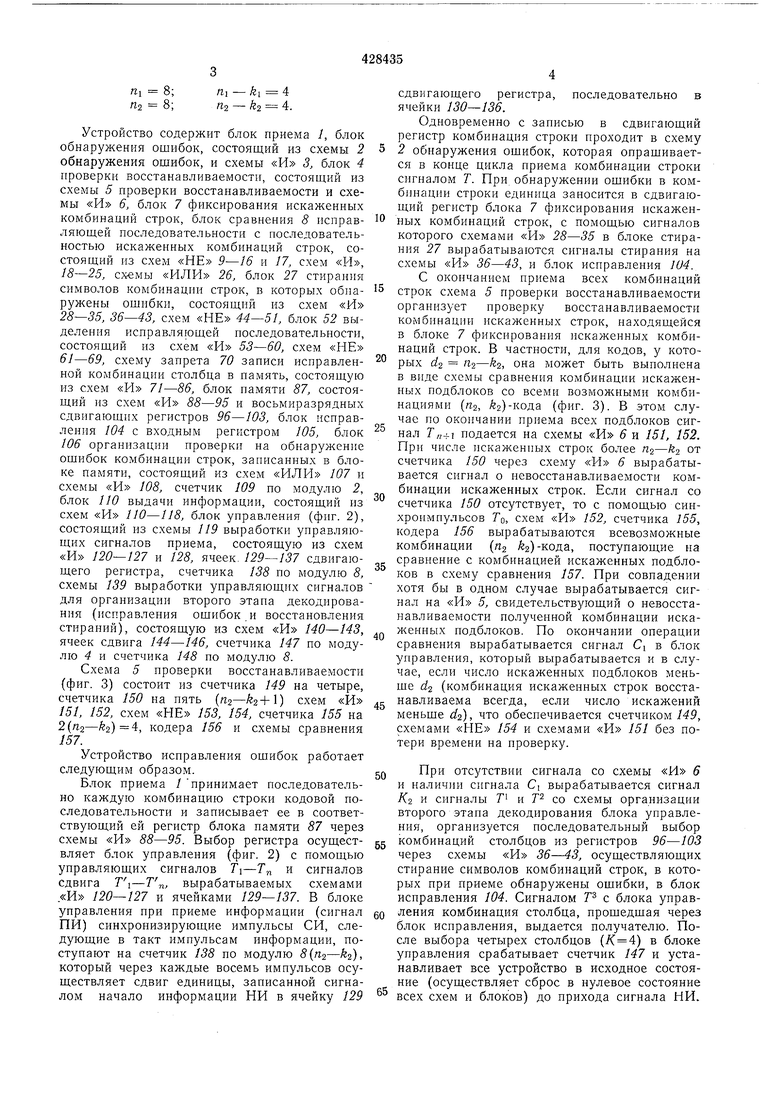

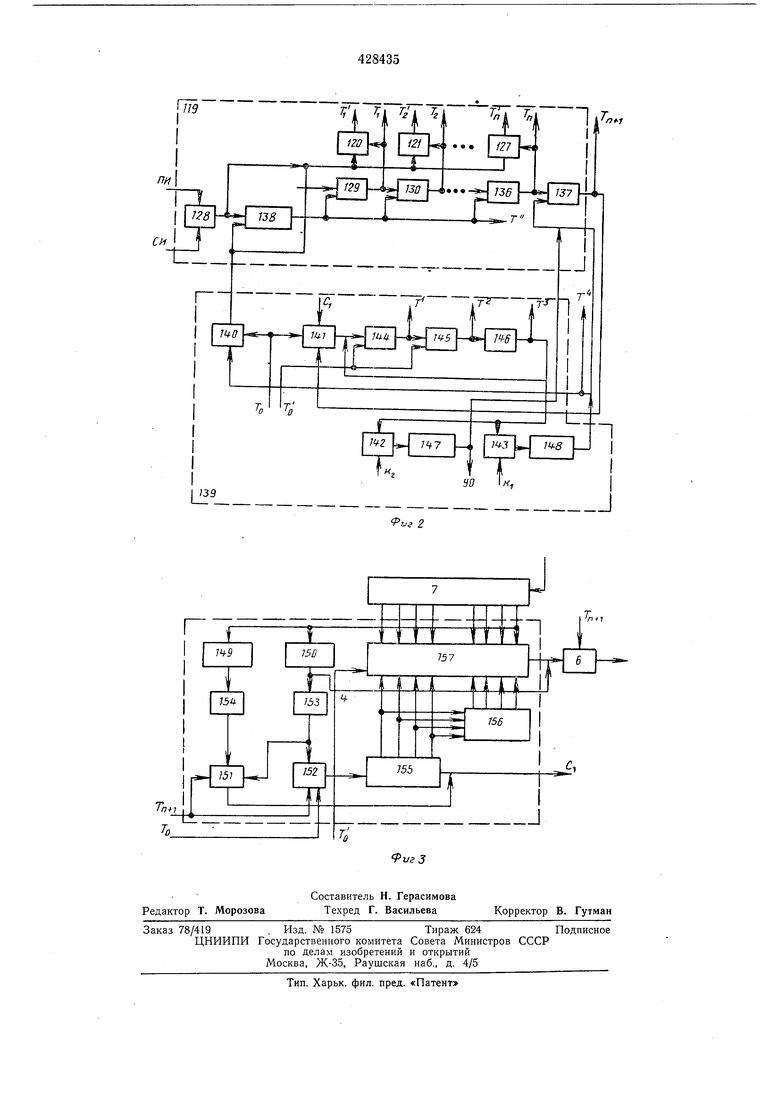

На фиг. 1, 2 и 3 приведены функциональные схемы устройства, реализующего предлагаемый способ для следующего варианта построения кодовой последовательности «1 8;«1 - 1 4 «2 8;«2 - 2 4. Устройство содержит блок приема 1, блок обнаружения ошибок, состоящий из схемы 2 обнаружения ошибок, и схемы «И 3, блок 4 проверки восстанавливаемости, состоящий из схемы 5 проверки восстанавливаемости и схемы «И 6, блок 7 фиксирования искаженных комбинаций строк, блок сравнения 8 исправляющей последовательности с последовательностью искаженных комбинаций строк, состоящий из схем «НЕ 9-16 и 17, схем «И, 18-25, схемы «ИЛИ 26, блок 27 стирания символов комбинации строк, в которых обпаружены ощибки, состоящий из схем «И 28-35, 36-43, схем «ИЕ 44-51, блок 52 выделения исправляющей последовательиости, состоящий из схем «И 53-60, схем «НЕ 61-69, схему запрета 70 записи исправленной комбинации столбца в память, состоящую из схем «PI 71-86, блок памяти 87, состоящий из схем «И 88-95 и восьмиразрядных сдвигающих регистров 96-103, блок исправления 104 с входным регистром 105, блок 106 организации проверки на обнаружение ощибок комбинации строк, записанных в блоке памяти, состоящий из схем «ИЛИ 107 и схемы «И 108, счетчик 109 по модулю 2, блок 110 выдачи информации, состоящий из схем «И 110-118, блок управления (фиг. 2), состоящий из схемы 119 выработки управляющих сигналов приема, состоящую из схем «И 120-127 и 128, ячеек 129-137 сдвигающего регистра, счетчика 138 по модулю 8, схемы 139 выработки управляющих сигналов для организации второго этапа декодирования (исправления ощибок.и восстановления стираний), состоящую из схем «И 140-143, ячеек сдвига 144-146, счетчика 147 по модулю 4 и счетчика 148 по модулю 8. Схема 5 проверки восстанавливаемости (фиг. 3) состоит из счетчика 149 на четыре. счетчика 150 на пять (п2-(2+1) схем «И 151, 152, схем «НЕ 153, 154, счетчика 155 на 2()4, кодера 156 и схемы сравнения 157. Устройство исправления ощибок работает следующим образом. Блок приема / принимает последовательно каждую комбинацию строки кодовой последовательности и записывает ее в соответствующий ей регистр блока памяти 87 через схемы «И 88-95. Выбор регистра осуществляет блок управления (фиг. 2) с помощью управляющих сигналов и сигналов сдвига Tl-Тп, вырабатываемых схемами .«И 120-127 и ячейками 129-137. В блоке управления при приеме информации (сигнал ПИ) синхронизирующие импульсы СИ, еледующие в такт импульсам информации, поступают на счетчик 138 по модулю 8(), который через каждые восемь импульсов осуществляет сдвиг единицы, записанной сигналом начало информации НИ в ячейку 129 сдвигающего регистра, последовательно ячейки 130-136. Одновременно с записью в сдвигающий регистр комбинация строки проходит в схему 2 обнаружения ощибок, которая опрашивается в конце цикла приема комбинации строки сигналом Т. При обнаружении ощибки в комбинации строки единица заносится в сдвигающий регистр блока 7 фиксирования искаженных комбинаций строк, с помощью сигналов которого схемами «И 28-35 в блоке стирания 27 вырабатываются сигналы стирания на схемы «И 36-43, и блок исправления 104. С окончанием приема всех комбинаций строк схема 5 проверки восстанавливаемости организует проверку восстанавливаемости комбинации искаженных строк, находящейся в блоке 7 фиксирования искаженных комбинаций строк. В частности, для кодов, у которых 2 т-1-kz, она может быть выполнена в виде схемы сравнения комбинации искаженных подблоков со всеми возмол ными комбинациями («2, Й2)-кода (фиг. 3). В этом случае по окончании приема всех подблоков сигнал Т„-LI подается на схемы «И в и 151, 152. При числе искаженных строк более от счетчика 150 через схему «И 6 вырабатывается сигнал о невосстанавливаемости комбинации искаженных строк. Если сигнал со счетчика 150 отсутствует, то с помощью синхроимпульсов Го, схем «И 152, счетчика 155, кодера 156 вырабатываются всевозможные комбинации («2 2)-кода, поступающие на сравнение с комбинацией искаженных подблоков в схему сравнения 157. При совпадении хотя бы в одном случае вырабатывается сигнал на «И 5, свидетельствующий о невосстанавливаемости полученной комбинации искаженных нодблоков. По окончании операции сравнения вырабатывается сигнал Ci в блок управления, который вырабатывается и в случае, если число искаженных подблоков меньще 2 (комбинация искаженных строк восстанавливаема всегда, если число искажений меньще dz), что обеспечивается счетчиком/49, схемами «НЕ 154 и схемами «Н 151 без потери времеии на проверку. При отсутствии сигнала со схемы «И 6 и наличии сигнала Cj вырабатывается сигнал KZ и сигналы Г и Р со схемы организации второго этаиа декодирования блока управления, организуется последовательный выбор комбинаций столбцов из регистров 96-103 через схемы «И 36-43, осуществляющих стирание символов комбинаций строк, в которых при приеме обнаружены ошибки, в блок исиравления 104. Сигналом Р с блока управления комбинация столбца, прощедщая через блок исправления, выдается получателю. Поеле выбора четырех столбцов (/(4) в блоке управления срабатывает счетчик 147 и устанавливает все устройство в исходное состояние (осуществляет сброс в нулевое состояние всех схем и блоков) до прихода сигнала НИ. Если установлено, что полученная комбинация искаженных строк при их стирании может оказаться невосстанавливаемой, то сигнал со схемы «И 6 поступает на триггер 158 и на счетчик 109 по модулю 9. Триггер 158 запрещает выдачу сигналов стирания со схем «И 28-35 на схемы «И 36-43 и в блок исправления 104. Кроме того, сигнал KI с триггера 158 поступает на схему «И 143, открывая вход на счетчик 148 по Ю модулю 8, который подсчитывает число комбинаций столбцов, прощедщих через блок исправления 104. Сигнал T,,+i, поступив в конце приема кодовой последовательности на схему «И 141, открывает вход синхроимпуль- 15 сов на сдвиг единицы в ячейках 144-146, обеспечивая выработку сигналов 7, Т, Р. С помощью сигналов Т Т, Т, осуществляющих выбор комбинаций столбцов из сдвигающих регистров 96-103, комбинации столбцов 20 через схемы «И 36-43 поступают во входной регистр 105 блока исправления. Из блока исправления 104 исправленная комбинация столбца поступает в блок 52 деления исправляющей последовательности на схемы 25 «И 53-60, на второй вход которых поступают сигналы с входного регистра 105, в котором находится неисправленная комбинация столбца. На выходе блока 52 образуется исправ- 30 ляющая последовательность, содержащая единичные символы на позициях, на которых в блоке исправления производится исправление символов на противоположные. Исправляющая последовательность со схем «НЕ 35 61-69 блока. 52 поступает в блок сравнения 8 на схемы «И 18-25 сравнения исправляющей последовательности с искажающей последовательностью, поступающей с блока 7 через схемы «НЕ 9-16 на вторые входы схем «И 18-25. В зависимости от результата сравнения в сдвигающие регистры 96-103 блока памяти 87 записывается либо комбинация, прощедщая исправление и находящаяся на выходе схем «И 79-86 (в случае несовпадения единичных символов исправляющей и искажающей последовательности ни в одном из разрядов), либо через схемы «И 71-78 неисправлениая комбинация, находящаяся во входном регистре 105 (в случае совпадения единичных символов хотя бы в одном из разрядов исправляющей и искажающей последовательностей). По окончании выбора из памяти и исправления восьмой комбинации столбца на выхо- S5 де счетчика 148 вырабатывается сигнал У , который прекращает выработку сигнала и подается па схемы «И 108, 140. Синхроимпульсы Го поступают через схему «И 140 на счетчик 138 и схемы «И 120-127, GO обеспечивающие выработку тактовых сигналов сдвига и организации перепроверк кодовой последовательпости по цегп-i: «ИЛР 107 - «И 108 - «ИЛИ 159 - схема 2 обнаружения ощибок - схема «И 88-95 в 6Е 5 сдвигающие регистры 96-103. Перепроверка происходит последовательно для каждой комбинации строки. По окончании перепроверки на выходе ячейки 137 появляется сигнал Т„+1, который поступает на схему «И 141, открывая проход синхроимпульсов на ячейки 144-146 и на схему проверки восстапавливаемости. Если комбинация искаженных строк, полученная в результате перепроверки признана певосстанавливаемой, то на выходе схемы «И 6 появляется сигнал, который поступает на счетчик 109, уже хранящий единицу. Сигнал, появляющийся в результате этого на выходе счетчика 109, свидетельствует о неисправимой комбинации ощибок и осуществляет сброс всей схемы в исходное состояние. Если сигна т схемой «И 6 не вырабатывается, то сигнал Ki с триггера 158 открывает схему «И 142, организуя (/(4)-циклов выбора комбинаций столбцов на блок исправления 104 ощибок и восстановления стираний с выдачей пнформации получателю. Таким образом, в случае, если число искаженных строк может образовать при их стирании невосстанавливаемое сочетание стертых позиций в комбинациях столбцов, то организуется исправление ощибок (без стирания строк) в П; комбинациях столбцов с последующей перепроверкой кодовой последовательности, записанной в блоке памяти. Если и после перепроверки окажется, что комбинация искаженных строк является иевосстанавливаемой, то принимается рещение о наличии неисправпмого сочетания ошибок. Если же после проведения исправления ощибок в столбцах («2,2)кода и последующей перепроверки окажется, что число искаженных комбинаций строк при их стирании образует восстанавливаемое сочетание стертых позиций, то организуется стирание искаженных строк с последуюи им исправлением ощибок и восстановлением стираний в комбинациях одноименных разрядов комбинаций строк (комбинациях столбцов). Предлагаемый способ исправления ошибок обеспечивает значительное уменьщение вероятности стирания (отказа от декодирования) кодовой последовательности за счет использования дополнительных возможностей исправлять значительное число сочетаний ощибок. Предмет изобретения 1. Способ исправления многократных разнесенных и сосредоточенных в пакеты ощпбок, заключающийся в разбиении на передающей стороне информационной импульсной последовательности длиной п па п, отдельных подблока длиной «i кодирования каждого подблока обнаруживающим ощибки (п, k)кодом, кодировании, в свою очередь, одноименных разрядов всех подблоков исправляющим ощибки («2, 2)-кодом И поочередной передаче всех подблоков по каналу связи, а

на приемной стороне - проверке на обнаружение ошибок каждого 1юдб„чока, стирании подблоков с обнаруженными ошибками, исправлении ошибок и восстановлении стираний в одноименных разрядах всех упомянутых П2 подблоков, вырабатывании сигнала о наличин ненсиравимого сочетания ошибок и стирании всей информационной импульсной последовательности длиной п, отличающийся тем, что, с целью более полного использования корректирующих возможностей исиользуемого кода, на приемной стороне одновременно с выполнением проверки иа обнаружение ошибок каждого подблока записывают с помошью блока памяти всю информацнонную импульсную последовательность длиной п, определяют восстанавливаемость комбинации искаженных подблоков, исправляют ошибки (л2, feg)-кодом последовательно в каждом столбце записанной с помощью блока памятн информационной импульсной последовательности длиной п, затем .в.се подблоки последовательно проверяют на наличие ошибок с фиксацией искаженных подблоков и проверкой восстанавливаемостн комбинации искаженных нодблоков, причем для восстанавливаемых комбинаций искаженных подблоков выполняют .операции стирания подблоков с обнаруженными ошибками, исправление ошибок и .восстановление стирадий в одноименных разряд.ах всех «2 подблоков, а для невосстанавливаемых ,ко;мбинаций искаженных нодблоков вынолняют операцию стирания всей информационной импульсной последовательности длиной п.

2. Снособ по н. 1, отличающийся тем, что, с целью ограничения увеличения числа подблоков, пораженных ошибками, исправление ошибок в одноименных разрядах подблоков выполняют только в подблоках, зафик-сироващных как искаженные нри ;нраве.рке на обнаружение ошибок каждого подблока.

I

Рг/г 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство исправления ошибок | 1972 |

|

SU446946A1 |

| УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОШИБОК В КОДОВОЙ КОМБИНАЦИИ | 1972 |

|

SU335689A1 |

| Устройство для исправления ошибок в информации, закодированной циклическим кодом | 1974 |

|

SU512589A1 |

| Устройство для исправления ошибок при декодировании кодовых комбинаций телеграфных сигналов | 1976 |

|

SU604169A2 |

| Устройство для исправления ошибок в системе передачи дискретной информации | 1984 |

|

SU1177927A2 |

| УСТРОЙСТВО для КОРРЕКЦИИ ДВУМЕРНОГО ИТЕРАТИВНОГО КОДА | 1972 |

|

SU332462A1 |

| Устройство для исправления ошибок в кодовой комбинации | 1974 |

|

SU526898A1 |

| УСТРОЙСТВО для ИСПРАВЛЕНИЯ ОШИБОК В МНОГОРЯДОВОЙ СИСТЕМЕ ПЕРЕДАЧИ ДАННЫХ | 1968 |

|

SU208348A1 |

| СПОСОБ ИСПРАВЛЕНИЯ МНОГОКРАТНЫХ ПАКЕТОВ ОШИБОК | 1965 |

|

SU174207A1 |

| Система для передачи и приема дискретной информации | 1979 |

|

SU903850A1 |

Даты

1974-05-15—Публикация

1972-01-26—Подача