1

РЬобретение относится к многоканальным системам связи, а именно к устройствам для асинхронного сопряжения в синхронном канале связи и может быть использовано в аппаратуре асинхронной передачи цифровой информации.

Известны устройства для асинхронного ввода двоичной информации в синхронный канал связи без дополнительного канала. В этих случаях в канал связи приходится вводить ие только информацию о полярности передаваемого сигнала, но и иЕ формацию о его тактовой частоте. Эта дополнительная информация обычио передается путем вставок в передаваемый сигнал вспомогательных посылок, которые обнаруживаются на приеме и сигнализируют об определенных значениях фазового сдвига между посылками входного сигнала и отводимыми для его передачи тактовыми посылками каиала связи.

В качестве вспомогательных посылок используют либо дублирующие посылки, т. е. иовторяюш,ие предыдущие посылки, либо дублирующие посылки совместно с инверсными посылками, т. е. имеющие полярность, обратную полярпости предществующих посылок. При этом сигнализация о фазовом сдвиге осуществляется изменением последовательности передачи инверсных и дублирующих посылок.

2

Однако при реализации известных устройств появление во входиом сигнале длительных групп посылок одной полярности соответствует передаче по линии связи большого числа повторяющих, т. е. дублирующих друг друга, посылок. Эти посылки маскируют вспомогательные дублирующие посылки, затрудняя нахождение их в принятом сигнале. Затрудняется также нахождение одиночной вспомогательной инверсной посылки, так как информационная посылка, передаваемая после вспомогательной инверсиой и повторяющая предществующую информационную посылку, в принятом сигнале оказывается инверсной посылкой. В инверсных устройствах время обнаружения всномогательных посылок (время поиска синхронизма) зависит от статистических свойств передаваемого сигнала.

Целью изобретения является повышение достоверности передачи информации и умепьщение времени вхождения в синхронизм.

Для этого на передающей стороне (m-fl)-M и ()-и выходами распределителя с одной стороны и выходом блока формироваиия дублирующих посылок с другой стороны включены последовательно соединенные схемы «Р1ЛИ и «Заирет и блок формирования инверсных посылок, причем к второму входу схемы «Запрет подключен выход блока периодического переключения, к одному входу

которого подключен выход блока однократного изменения периода, а к другому входу - (т4-2)-й выход распределителя, а на приемной стороне - менаду входом и (т+2)-м выходом распределителя включен блок периоднческого переключения, выход которого подключен к второму входу приемника синхронизации через последовательпо соединенные блок выделения инверсных посылок, сигнальный вход которого соединен с соответствующим входом блока выделения дублирующих посылок, и схему «РШИ, к второму входу которой подключен выход блока выделения дублирующих посылок, здесь т - число информационных посылок в цикле транслируемого сигнала.

В предложенном устройстве в транслируемый сигнал вводятся сдвоенные вспомогательные посылки, разделяющие сигналы на циклы, каждый из которых содержит т информационных и две вспомогательные посылки.

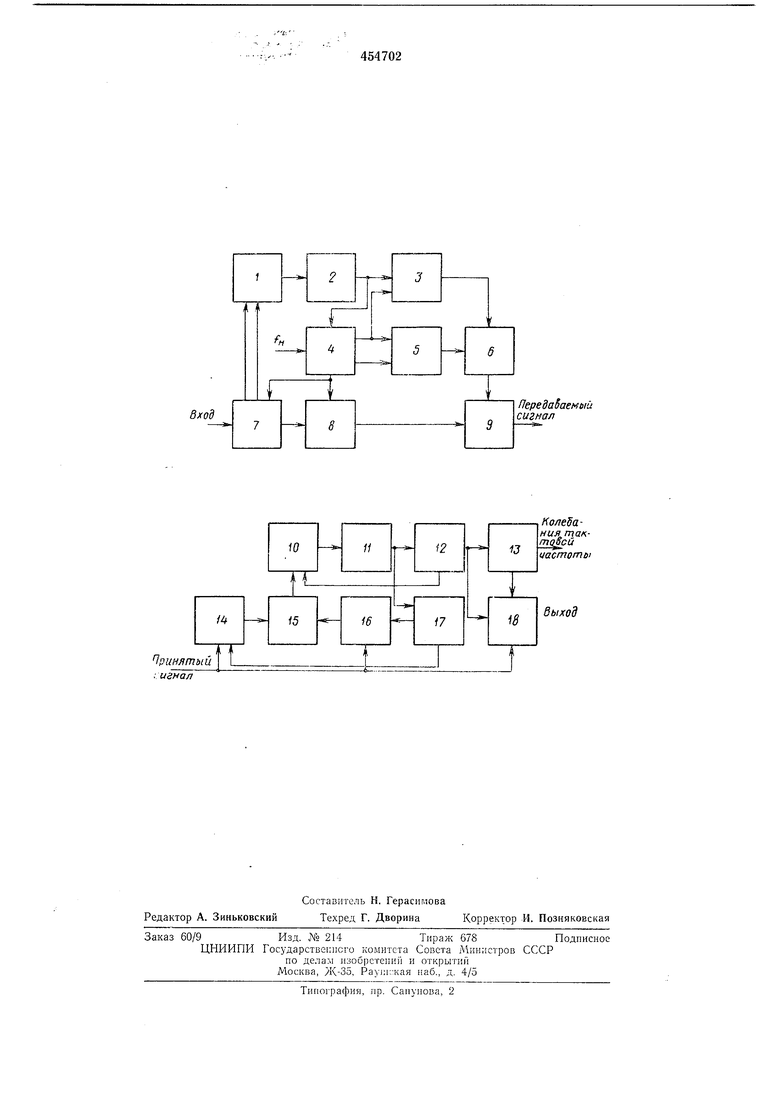

На чертеже приведена блок-схема устройства.

Устройство для синхронного сопряжения содержит на передающей части блок 1 фиксации фазового сдвига, блок 2 однократного изменения периода, блок 3 периодического переключения, распределитель 4, схему «ИЛИ 5, схему «Запрет 6, блок памяти 7, блок 8 формирования дублирующих посылок и блок 9 формирования инверсных посылок, а на приемпой части - приемпик синхронизации 10, блок 11 однократного изменения периода, распределитель 12, блок 13 восстановления тактовой частоты, блок 14 выделения дублирующих посылок, схему «ИЛИ 15, блок 16 выделения инверсных носылок, блок 17 периодического переключения, блок памяти 18.

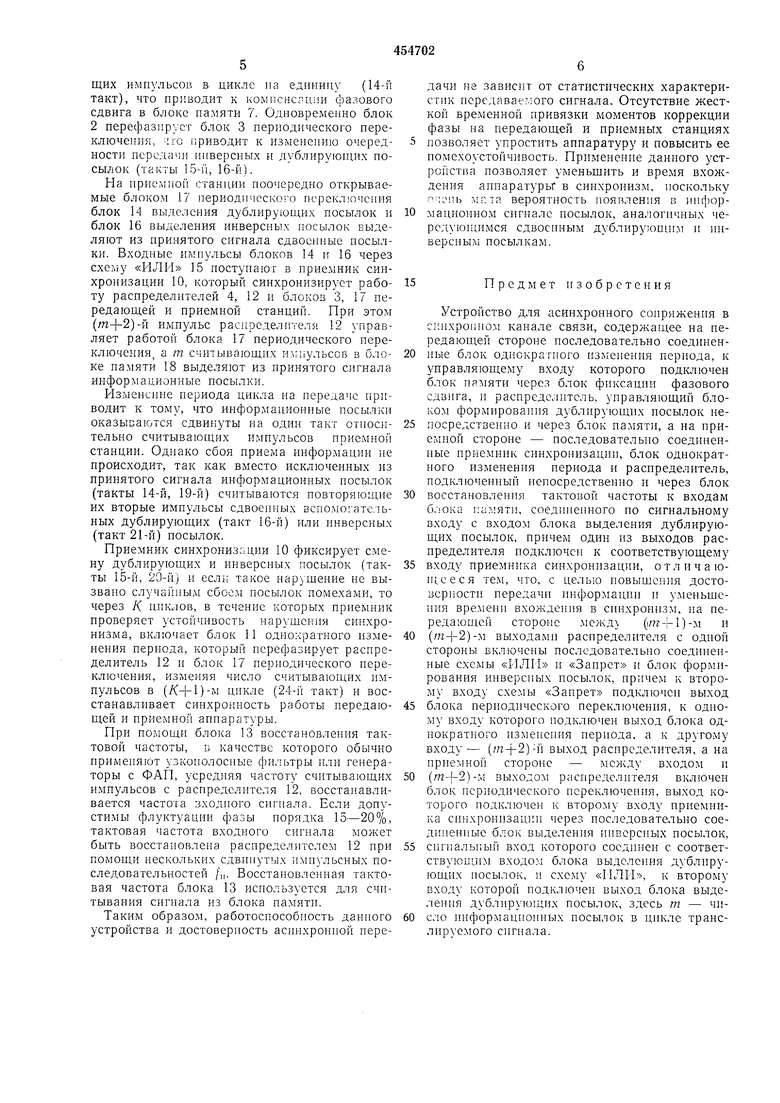

Работа устройства на примере т 3 и ,

где Д - малая величина, выбираемая так, чтобы при всех возможных расстройках частот знак А, определяющий направление изменения фазы импульсной несущей относительно входного сигнала, оставался ностоянным, проиллюстрирована таблицей, где буквой С обозначены тактовые позиции, отведенные в канале связи для асинхронного передаваемого сигнала, а буквами Д и И соответственно обозначены позиции вспомогательных дублирующих

и вспомогательных инверсных носылок.

Таблица

На передающей станции входной сигнал записывается в блок памяти 7 и переписывается распределителем 4 па тактовые позиции канала связи. Выходные импульсы блока памяти растягиваются на весь период считывающих импульсов в блоке 8 формирования дублирующих посылок. На блок 8 от распределителя 4 не поступают (т+1)-й и (т-|-2)-й импульсы, поэтому на месте этих импульсов формируются посылки, дублирующие т-ю информационную посылку. Выходное напряжение блока 8 поступает на блок 9 формирования инверсных посылок, на вход которого через схему «ИЛИ 5 и схему «Запрет 6 поступают (т+1)-й и (т-4-2)-й импульсы распределителя 4. Нри приходе этих импульсов формируются инверсные посылки. Одновременно (т-|-2)-й импульс поступает на блок 3 периодического переключения, который в каждом втором цикле запирает схему «Запрет 6, запрещая прохождение (т-}-)-го и (m-f2)-ro импульсов на блок 9. При отсутствии этих импульсов блок 9 пропускает на выход посылки, формируемые блоком 8.

Таким образом, в передаваемом сигнале после каждых т информациоппых импульсов (такты первый - третий и щестой - восьмой) передаются чередующиеся сдвоенные инверсные (такты четвертый, пятый) и сдвоенные

дублирующие посылки (такты девятый, десятый).

Сдвиг фазы менаду импульсами записи и считывания блока памяти 7 контролируется блоком 1 фиксации фазового сдвига. Когда

этот сдвиг достигает

т+ 2

где Гс - период следования импульсов входного сигнала, включается блок 2 однократного изменения периода, который воздействует на распределитель 4, изменяя число считывающих импульсов в цикле па единицу (14-й такт), что приводит к компснслции фазового сдвига в блоке памяти 7. Одиовременно блок 2 перефазируст блок 3 периодического переключе1 ия, :то приводит к изменению очередности передачи И1верспых и дублирующих посылок (такты IS-ii, 16-й).

На приемной станции поочередно открываемые блоком 17 периодического переключения блок 14 выделения дублирующих посылок и блок 16 выделения инверсных посылок выделяют из принятого сигнала сдвоеппые посылки. Входпые цмпульсы блоков 14 и 16 через схему «Р1ЛИ 15 поступаю г в приемник синхронизации 10, который синхронизирует работу распределителей 4, 12 и блоков 3, 17 передающей и приемной станций. При этом ()-й импульс распределителя 12 управляет работой блока 17 периодического переключения, а т считывающих импульсов в блоке памяти 18 выделяют из принятого сигнала информационные посылки.

Измепенпе периода цикла на передаче приводит к тому, что информаииониые посылки оказываются сдвинуты на один такт относительно считывающих импульсов приемной станции. Одиако сбоя приема информации не происходит, так как вместо исключенных из принятого сигнала информационных посылок (такты 14-й, 19-й) считываются повторяющие их вторые импульсы сдвоенных вспомогательных дублиругощих (такт 16-й) или инверсных (такт 21-й) посылок.

Приемник синхронизации 10 фиксирует смену дублирующих и инверспых посылок (такты 15-й, 20-й) и если такое нарущение не вызвано случай 1ыл1 сбоем посылок помехами, то через /( пиклов, в течение которых приемник проверяет устойчивость нарущения синхронизма, включает блок И однократного изменения периода, который перефазирует распределитель 12 и блок 17 периодического переключения, изменяя число считывающих импульсов в ()-м цикле (24-11 такт) и восстанавливает синхронность работы передающей и приемной аппаратуры.

При помощи блока 13 восстановления тактовой частоты, D качестве которого обычно применяют узкополосные фильтры или генераторы с ФАП, усредняя частоту считывающих импульсов с распределителя 12, восстанавливается частота зходпого сигнала. Если допустимы флуктуации фазы порядка 15-20%, тактовая частота входного сигнала может быть восстаповлепа распределителем 12 при помощи пескольких сдвинутых импульсных последовательностей /. Восстановленная тактовая частота блока 13 используется для считывания сигнала из блока памяти.

Таким образом, работоспособность данного устройства и достоверность асгпьхронной передачи не зависит от статистических характеристик псредаваеглого сигнала. Отсутствие жесткой временной привязки моментов коррекции фазы на передающей и приемных станциях позволяет упростить аппаратуру и повысить ее помехоустойчивость. Примепение данного устройства позволяет уменьшить и время вхождепия аппаратуры в синхронизм, поскольку o:;L4 b v.ia вероятность появления в nnd,)opмационном сигнале посылок, аналогпчных чередующимся СДВОСИНЫМ ДублИру ОПи1М и П1версным посылкам.

Предмет изобретения

15

Устройство для асинхронного сонряження в синхронном канале связи, содержащее иа передающей стороне последовательно соединенные блок одцокрагпого пзменения периода, к управляющему входу которого подключен блок памяти через блок фиксацпи фазового сдвига, и распределитель, управляющий блоком формирования дублирующих посылок непосредственно и через блок памяти, а на приемной стороне - последовательпо соедипеппые приемник синхронизации, блок однократного изменення периода и распределитель, подключенный непосредственно и через блок

восстановления тактовой частоты к входам блока па:.ят11, соединенного по сигнальному входу с входом блока выделения дублирующих посылок, причем один из выходов расиределителя подключен к соответствующему

входу приемника синхронизации, отличаюп,ееся тем, что, с целью повыщспия достоверности передачп информации и уменьщения времени вхождения в спнхропизм, па передающей стороне междх (im-rl)-M н

()-м выходамп распределителя с одной стороны включены последовательно соединенные схемы «ИЛИ и «Запрет и блок формирования ипверспых посылок, причем к второму входу схемы «Запрет подключен выход

блока периодического переключения, к одпому входу которого подключен выход блока однократного изменения нериода, а к другому входу - (т+2)-й выход раснределителя, а на приемной стороне - между входом и

()-м выходом распределптеля включен блок периодического переключенпя, выход которого подключен к второму входу приемника синхронизации через последовательно соединенные блок выделения ппверспых посылок,

спгпальг.ый вход которого соединен с соответствуюпИм входом блока выделения дублирующих носылок, и схе.му «ПЛИ, к второму входу которой подключен выход блока выделения дублирующих посылок, здесь ш - чис.ю ипформационных посылок в цпкле транслируемого спгнала.

Вход

fJepedaSaet tiiu сигнал

Авторы

Даты

1974-12-25—Публикация

1972-06-05—Подача