Изобретение относится к электросвязи и может быть использовано в ап паратуре многоканальной передачи двоичной инфОЕ мации и в оборудовании цифровых сетей связи. Известно устройство асинхронного ввода двоичной информации в цифровой канал связи, содержащее на передающей станции эластичную память, блок фиксации фазового сдвига, распределитель, блок изменения цикла и блок вписывания вспомогательных посылок, а на приемной станции - блок выделения вспомогательных посылок, приемник синхронизации, распределитель, блок изменения цикла, эластичную память и блок восстановления тактовой частоты Щ. Известное устройство характеризуется малой величиной допустимой расстройки тактовых частот входного сиг нала и канала связи. Наиболее близким техническим решением к предлагаемому является устройство асинхронного ввода двоичной информации в цифровой канал санзи, содержащее на передающей стороне блок фиксации фазового сдвига, последовательно соединенные блок эласти ной памяти, первый и второй блоки введения вспомогательных сигналов, а также последовательно соединенные счетчик циклов, блок изменения цикла на один такт и распределитель импуль сов, причем второй и третий выходы блока эластичной памяти соединены с соответствующими входами блока фиксации фазового сдвига, а первый, вто рой, третий и четвертый выходы распределителя импульсов подключены соответственно к первым управляющим входам счетчика циклов, блока эласти ной , первого и второго блоков введения вспомогательных сигналов, а на приемной стороне - блок выделения вспомогательных сигналов, приемник синхронизирующих сигналов, последовательно соединенные блок изменения цикла на один такт, распределитель Импульсов, блок восстановления тактовых импульсов и блок эластичной памяти, причем второй и третий выходы распределителя импульсов соединен соответственно с первым входом приемника синхронизирующих сигналов и вторым входом блока эластичной памяти, информационный вход которого соединен с соответствующим входом блока выделения вспомогательных сигналов f 2 . Недостатком известного устройства является возможность коррекции фазог вых сдвигов, вызванных расстройкой тактовых частот входного сигнала и канала связи, только в одном направлении., что приводит к необходимости введения начальной расстройки, которая должна быть достаточно мала, но превышала суммарную нестабильность этих частот. Кроме того, известное устройство обладает малым диапазоном допустимых расстроек частот. Цель изобретения - обеспечение ввода информации при двустороннем направлении фазовых сдвигов, вызываемых расстройкой тактовых частот входного сигнала и канала связи. Поставленная цель достигается тем, что в устройство асинхронного ввода двоичной информации в цифровой канал связи, содержащее на передающей стороне блок фиксации фазового сдвига, последовательно соединенные блок эластичной памяти, первый и второй блоки введения вспомогательных сигналов, а также последовательно соединенные счетчик циклов, блок изменения цикла на один такт и распределитель импульсов, причем второй и третий выхо,цы блока эластичной памяти соединены с соответствующими входами блока фиксации фазового сдвига, а первый, второй, третий и четвертый выходы распределителя импульсов подключены соответственно к первьм управляющимвходам счетчика циклов, блока эластичной памяти, первого и второго блоков введения вспомогательных сигналов, а на приемной стороне блок выделения вспомогательных сигналов, приемник синхронизируюиу х сигналов, последовательно соединенные блок изменения цикла на один такт, распределитель импульсов,.блок восстановления тактовых импульсов и блок эластичной памяти, причем второй и третий выходы распределителя импульсов соединены соответственно с первым входом приемника синхронизирующих сигналов и вторым входом блока эластичной памяти, информационный вход которого соединен с соответствующим входом блока выделения вспомогательных сигналов, на передающей стороне введены элемент ИЛИ, первый и второй элементы И, причем первый выход блока фиксации фаэйвого сдвига подключен к первым входам элемента ИЛИ и первого элемента И, второй выход блока фиксации фазового сдвига подключен к второму входу элемента ИЛИ и первому входу второго элемента И, выход элемента ИЛИ подключен к второму управлякицему входу счетчика циклов, выход которого соединен с вторыми входами первого и второго элементов И, выходы которых соединены с вторыми управляющими входами соответственно первого, и второго блоков введения вспо- могательных сигналов, а на приемной стороне введены корректор сиг-г, налов синхронизации, блок задержки и блок определения направления фазовой- коррекции, причем выход

блока Наделения вспомогательных сигналов соединен с первыми входами корректора сигналов .синхронизации и блока определения направления фазовой коррекции, выход которого подключен к первому входу блока измененйя цикла на один такт и второму входу корректора сигналов синхронизации третий вход которого соединен с первым выходом блока задержки, второй вход которого подключен к второму входу блрка изменения цикла на один такт, при этом первый и второй выходы приемника синхронизирующих сигналов подключены соответственно к входу блока задержки и второму входу блока определения направления фазовой коррекции.

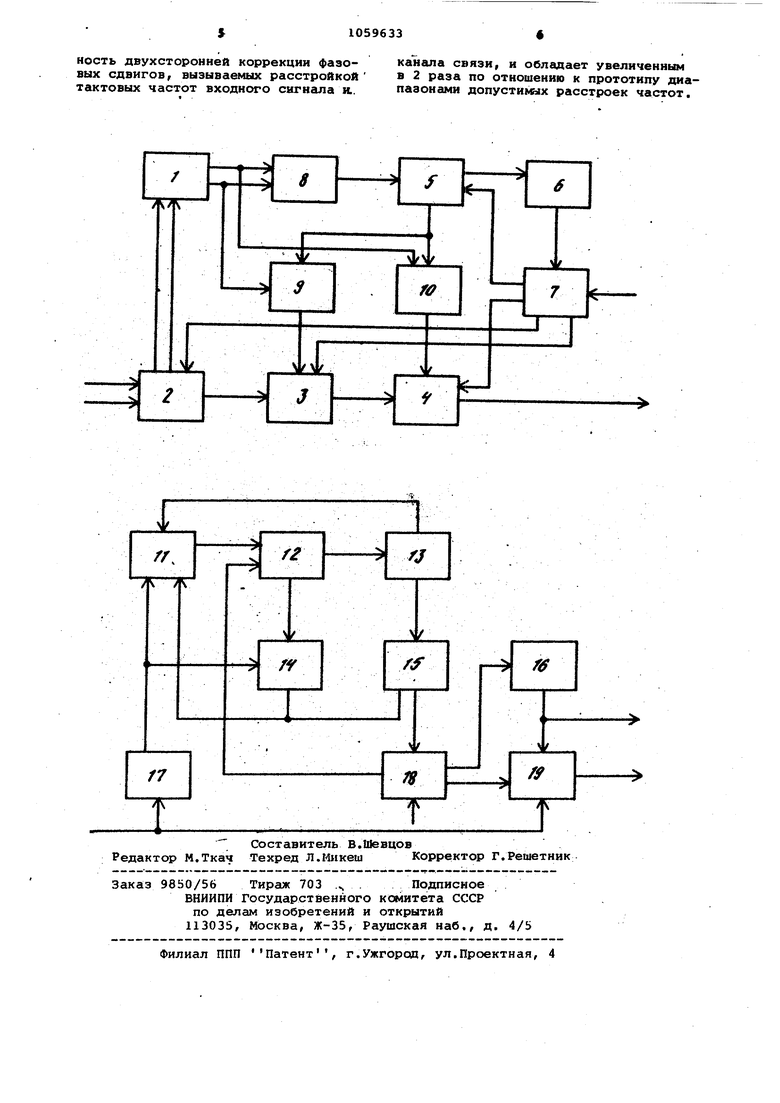

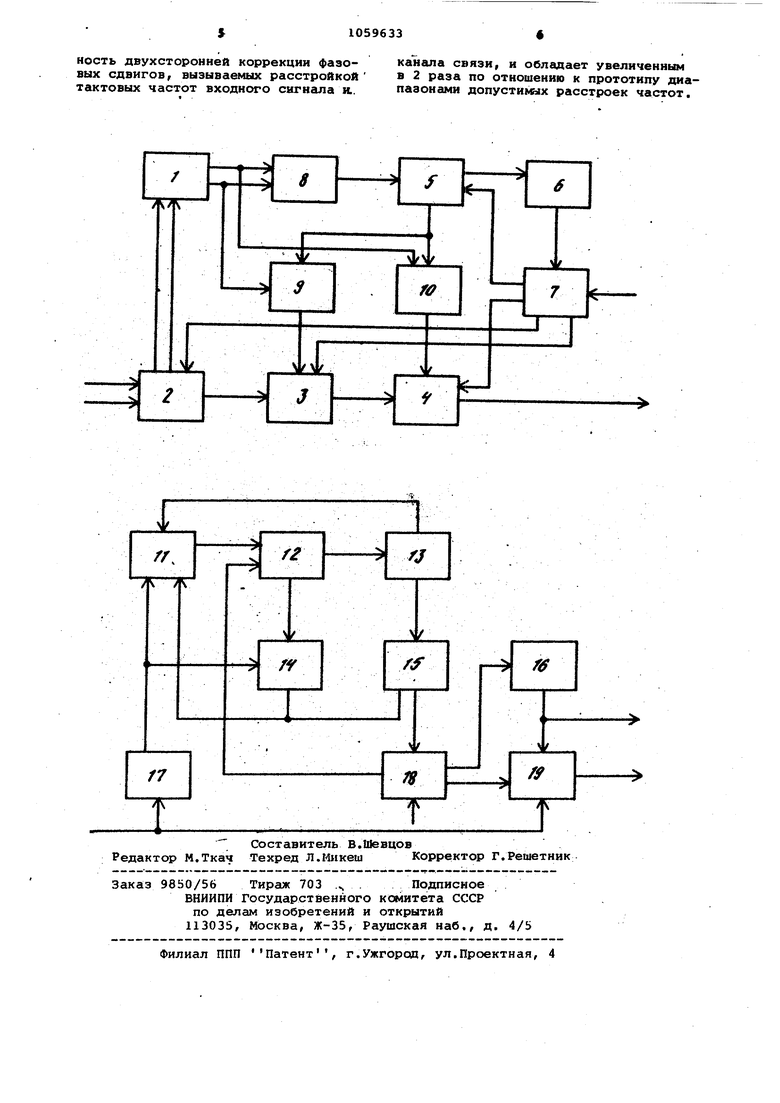

На чертеже показана структурная электрическая схема устройства асинхронного ввода двоичной информации в цифровой канал связи.

Устройство содержит на передаимцей стороне блок 1 фиксации фазового сдвига, блок 2 эластичной памяти, первый блок 3 введения вспомогательных сигналов, второй блок 4 введения вспомогательных сигналов, счетчик 5 циклов, диск 6 изменения цикла на один такт, распределитель 7 импульсов, элемент ИЛИ 8, первый элемент И 9, второй элемент И 10, а на приемной стороне корректор ii сигналов синхронизации, приемник 12-синхронизирующих сигналов, блок 13 задержки, блок 14 определения направле ния фазовой коррекции, блок 15 иэменения цикла на один такт, блок 16 восстановления тактовых импульсов, блок 17 выделения вспомогательных сигналов, распределитель 18 импульсов, блок 19 эластичной памяти.

Устройство работает следующим образом.

На передающей стороне входной сигНсш записывается в блок 2, При считывании этого сигнсша импульсной пос ледовательностью с распределителя 7 формируется цикл передачи, состоящий из m информационных и двух вспомогательных посылок, которые вписываются в передаваемый сигнал блоками 3 и 4. В качестве вспомогательных посылок используются дублирующие и инверсные посылки.

Фазовый сдвиг между импульсами записи и считывания контролируется блоком 1, который следит не только за ег.о величиной, но и за направлением. Когда фазовый сдвиг достигает, порогового значения на одном из выходов блока 1, в зависимости от знака сдвига появляется сигнал, который через элемент ИЛИ 8 включает счетчик 5. При этом счетчик 5 на время п циклов включает первый и второй элементы И 19 и 20, которые

в зависимости от знака фазового сдвига воздействуют на один из блоков (3 ИЛИ 4), который заменяет вписываемую им вспомогательную посьшку ее логической инверсией. В (n+D-M цикле с помощью блока 6, воздействующего на распределитель 7, число информационных посылок в зависимости от направления фазового сдвига однократно увеличивается, или уменьшается на Е тактов, где S - целое число.

На приемной стороне принятый сигнал вписывается в блок 19 с помощью импульсной последовательности с распределителя 10, исключающий из этого сигнала вспомогательные посылки.

Считывание сигнала из блока 19 производится абонентской тактовой частотой, восстановленной блоком 16.

Прииятый сигнал проходит также через блок 17, выделяющий .посылки, зависимые от информационных, и через корректор 11 попадает в приемник 12. Приемник 12 находит вспомогательные посыпки и контролирует их состояние. При обнаружении изменения одной из вспомогательных посылок в k циклах приемник синхронизации вы- дает сигнал,, который задерживается в блоке 13 на tt -.k циклов и воздействует на блок 15. Одновременно блок 1 по изменившей знак вспомогательной посылке определяет направление необходимой фазовой коррекции и в соответствии с его сигналом блок 15 .уменьшает или увеличивает на f тактов длительность формируемого распределителем 18 (п + 1)-го цикла, корректируя фазу тактовой частоты, восстанавливаемой блоком 16. .

Для обеспечения работы при больших расстройках тактовых частот входного сигнала и канала связи на входе приемника 12 включен корректор 11, который до обнаружения приемником 12 сигнала о наличии фазового сдвига подтверждает синхрон|1зм, если вспомогательные посылки в предыдущем и текущем цикле совпадают и содержат не более одной измененной вспомогательной посылки. После обнаружения сигнала о наличии фазового сдвига и до коррекции его в ()-м цикле корректор 11 подтверждает наличие синхронизма, если вспомогательные посылки соответствуют обнаруженному сигналу. Таким образом каждый фазовый сдвиг приводит к поступлению в . приемник, синхронизации лишь одного мпульса,- нз подтверждающего наличие синхронизма..

Использование предлагаемого изобретения позволяет обеспечить возмэжность двухсторонней коррекции фазовых сдвигов, вызываемых расстройкой тактовых частот входного сигнгша к.

канала связи, и обладает увеличенным в 2 раза по отношению к прототипу диапазонами допустим-iix расстроек частот.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для асинхронного сопряжения в синхронном канале связи | 1972 |

|

SU454702A1 |

| СПОСОБ АСИНХРОННОГО ВВОДА ДВОИЧНЫХ СИГНАЛОВ В СИНХРОННЫЙ КАНАЛ СВЯЗИВПТБ.•--fjnn fiic'rir?»:"'^'?!^ ^т;\ а''Ш;*^.; ^^м | 1972 |

|

SU436450A1 |

| Устройство для приема сигналов с относительной фазовой модуляцией | 1990 |

|

SU1714817A1 |

| Регенератор двоичных сигналов | 1979 |

|

SU794752A1 |

| Устройство для асинхронного уплотнения каналов связи с использованием временного разделения сигналов | 1973 |

|

SU479138A1 |

| Устройство поэлементной синхронизации | 1987 |

|

SU1517142A1 |

| Устройство для детектирования многочастотных сигналов | 1987 |

|

SU1427596A1 |

| Система передачи дискретной информации | 1987 |

|

SU1506566A2 |

| Устройство для асинхронного сопряжения цифровых потоков | 1986 |

|

SU1312556A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

УСТРОЙСТВО АСИНХРОННОГО ВВОДА ДВОИЧНОЙ ИНФОРМАЦИИ В Ш1ФРОВОЙ КАНАЛ СВЯЗИ, содержащее на передгиощей стороне блок фиксации фазового сдвига, последовательно соединенные блок эластичной памяти, первый и второй блоки введения вспомогательшдх сигналов, а также последовательно соединенные счетчик циклов/ блок изменения цикла на один такт и распредедитель импульсов, причем второй и третий выходы блока эластичной памяти соединены с соответствующими входами блока фиксации фазового сдвига, а первый, второй, третий и четвертый выходы распре делителя импульсов подключены соответственно к первым управляющим входам счетчика циклов, блока эластичной памяти, первого и второго блоков введения вспомогательных сигналов, а на приемной стороне - бяок выделения вспомогательных сигналов, приемник синхронизирующих сигналов , последовательно соединенные блок изменения цикла на такт, распределитель импульсов блок восстановления тактовых импульсов и блок эластичной памяти, причем второй и третий выходы распределителя импульсов соединены соответственно с первым входом приемника синхронизнрующих сигналов и вторым входом блока эластичной памяти, информационный вход которого соединен с соответствующим входом блока вьаделеIния вспомогательных сигналов, отличающееся тем, что, с целью обеспечения ввода информации при двустороннем направлении фазовых сдвигов, вызываемых расстройкой тактовых час тот входного сигнала и канала связи, на передающей стороне введены элеп- мент ИЛИ, первый и второй элементы и, пртчем первый выход блока фиксации фазового сдвига подключен к первьт входам элемента ИЛИ и первого элемента И, второй выход блока фиксации фазового сдвига подключен к второму входу элемента ИЛИ и первому входу второго, элемента И, выход элемента ИЛИ подключен к второму управляющему входу счетчика циклов, яыход которого g соединен с вторьвгШ входами первого « и второго элементов И, выходы кото- /Л рых соединены с вторыми управляюци- ми входами соответственно первого и f второго блоков введения вспомогательных сигналов, а на приёмной стороне S введены корректор сигналов синхроннэацин, блок задержки и блок определения направления фазовой коррекции, причем выход блока выделения вспсмло:л гательных сигналов соединен с псрвыto ми входами корректора сигналов синхронизации и блока определения наCb правления фазовой коррекции, выход :о которого подключен к первому входу блока изменения цикла на один такт DO и второму входу корректора сигналов синхронизации, третий вход которого соединен с первым выходом блока задержки, вторс вход которого подклю-{ чен к второму входу блока изменения цикла на один TRKT, при этом первый и второй выходы приемника синхроннзирующих сигналов подключены соответственно кВХОДУ блока задержки и второму входу блока определения направления фазовой коррекции.

Авторы

Даты

1983-12-07—Публикация

1982-01-28—Подача