Sx. int. сигнала

К лом

Г

(

(Л

стороне - блок 2 кодирования ЛС, блок 13 выделения ошибок кодирования, Олок 14 накопления ошибок кодирования блок 16 деления частоты, счетн1 1е Т 19 и 20, эл-т 22 сравнения. Формирователи 1 и 2 основного и ДС формируют двоичные информац. сигналы совместимые по логич.уровням с остальными устр-ми передающей части, работа к-рой синхронизируется сигналами С блока 3 синхронизации. Передающей частью формируется линейный сигнал в виде последовательности двухбитных кодовых блоков, в к-ром посылки основного сигнала передаются запретом переходов логич. уровней между битами каждого блока, а посыпки ЛС - запретом переходов на границах после каждого второго кодового блока. ДС кодируется в блоке 4 кодом типа

1Б2В. Это позволяет на приеме уменьшить время вхождения в синхронизм при разделении основного и ДС. Восстановление основного и ДС в приемной части достигается при условии правильной фазировки синхросигналов, действующих на тактовых входах Т 21 и регистра 18, относительно двухбитных кодовых блоков принятого сигнала. Для выйора фазы этих синхросигналов служит схема, включающая блок 13, 14, Т1У и коммутатор 24. 5 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ - ДЕКОДИРОВАНИЯ ДАННЫХ | 2002 |

|

RU2214044C1 |

| Декодер мажоритарного двоичного кода | 1988 |

|

SU1566488A1 |

| УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ДАННЫХ | 2002 |

|

RU2214046C1 |

| Устройство для контроля каналов записи аппарата магнитной записи | 1986 |

|

SU1411818A1 |

| СИСТЕМА ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ИНФОРМАЦИИ КОДОМ ПЕРЕМЕННОЙ ДЛИНЫ | 1996 |

|

RU2123765C1 |

| Устройство для кодирования и декодирования сигналов в системах передачи цифровых данных | 1980 |

|

SU1046959A1 |

| УСТРОЙСТВО КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ РЕЧЕВЫХ СООБЩЕНИЙ | 1994 |

|

RU2085044C1 |

| СПОСОБ ПЕРЕДАЧИ ИНФОРМАЦИИ И СИСТЕМА ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2011 |

|

RU2480840C2 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2002 |

|

RU2239953C2 |

| Биимпульсный регенератор | 1986 |

|

SU1413727A2 |

Изобретение относится к технике оптич. связи. Цель изобретения - повышение достоверности передачи дополнительного сигнала (ДС). На передающей стороне введены блок 4 кодирования ДС, двоичный счетчик 5, триггер (Т) 6, эл-т НЕ 10, на приемной

1

Изобретение относится к технике оптической связи и может быть использовано в цифровых волоконно-оптических системах передачи, в которь х наряду с основным цифровым информационным сигналом по линии свизи необходимо одновременно передавать дополнительный двоичный сигнал, скорость передачи которого меньше чем у основного сигнала.

Целью изобретения является повышение достоверности передачи дополнительного сигнала.

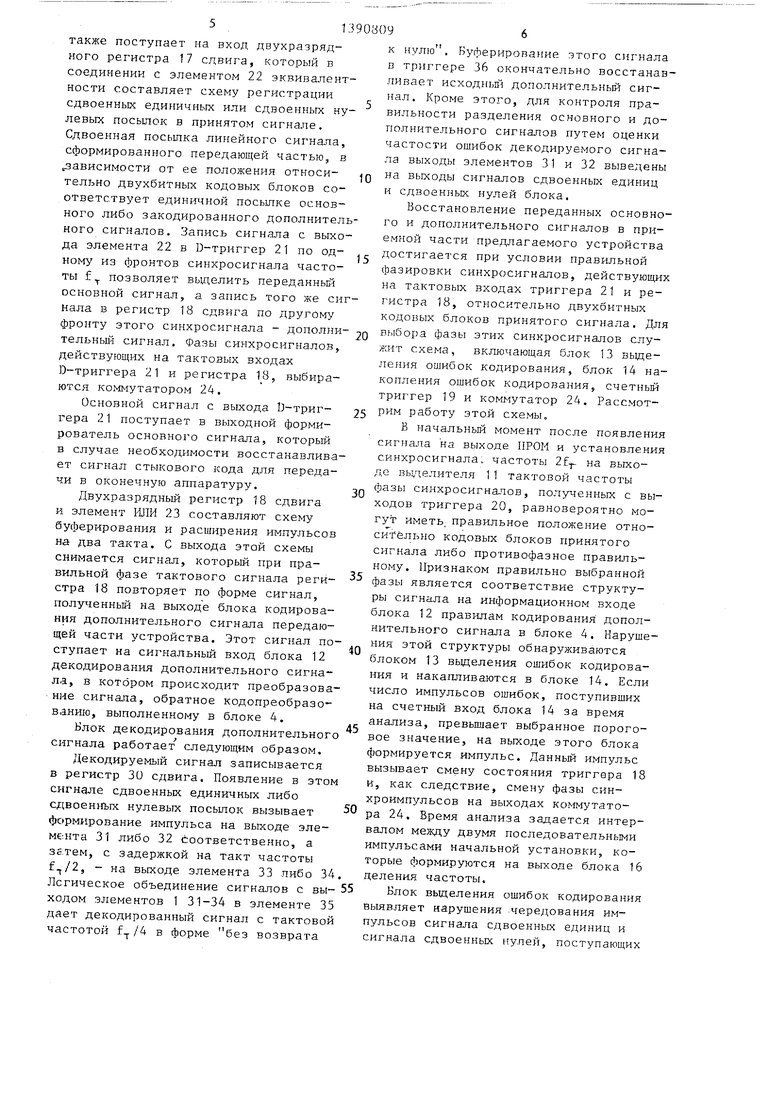

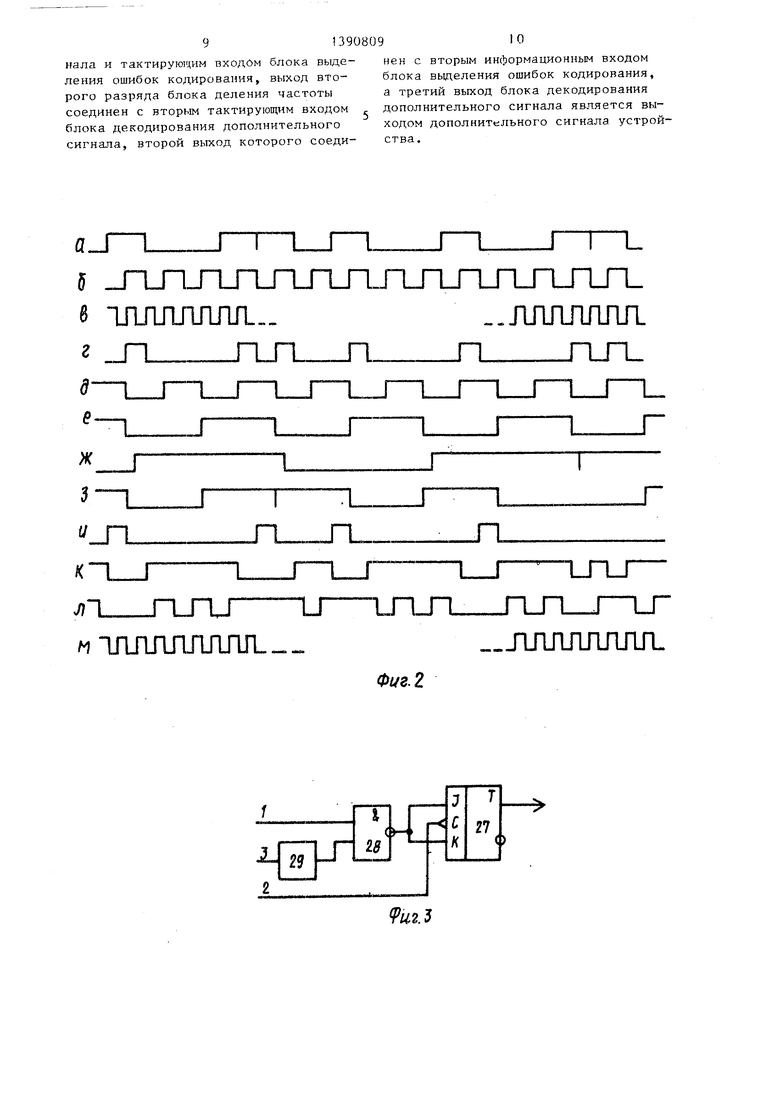

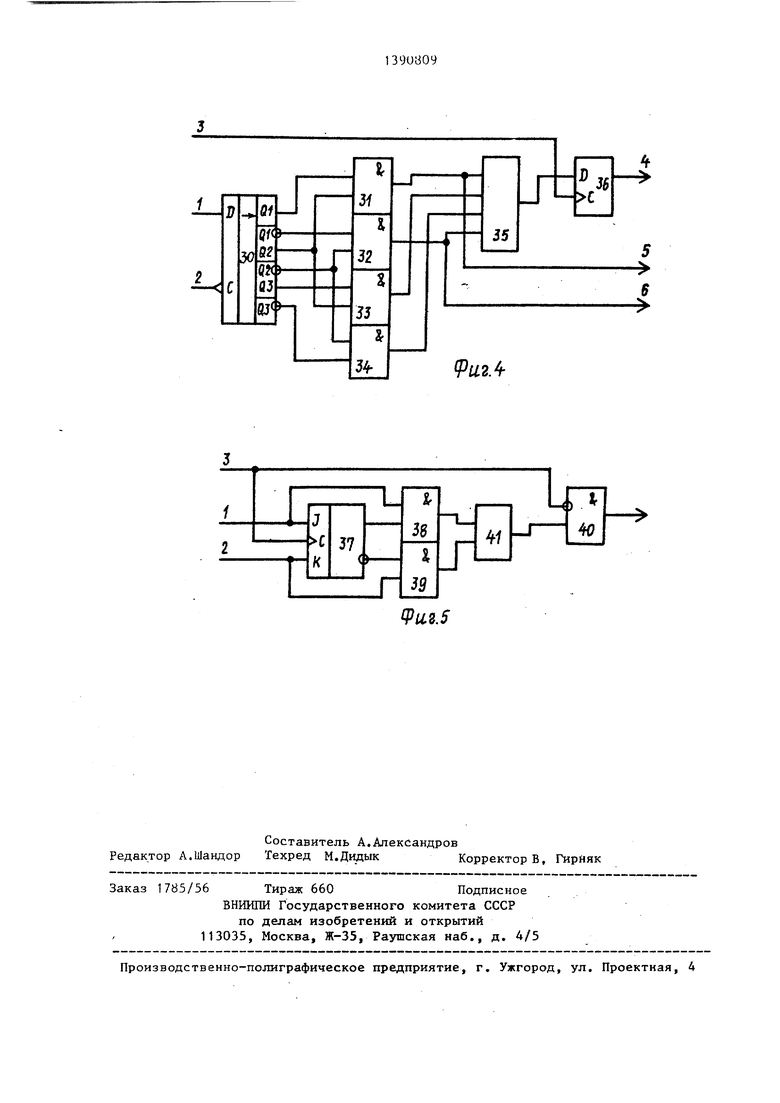

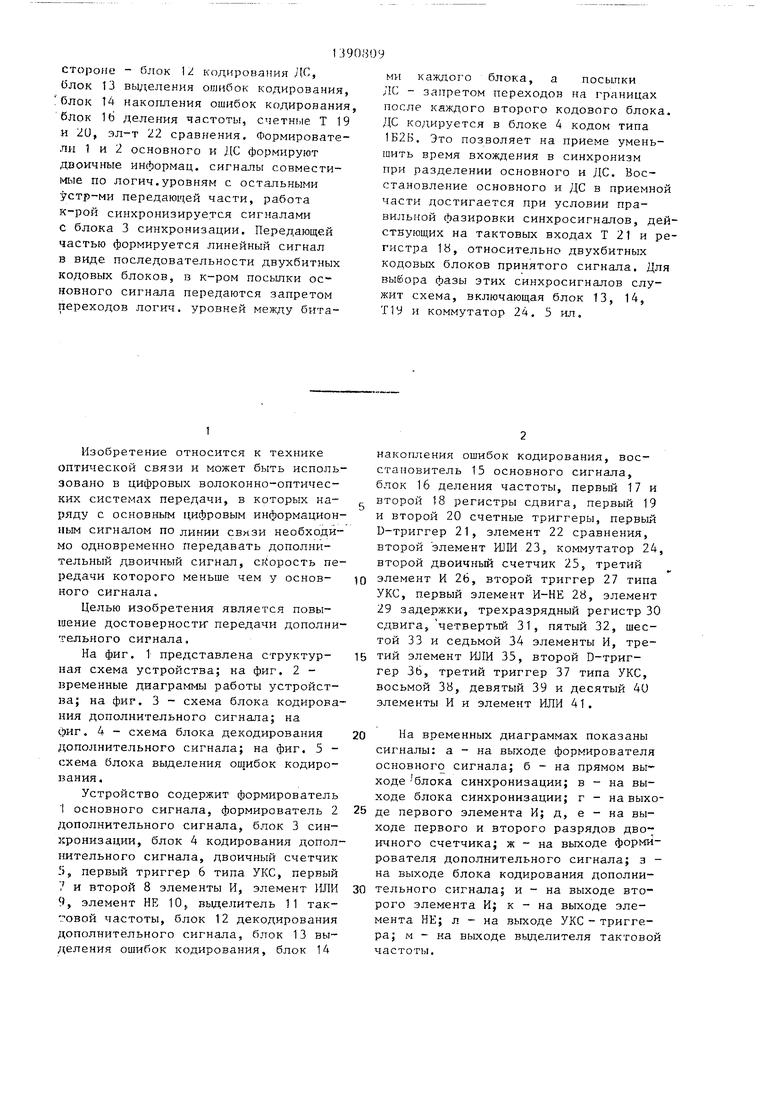

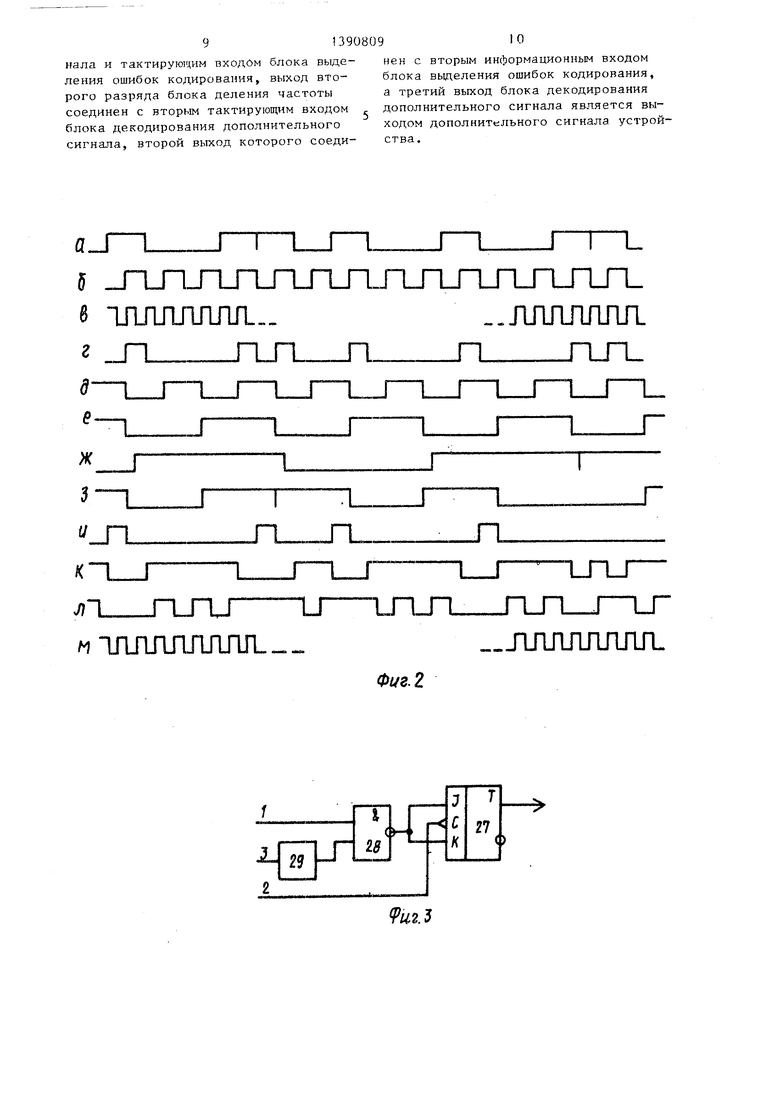

На фиг. 1 представлена структурная схема устройства; на фиг. 2 - временные диаграммы работы устройст- на; на фиг. 3 - схема блока кодирования дополнительного сигнала; на фиг. 4 - схема блока декодирования дополнительного сигнала; на фиг. 5 - схема блока выделения ошибок кодирования.

Устройство содержит формирователь 1 основного сигнала, формирователь 2 дополнительного сигнала, блок 3 синхронизации, блок 4 кодирования дополнительного сигнала, двоичный счетчик ), первый триггер 6 типа УКС, первый 7 и второй 8 элементы И, элемент Ш1И 9, элемент НЕ 10, выделитель 11 так- говой частоты, блок 12 декодирования дополнительного сигнала, блок 13 выделения ошибок кодирования, блок 14

накопления ошибок кодирования, восстановитель 15 основного сигнала, блок 16 деления частоты, первьм 17 и

второй 18 регистры сдвига, первый 19 и второй 20 счетные триггеры, первый D-триггер 21, элемент 22 сравнения, второй элемент HJM 23, коммутатор 24, второй двоичный счетчик 25, третий

элемент И 26, второй триггер 27 типа УКС, первый элемент И-НЕ 28, элемент 29 задержки, трехразрядный регистр 30 сдвига, четвертый 31, пятый 32, шестой 33 и седьмой 34 элементы И, третий элемент ИЛИ 35, второй D-триггер 36, третий триггер 37 типа УКС, восьмой 38, девятый 39 и десятый 40 элементы И и элемент ИЛИ 41.

На временных диаграммах показаны сигналы: а - на выходе формирователя основного сигнала; б - на прямом выходе блока синхронизации; в - на выходе блока синхронизации; г - на выходе первого элемента И; д, е - на выходе первого и второго разрядов двоичного счетчика; ж - на выходе формирователя дополнительного сигнала; з - на выходе блока кодирования дополнительного сигнала; и - на выходе второго элемента И; к - на выходе элемента НЕ; л - на выходе УКС - триггера; м - на выходе выделителя тактовой частоты.

Устройство работает следующим образом.

Основной и дополнительный цифровые сигналы по соответствующим входным линиям поступают в передающую часть устройства, на выходе которой формируется двоичный линейный сигнал, несуп;ий информацию как об основном,

так и о дополнительном сигналах. Этот|о и сигналом частоты /2.

линейный сигнал поступает в волоконно-оптическую линию передачи, включающую передающий оптический модуль (ПОМ), волоконно-оптический тракт и приемный оптический модуль (ПРОМ). С выхода/ 1IPOM линейный сигнал поступает в приемную часть устройства. Здесь происходит разделение и восстановление переданных основного и дополнительного сигналов.

Передаваемый дополнительньй сигнал может быть синхронным или асинхронным по отношению к передаваемому основному сигналу. В первом случае в предлагаемом устройстве тактовая частота дополнительного сигнала может составлять f-j-/aN, где f. - тактовая частота основного сигнала, N - любое целое 0. Скорость передачи асинхронного дополнительного сигнала ограничена допустимой величиной погрешности временного положения фронтов переданных посылок этого сигнала В данном устройстве смещение фронтов посьшок относительно их исходного положения не превышает ±2/f.

Формирователи 1 и 2 основного и дополнительного сигнала формируют на своих выходах двоичные информационные сигналы, совместимые по логическим уровням с остальными устройствами передающей части.

Работа передающей части синхронизируется сигналами с выходом блока 3 синхронизации. На первом и втором выходах этого блока формируются противофазные сигналы тактовой частоты f-, а на третьем выходе - синхросигнал частоты 2f.

Синхросигнал частоты 2f с блока синхронизации поступает на тактовый С-вход триггера 6, у которого входы У и К объединены. На выходе этого триггера формируется цифровой сигнал с максимальной частотой переключения

2f. Переключения триггера 6 не происходит, если во время действия импульса на его тактовом входе на одном из двух входов элемента ИЛИ 9 присутствует единичный сигнал. На первый вход этого элемента поступает основной сигнал, простробированньп1 в элементе 7 синхросигналом частоты f, а на второй вход - дополнительный нал, закодированный в блоке 4 и про- стробированньвЧ в элементе 8 инвертированным синхросигналом частоты f

0

5

0

5

5

0

5

0

Последний получен делением частоты синхросигнала двоичным счетчиком 5. Появление единичной посылки основного сигнала запрещает переход в выходном сигнале триггера 6 во время положительного полутакта, а единичной посылки закодированного дополнительного сигнала во время каждого второго отрицательного полутакта синхросигнала, действующего на прямом выходе блока синхронизации.

Таким образом, передающей ,частью устройства формируется линейный сигнал в виде последовательности двух- битных кодовых блоков, в котором посылки основного сигнала передаются запретом переходов логических уровней между битами каждого блока, а посылки доцолнительного - запретом /lepe- ходов на границах после каждого второго кодового блока. Сформированный сигнал удовлетворяет всем требованиям, предъявляемым к линейным сигна,лам цифровых систем передачи. Так, длительность серий единичных либо нулевых посылок в нем ограничена и не превышает четырех одинаковых посылок подряд-. Это позволяет на прием.ной стороне выделять тактовый синхросигнал и контролировать частоту ошибок приема.

В передающей части устройства дополнительньй сигнал iкодируется в блоке 4 кодом типа 1Б2Б (один быт кодируется двумя битами). Подобное предварительное кодирование дополнительного сигнала вносит в него избыточные признаки, использование которых на приеме позволяет уменьшить время вхождения в синхронизм при разделении основного и дополнительного сигналов. В приемную часть устройства по линии принятого сигнала поступает сигнал с выхода ПРОМ. В выделителе 11 тактовой частоты из него формируется

синхросигнал частоты 2f, из которого счетным триггером 20 в свою очередь

формируются два противофазных синхросигнала частот fт. Принятый сигнал

также поступает на вход двухразряд- ного регистра 17 сдвига, который в соединении с элементом 22 эквивалентности составляет схему регистрации сдвоенных единичных или сдвоенных нулевых посылок в принятом сигнале. Сдвоенная посьшка линейного сигнала, сформированного передающей частью, в „зависимости от ее положения относительно двухбитньк кодовых блоков соответствует единичной посылке основного либо закодированного дополнительного сигналов. Запись сигнала с выхо1390а()96

к нулю, Вуферирование этого сигнала в триггере 36 окончательно восстанавливает исходньш дополнительньй сигнал. Кроме этого, для контроля правильности разделения основного и дополнительного сигналов путем оценки частости ошибок декодируемого сигнала выходы элементов 31 и 32 выведены д на выходы сигналов сдвоенных единиц и сдвоенньк нулей блока.

Восстановление переданных основного и дополнительного сигналов в при- BMHoii части предлагаемого устройства

да элемента 22 в D-триггер 21 по од- , достигается при условии правильной

ному из фронтов синхросигнала частоты f позволяет выделитр переданньй основной сигнал, а запись того же сигнала в регистр 18 сдвига по другому

фазировки синхросигналов, действующ на тактовых входах триггера 21 и ре гистра 18, относительно двухбитных кодовых блоков принятого сигнала. Д

фронту этого синхросигнала - дополни- 2Q выбора фазы этих синхросигналов слутельный сигнал. Фазы синхросигналов, действу ощих на тактовых входах 1)-триггера 21 и регистра , выбираются коммутатором 24.

Основной сигнал с выхода D-триг- гера 21 поступает в выходной формирователь основного сигнала, который в случае необходимости восстанавливает сигнал стыкового кода для передачи в оконечную аппаратуру.

Двухразрядный регистр 18 сдвига и элемент ИЛИ 23 составляют схему буферирования и расширения импульсов на два такта. С выхода этой схемы снимается сигнал, который при правильной фазе тактового сигнала регистра 18 повторяет по форме сигнал, полученньм на выходе блока кодирования дополнительного сигнала передающей части устройства. Этот сигнал поступает на сигнальный вход блока 12 декодирования дополнительного сигнала, в котором происходит преобразование сигнала, обратное кодопреобразо - ванию, выполненному в блоке 4.

Клок декодирования дополнительног сигнала работает следующим образом.

Декодируемый сигнал записывается в регистр 30 сдвига. Появление в это срггнале сдвоенных единичных либо сдвоениых нулевых посылок вызывает формирование импульса на выходе эле- ме:нта 31 либо 32 соответственно, а

, - на выходе элемента 33 либо 34. Логическое объединение сигналов с вы- 55 ходом элементов 1 31-34 в элементе 35 дает декодированный сигнал с тактовой частотой в форме без возврата

фазировки синхросигналов, действующих на тактовых входах триггера 21 и регистра 18, относительно двухбитных кодовых блоков принятого сигнала. Для

5

0

5

0

5

0

5

жит схема, включающая блок 13 выделения ошибок кодирования, блок 14 накопления ошибок кодирования, счетньй триггер 19 и коммутатор 24. Рассмотрим работу этой схемы„

В начальньй момент после появления сигнала на выходе ИРОМ и установления синхросигналаU частоты 2f на выходе вы,ч;елителя 1 1 тактовой частоты фазы синхросигналов, полученных с выходов триггера 20, равновероятно могут иметь, правильное положение относительно кодовых блоков принятого сигнала либо противофазное правиль- Hot-iy. Признаком правильно выбранной фазы является соответствие структуры сигнала на информационном входе блока 12 правилам кодирования дополнительного сигнала в блоке 4. Нарушения этой структуры обнаруживаются блоком 13 выделения ошибок кодирования и накапливаются в блоке 14. Если число импульсов ошибок, поступивших на счетный вход блока 14 за время анализа, превышает выбранное пороговое значение, на выходе этого блока формируется импульс. Данньм импульс вызывает смену состояния триггера 18 и, как следствие, смену фазы синхроимпульсов на выходах коммутатора 24. Время анализа задается интервалом между двумя последовательными импульсами начальной установки, которые формируются на выходе блока 16 деления частоты.

Блок выделения ошибок кодирования выявляет нарушения чередования импульсов сигнала сдвоенных единиц и сигнала сдвоенных нулей, поступающих

7

на информационные входы блока 13 с соответствуюцр х выходов блока 12 декодирования. Нарушения в структуре кодированного сигнала, действующего на информационном входе блока 12, вьг- зывают нарушения чередования этих импульсов, которое в блоке 13 вызывает появление единичного уровня сигнала на выходе элемента 41. Сигнал с выхода элемента 41 после стробирования в элементе 40 импульсами синхросигнала частоты f-f/2 поступает на вьгход блока.

Ф

ормула изобретения Устройство для передачи и приема основного и дополнительного сигналов по цифровой волоконно-оптической линии связи, содержащее на передающей стороне последовательно соединенные формирователь основного сигнала, первый элемент И и первый элемент ИЛИ, формирователь дополнительного сигнала, блок синхронизации и второй элемент И, причем вход формирователя основного сигнала является входом основного сигнала устройства, вход формирователя дополнительного сигнала является входом дополнительного сигнала устройства, вход блока синхронизации является входом синхронизации устройства, прямой выход блока синхронизации соединен с вторым входом первого элемента И, инверсньш выход блока синхронизации соединен с первым входом второго элемента И, а на приемной стороне - второй элемент ИЛИ, восстановитель основного сигнала и последовательно соединенные вьщели- тель тактовой частоты и первый регистр сдвига, причем выход восстановителя основного сигнала является выходом основного сигнала устройства а вход вьщелителя тактовой частоты соединен с информационным входом ре гнстра и является входом приемника, отлич ающе еся тем, что, с целью повышения достоверности передачи дополнительного сигнала, в него введены на передающей стороне блок кодирования дополнительного сигнала, двоичньй счетчик, первый триггер и элемент НЕ, причем инверсньй выход блока синхронизации соединен с входом двоичного счетчика, вьгход первого разряда которого соединен с первым входом тактирования блока кодирования дополнительного сигнала и с вторым

.-

JQ а098

входом второго элемента И, вьпсод второго разряда двоичного счетчика соединен с вторым входом тактирования блока кодирования дополнительного сигнала, вь.ход формирователя дополнительного сигнала соединен с информационным входом блока кодирования до- JQ 15

20

25

30

35 50 55

40

45

соединен с третьим входом второго элемента И, выход которого соединен с вторым входом первого элемента ИЛИ, выход которого соединен с входом элемента НЕ, выход которого соединен с входами Y и К первого триггера, выход которого является выходом передатчика, вьгход удвоенной тактовой частоты блока синхронизации соединен с входом синхронизации первого триггера, а на приемной стороне пос11едо- вательно соединенные блок декодирования дополнительного сигнала, блок выделения ошибок кодирования, блок накопления ошибок кодирования и первый счетньй триггер, выход которого соединен с управляющим входом коммутато ра, блок деления .частоты, второй счетный триггер и элемент сравнения, вькод которого соединен с информационными входами D-триггера и второго регистра сдвига, причем выходы первого и второго разряда первого реги- ,стра сдвига соединены соответственно с первым и вторым входами элемента сравнения, выходы первого и второго разряда второго регистра сдвига соединены соответственно с первым и вторым входами второго элемента ИЛИ, вьгход которого соединен с информационным входом блока декодирования дополнительного сигнал а,- выход вьщелителя тактовой частоты соединен с входом второго счетного триггера, прямой и инверсный выходы которого соединены соответственно с первым и вторым информационными входами коммутатора, прямой выход которого соединен с входом синхронизации D-триггера, выход которого соединен с входом выходного формирователя основного сигнала, инверсный выход коммутатора соединен . с входом синхронизации второго регистра сдвига и с входом блока деления частоты, выход которого соединен с входом синхронизации блока накопления ошибок кодирования, выход первого разряда блока деления частоты соединен с первым тактирующим входом блока декодирования дополнительного сиг9139080910

нала и тактирующим входим блока вьще- нен с вторым информационным входом

ления ошибок кодирования, выход второго разряда блока деления частоты соединен с вторым тактирующим входом блока декодирования дополнительного сигнала, второй выход которого соедиблока выделения ошибок кодирования а третий выход блока декодирования дополнительного сигнала является в ходом дополнительного сигнала устр ства.

5JHJnJ-ljnjarbn.rLriJnJlJaJ

6ТШ1Ш ШЛ.„„ ЛЛШ1ЛШ1 г jnП П П ПП П

мЛЛЛПЛЛЯПЛ.нен с вторым информационным входом

блока выделения ошибок кодирования, а третий выход блока декодирования дополнительного сигнала является выходом дополнительного сигнала устройства.

J L

..JlTLfinJinJirL

0if8.2

.5

Риъ.

| СВАЯ И СПОСОБ ЕЕ ВОЗВЕДЕНИЯ | 2013 |

|

RU2535556C1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1988-04-23—Публикация

1986-12-30—Подача