1

Изобретение относится к области телеуправления, в частности к технике телеуправления рассредоточенными объектами.

Известны устройства для приема команд управления при многоступенчатой передаче командных признаков, основанные на обработке последних по методу логической конъюнкции либо суммированием их по модулю 2.

Однако в известных устройствах при возникновении любой одиночной ошибки имеет место защитный отказ (неисполнение команды).

Цель изобретения - повышение досто1верности приема команд в асимметричных каналах связи с ложными появлениями импульсов за счет исправления одиночных ошибок при приеме команд с обработкой командных признаков суммированием их по модулю 2.

Цель достигается тем, что в предлагаемое устройство введены дополнительные группы схем «И, группы схем «ИЛИ, дополнительный регистр, распределитель импульсов, выполненный в виде пересчетной схемы, вход которой через схему «И подключен к выходам генератора и триггера, а выходы - к соответствующим входам матричной схемы, ждущие одновибраторы, дифференцирующие цепи, триггеры и схемы «И, причем первые входы перовой группы схем «И подключены к соответствующим входны.м шинам приема командных признаков, первые входы второй группы схем «И соединены с соответствующими входными щипами приема контрольного признака, выход схемы «И дешифратора адреса .подключен к первому входу триггера дешифратора адреса и через вторую дифференцирующую цепь к соответствующему входу первого регистра, второй вход триггера дешифратора адреса соединен с выходом первой дифференцирующей цепи, выход триггера дешифратора адреса подключен к вторым входам первой группы схем «И и через последовательно соединенные первые

g ждущий одновибратор и дифференцирующую цепь к первому .входу триггера распределителя импульсов, последний выход которого подключен к сбросовому входу своего триггера, к сбросовому входу первого триггера и через последовательно соединенные второй ждущий

0 одновибратор и третью дифференцирующую цепь - к соответствующим входам первого триггера, третьего ждущего одновибратора, к первому входу второго триггера и к соответствующихМ входам третьей группы схем «И.

Выход третьего ждущего одновибратора

через четвертую дифференцирующую цепь

подключен к второму входу второго триггера

и к соответствующим входам первого и до0 полнительного регистров, выход первого

триггера подключен к вторым входам второй группы схем «И, выходы первой группы схем «И через первые входы пер1вой группы схем «ИЛИ подключены .к первому регистру, вторые входы первой группы схем «ИЛИ подключены к соответствующим выходам третьей группы схем «И, выходы второй группы схем «И.

Через вторую группу схем «ИЛИ подключены к соответствующим 1входам дополнительного регистра, выходы которого подключены к соответствующим входам третьей группы схем «И, выходы матричной схемы распределителя импульсов через четвертую группу схем «И подключены к соотгветствующим входам второй группы схем «ИЛИ.

Работает предлагаемое устройство в общем случае следующим образом.

Принимаемым на первой ступени избираиия в виде двоичного параллельного (п-г) разрядного слова веса W адресным признаком открывают п-г схем «И первой группы, в результате чего осуществляется запись в первый регистр адресного признака (поскольку длительность сигналов значительно превышает время срабатывания дешифратора адреса) и разрешается прием командных признаков второй и третьей ступеней избирания в виде слов двоичного параллельного (п-г)-разрядного кода веса W, которые также записывают в параллельный регистр.

Принимаемые избирающие признаки (В первом регистре последовательно суммируются по модулю 2, образуя в итоге командное слово того же веса W. По окончании действия на входных шинах сигналов командного признака третьей ступени избирания разрешают прием на четвертой ступени контрольного слова в виде комбинации параллельного г-разрядного слова веса W, соответствующего переданной команде, которое записывают в триггеры дополнительного регистра.

Одновременно для записанного в первом регистре командного слова суммированием по модулю 2 определенных разрядов этого слова вычисляют соответствующее ему контрольное слово, которое с целью выявления комбинации ошибки сммируют по модулю 2 с контрольным словом, принятым на четвертой ступени.

Если в результате суммирования образуется нулевое слово, то это означает отсутствие ошибки. Если же в итоге суммирования образуется ненулевое слово, то с помощью его единичных разрядов определяют номер разряда командного слова, который должен быть исправлен, и подают сигнал коррекции на вход соответствующего триггера первого регистра.

По окончании операции обнаружения и исправления ошибки открывают входы схем «И дешифратора команд, разрешая декодироваеие принятой команды.

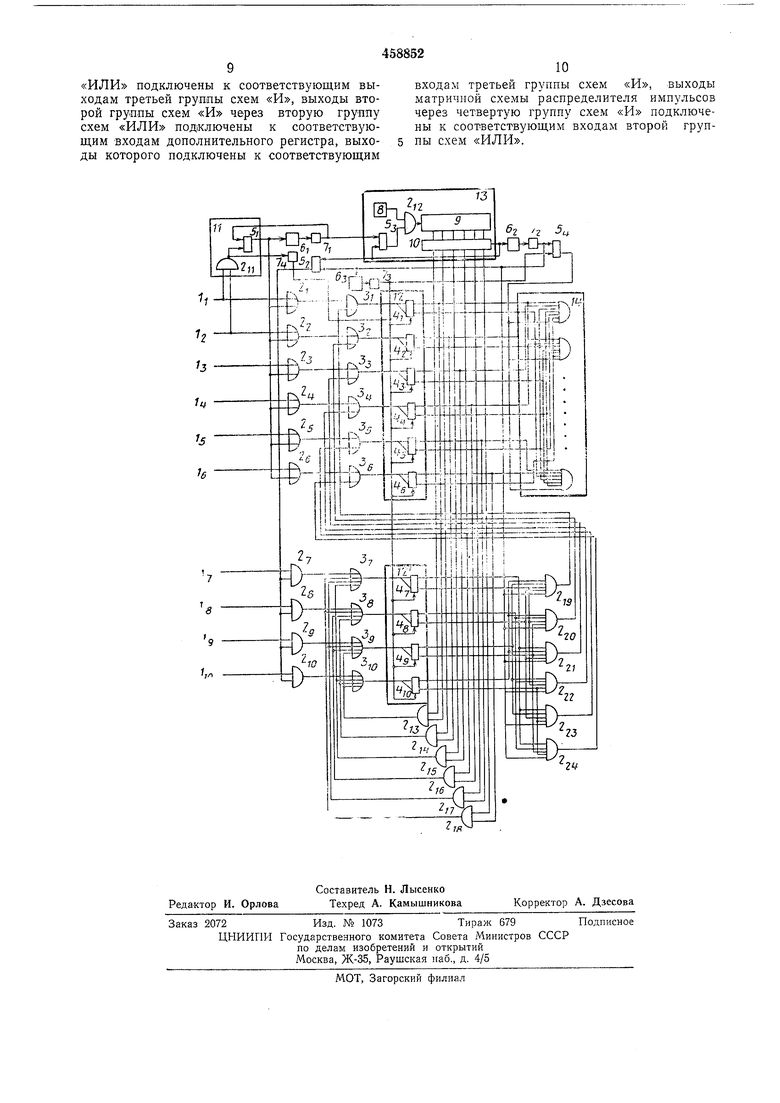

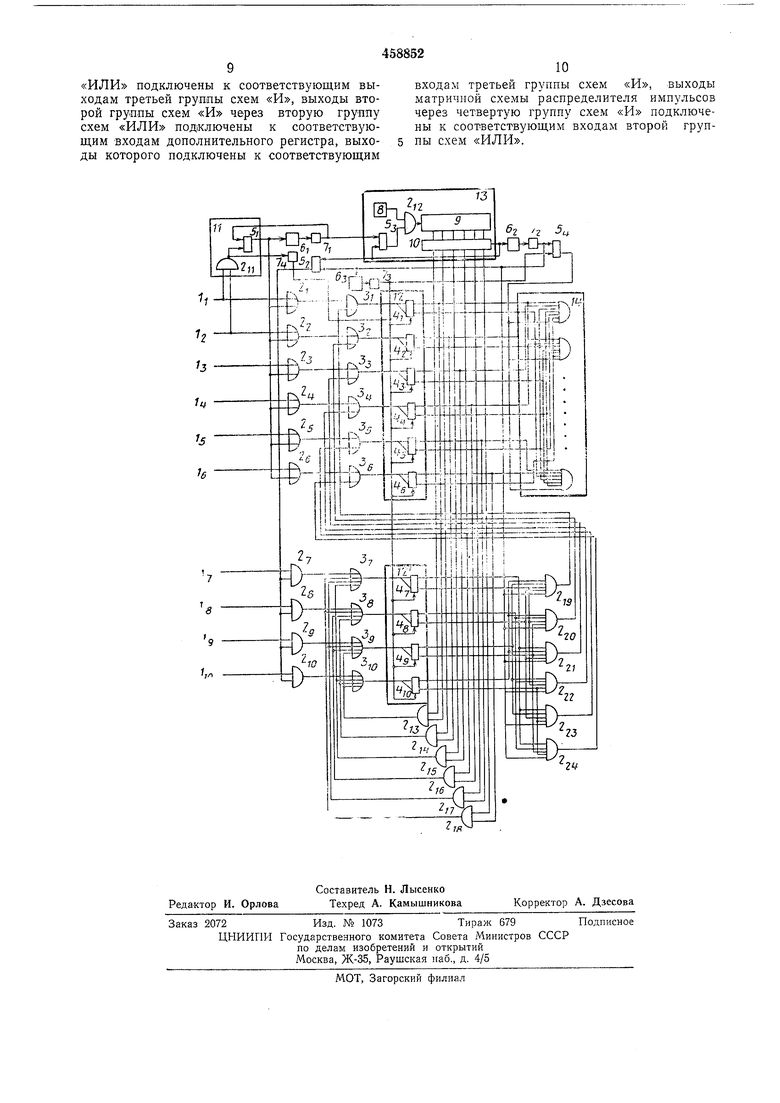

Блок-схема устройства применительно к

приему команд в виде сигналов - слов десятиразрядного параллельного кода, в котором 6 разрядов (п-г) используются для кодирования в весе командных признаков, а 4 разряда (г) используются для кодирования в весе W-2 проверочного слова, приведена на чертеже.

Устройство содержит входные шины Ь--lio, первую группу схем «И , вторую группу схем «И , схемы «И 2и-2i2, четвертую группу схем «И 2i3-2i8, третью группу схем «И 2 9-224, первую группу схем «ИЛИ , вторую группу схем «ИЛИ , триггеры со

счетным входом, триггеры с раздельными входами, ждущие одновибраторы 6i-63, дифференцирующие цепи 7i-7, генератор импульсов 8, пересчетную схему 9, матричную схему 10, дешифратор адреса 11, регистры 12 и 12 соответственно на триггерах 4i-4б и , распределитель импульсов 13, дещифратор команд 14.

Выход дещифратора адреса 11, состоящего из схемы «И 2ii и триггера 5i, непосредственно соединен с одними входами первой группы схем «И 2i-2б, а через первые ждущий одновибратор 6i и дифференцирующую цепь соединен со сбросовым входом триггера 5 и с входом распределителя импульсов 13. Другие входы первой группысхем «И связаны с входными шинами, а выходы через первую группу схем «ИЛИ соединены с входами счетных триггеров регистра 12, выходы которых соединены с дешифратором команд и с одним из входов четвертой группы схем «И 2i3-2i8. Другие входы четвертой группы схем «И 2i3-2i8 соединены с соответствующими выходами распределителя импульсов 13, а выходы через вторую группу схем «ИЛИ 3т-Зю соединены со счетными входами триггеров дополнительного регистра 12, выходы которых, в свою очередь, через третью группу схем «И 2i9-224 и первую группу схем

«ИЛИ 3i-Зб соединены со счетными входами триггеров 4)-4б регистра 12.

Выход распределителя импульсов 13 соединен со входом триггера 62, выход которого соединен с одними входами второй группы

схем «И , другие входы которых соединены с входными шинами, а выходы через вторую группу схем «ИЛИ соединены с входами триггеров .

Выходраспределителя импульсов 13 соединен также с ждущим одновибратором ба, выход которого через дифференцирующую цепь 72 соединен с общими входами третьей группы схем «И 2i9-224, с входом ждущего одновибратора 6з, со сбросовым входом триггера 52 и входом триггера 64, выход которого соединен с входом дешифратора команд 14.

Выход ждущего одновИбратора 6з через дифференцирующую цепь 7з соединен со сбросовыми входами счетных триггерО в регистра 12. Схема работает следующим образом.

Поступление в момент времени ti на входные шины li, la адреса в виде сигна.та первой ступени избирания 110000 возбуждает выход схемы «И 2п дешифратора адреса И и перебрасывает триггер 5i в единичное состояние, а триггеры 64, 4i-4io через дифференцирующую цепь 7з устанавливает в нулевое состояние. Сигнал с единичного выхода триггера 5i запускает ждущий одновибратор 6i и одновременно открывает входы схем «И 2i-2б. Сигнал адреса через схемы «И 2ь 22 и схемы «Р1ЛИ Зь 82 перебрасывает в единичное состояние триггеры 4i, 42 регистра 12. Таким образом, после поступления адреса в регистре оказывается записанным слово 110000.

Пусть затем в момент t на входные шины li, Ь поступает командный признак второй ступени избирания в виде сигнала 101000. Через входные схемы «И 2i, 2з и схемы «ИЛИ Зь Зз сигнал поступает на счетные входы триггеров 4, 4$, которые производят операцию сложения по модулю 2 адресного слова и поступившего слова командного признака. В результате триггер 4. переходит в нулевое состояние, триггер 4$ - в единичное состояние, триггер 42 остается в единичном состоянии и в регистре оказывается записанным слово 110000 + 101000 - - 011 000.

Пусть далее в момент t на входные шины Ь, 1б поступает командный признак третьей ступени избирания в виде сигнала 010001. Через схемы «И 22, 2б и схемы «ИЛИ 32, Зб сигнал поступает на счетные входы триггеров 42, 4$, которые производят операцию сложения по модулю 2 записанного в регистре слова 011000 и поступившего слова 010001. В результате триггер 42 переходит в нулевое состояние, триггер 4б - в единичйое состояние и в регистр записывается слово 011000 + 010001 001001.

В момент времени t4, по окончании действия на входных шинах сигналов командного признака третьей ступени избирания, возвращается в исходное состояние ждущий одновибратор 6i. Сигнал с выхода однавибратора дифференцируется цепью 7) и в момент времени /4 воздействует на входы триггеров 5i и 5з. Триггер 5i возвращается в исходное состояние и закрывает входные схемы «И 2)-2б первой группы. Триггер 5з, срабатывая, открывает с.хему «И 2i2, которая пропускает импульсную последовательность, создаваемую генератором 8, на вход пересчетной схемы 9. Двоичные импульсные сигналы с выхода пересчетной схемы поступают на матричную схему 10, образующую последовательность семи импульсов, шесть из которых используются для поочередного открывания с.хем «И четвертой группы.

В момент /5 поступления опрашивающего импульса единичный сигнал с выхода триггера 4з через схему «И и схемы «ИЛИ Зт, Зю проходит на триггеры 4f и 4io, записывая в них комбинацию 1001. Единичный си1нал с выхода триггера 4б в момент t поступления оиращивающего импульса через схему «И 2is и схемы «ИЛИ 3, Зз проходит на триггеры 4, 4д, записывая в них слово 1100. В результате суммирования по модулю 2 к моменту tj поступления на входные шины сигналов контрольного слова в триггера х -48 и 4io будет записано слово 1001 +

+ 1100 0101.

В момент времени tj седьмым импульсом с выхода распределителя 13 осуществляется сброс триггера 5з, в результате чего закрывается схема «И 2i2 и прекращается выдача

с распределителя 13 опрашивающих импульсов. Одновременно взводится триггер 5 и запускается ждущий одновибратор ба- Сигнал с выхода триггера Sj открывает вторую группу схем «И , разрешая прием контрольного слова 0101, которое через схемы «ИЛИ За, 3|о поступает в триггеры 48 и 4io.

Поскольку в триггерах 48 и 4io ранее было записано слово 0101, то в результате приема контрольного слова 0101 в момент /7 они перейдут в нулевое состояние. В итоге будет записа-но слово 0101 + 0101 0000, что свидетельствует об отсутствии ощибки в принятой команде.

В момент времени ta возвратится в исходное состояние ждущий одноввбратор бг. Сигнал с его выхода дифференцируется и в мо.мент /8 сбрасывает триггер 62 в исходное состояние. При этом закрываются входы второй группы схем «И и выдается разрешающий сигнал на входы третьей группы схем «И 2i9-224. Одновременно запускается ждущий одновибратор 6з и взводится триггер 54, с выхода которого на дешифратор команд 14 поступает сигнал, разрешающий декодирование принятой команды. Ждущий одновибратор 6з возвращается в исходное состояние в момент 9- Сигнал с его выхода дифференцируется и подается на триггер 64, возвращая его в исходное состояние, а также на триггеры , устанавливая их в нулевое состояние.

Рассмотрим теперь случай появления одиночной ошибки. Пусть «а третьей ступени избирания вместо слова 010001 принято слово

010101, т. е. появляется ложный единичный разряд на четвертой позиции (при счете слова направо). В регистре 12 при этом записано слово 001 101, т. е. в единичном состоянии находятся триггеры 4з, 44, 4б. При считывании

этого слова с распределителя 13 импульсами через схемы «И 2i5, 2i6, 2i8 и схемы«ИЛИ ЗУ, Зд, Зю в триггеры 49 и записывается соответствующая ему контрольная комбинация ООП.

При суммировании ее с принимаемым на четвертой ступени контрольным словом 0101 образуется комбинация ошибки 001 +0101 0110, т. е. триггеры 48, 40 оказываются а единичном состоянии. Комбинация ошибки

декодируется схемой «И 222, с выхода коТОрСй да тупает сигнал на триггер 44, возвраодая его в нулевое состояние. В результате в регистре 12 оказывается записанным слово 001001, соответствующее переданной команде.

Таким образом осуществляется исправление одиночной ошибки, появляющейся на избирающей ступени командной серии.

Рассмотрим далее случай появления ошибки не только на избирающей, но и на К:е тр9лшой -стуш-ни. Пусть в регистре 12 суммпроваийя слов .из-йирающих признаков вместо дамандад 001001 как и ранее з&дйеаяо 001 101, а на контрольной ступеяи вместо переданного слова 0101 принятф слово 1101. Поскольку команде 001101 соответствует контрольное слово ООН, то образуется комбинация ощибки ООН -+- 1101 1110, под воздействием которой схемы «И 222, 223, 224 формируют сигналы коррекции четвертого, пятого и шестого разрядных мест. После коррекции в регистре вместо переданной команды 001 001 окажется записанной ложная команда 001010.

Для исключения формирования ложной команды при наличии ошибки в контрольной иосидке -в третьей группе схем «И 2i9-224 помимо рабочих предусмотрены также и защитные входы. Так нер1вый и второй (рабочие) входы схемы «И 22 соединены с единичными выходами триггеров 4 и 4д, а защитные (третий и четвертый) входы соединены с нулевыми выходами триггеров 4 и 4io; рабочие (первый и второй) входы схемы «И 223 соединены с единичными выходами триггеров 4 и 4д, а защитные (третий и четвертый) входы соединены с нулевыми выходами триггеров 48 и 4io; рабочие (первый и второй) входы схемы «И 224 соединены с единичными выходами триггеров 4 и 4$, защитные (третий и четвертый) соединены с нулевыми выходами триггеров 49 и 4io.

Подобным же образом осуществлены входные связн и для остальных схем «И 2i9, 220, 221. Любая схема «И срабатывает лишь в случае наличия единичных сигналов на всех ее входах - рабочих и защитных.

Для комбинации ошибки 1110 будут иметь место нулевые сигналы на защитном третьем входе схемы «И 222, соединенным с нулевым выходом триггера 4, на защитном (третьем) входе схемы «И 22з, соединенным с нулевым выходом триггера 4, .на защитном (третьем) входе схемы «И 224, соединенным с нулевым выходом триггера 49 Поэтому на выходах схем «И 222, 223, 224 сигналы коррекции не появляются и ложная команда 001010 не образуется.

Однако при декодировании записанной в регистре 12 комбинации 001101 помимо переданной команды 000101. образуется и ложная команда 000 101. Во избежание декодирования ложной команды дешифратор команд также выполнен по схеме с числовой защитой-г схемы «И дешифратора соединены как с единичными, так и с нулевыми выходами триггеров регистра 12. Если вес комбинации, занисанной в регистре 12, отличается от установленного значения, то 5 имеет место защитный отказ - неисполнение команды.

Предмет изобретения

0 Устройство для приема команд, содержащее дешифратор адреса, выполненный на схеме «И и триггере, входы которого соединены с входными шинами, а выход - с одними входами первой группы схем «И, другие входы которых соединены с соответствующими входными шинами, регистр, выполненный на счетных триггерах, выходы которых соединены с соответствующими входами дешифратора команд, отличающееся тем, что, с

(i целью повышения помехоустойчивости устройства, в него введены дополнительные группы схем «И, группы схем «ИЛИ, дополнительный регистр, распределитель импульсов, выполненный в виде пересчетной схемы, вход

5 которой через схему «И подключен к выходам генератора и триггера, а выходы - к соответствующим входам матричной схемы, ждущие одноБибраторы, дифференцирующие цепи, триггеры и схемы «И, причем первые

входы пер1вой группы схем «Pi подключены к соответств5ющим входным шинам приема командных признаков, первые входы второй группы схем «И соединены с соответствующими входными шинами приема контрольного признака, выход схемы «И дешифратора адреса подключен к первому входу триггера дешифратора адреса и через вторую дифференцирующую цепь подключен к соответствующему входу первого регистра, второй вход

0 триггера дешифратора адреса соединен с выходом первой дифференцируюшей цепи, выход триггера дешифратора адреса подключен к вторым входам первой группы схем «И и через последовательно соединенные первые

5 ждущий одновибратор и дифференцирующую цепь - к первому входу триггера распределителя импульсов, последний выход которого подключен к сбросовому входу своего триггера, к сбросовому входу первого триггера и

0 через последовательно соединенные второй ждущий одновибратор и третью дифференцирующую цепь - к соответствующим входам первого триггера, третьего ждущего одновибратора, к первому входу второго триггера и

55 соответствующим входам третьей группы схем «И, выход третьего ледущего одновибратора через четвертую дифференцирующую цепь подключен к сбросовому входу второго триггера и к соответствующим входам первого и дополнительного регистров, выход первого триггера подключен к вторым входам второй группы схем «И, выходы первой группы схем «И через первые входы первой группы схем «ИЛИ подключены к первому 65 регистру, вторые входы первой группы схем

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ПРИЁМА КОМАНД ТЕЛЕУПРАВЛЕНИЯ | 1973 |

|

SU409276A1 |

| УСТРОЙСТВО для ПРИЕМА КОМАНД ТЕЛЕУПРАВЛЕНИЯ | 1973 |

|

SU405126A1 |

| Многоканальное устройство для сопряжения абонентов с ЦВМ | 1990 |

|

SU1777146A1 |

| Селекторный канал | 1982 |

|

SU1053096A1 |

| ОТКАЗОУСТОЙЧИВАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА С АППАРАТНО-ПРОГРАММНОЙ РЕАЛИЗАЦИЕЙ ФУНКЦИЙ ОТКАЗОУСТОЙЧИВОСТИ И ДИНАМИЧЕСКОЙ РЕКОНФИГУРАЦИИ | 2010 |

|

RU2455681C1 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

| Устройство для контроля хода программ | 1987 |

|

SU1501065A1 |

| Устройство для сопряжения цифровой вычислительной машины | 1987 |

|

SU1444793A1 |

| Устройство для контроля состояния технических объектов | 1983 |

|

SU1156011A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ДВУХ ЭВМ | 1988 |

|

RU1554636C |

Авторы

Даты

1975-01-30—Публикация

1973-01-25—Подача