(Л

ел

о: ел

3150

гистраль 8 команд и данных ЭВМ, регистр 15, и 1фровой компаратор 16, первьп одновибратор 22, второй одно- вибратор 23, счетчик 25, При пуске микроэвм во время выполнения первой же команды процессора .Чтение или Запись запускается первый одновибратор 22. Коды команд программы, поступая по совмещенной магистрали 8 команд и данных ЭВМ для вьтолнения на процессор микроэвм, подаются также на вход параллельного формирователя 1 сигнатур. При этом формируют сигнал тактирования последнего. Формируемую сигнатуру периодически записывают по адресу цифрового компарато0654

ра 16, на котором при этом происходит сравнение текущей сигнатуры с эталонной, содержащейся в регистре 5 15, Одновременно происходит перезапуск первого одновибратора 22. Если цифровой компаратор 16 обнаруживает несравнение, формируется сигнал перезапуска микроэвм. В случае отсут10 ствия перезапуска первого одновибратора 22 сигнал с его выхода запускает второй одновибратор 23, выходной импульс которого перезапускает микро- ЭВМ. Счетчик 25 подсчитывает коли- 5 чество перезапусков микроЭВМ и по

достижении некоторого заданного числа останавливает работу микроЭВМ. 1 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| МОДУЛЬ СИСТЕМНОГО КОНТРОЛЯ | 2003 |

|

RU2265240C2 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ИЗОБРАЖЕНИЙ | 1990 |

|

RU2047921C1 |

| Устройство для сопряжения ЭВМ с внешним устройством | 1986 |

|

SU1377864A1 |

| Устройство для проверки выполнения последовательности команд микропроцессора | 1984 |

|

SU1247874A1 |

| Устройство для отладки и контроля хода программ | 1989 |

|

SU1691843A2 |

| ЭВМ | 1990 |

|

RU2024928C1 |

| Устройство для ввода-вывода информации | 1987 |

|

SU1451674A1 |

| Устройство для контроля хода программы и перезапуска ЭВМ | 1987 |

|

SU1501066A2 |

| Распределенная система управления | 1989 |

|

SU1732345A1 |

| Устройство приоритетного доступа к общей шине | 1990 |

|

SU1711173A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано в вычислительных устройствах с совмещенной магистралью команд и данных. Целью изобретения является расширение диагностических возможностей устройства за счет выполнения оперативного тестирования микро ЭВМ. Устройство содержит формирователь 1 сигнатур, совмещенную магистраль 8 команд и данных ЭВМ, регистр 15, цифровой компаратор 16, первый одновибратор 22, второй одновибратор 23 и счетчик 25. При пуске микроЭВМ во время выполнения первой команды процессора "Чтение" или "Запись" запускается первый одновибратор 22. Коды команд программы, поступая по совмещенной магистрали 8 команд и данных ЭВМ для выполнения на процессор микроЭВМ, подаются также на вход параллельного формирователя 1 сигнатур. При этом формируют сигнал тактирования последнего. Формируемую сигнатуру периодически записывают по адресу цифрового компаратора 16, на котором при этом происходит сравнение текущей сигнатуры с эталонной, содержащейся в регистре 15. Одновременно происходит перезапуск первого одновибратора 22. Если цифровой компаратор 16 обнаруживает несравнение, формируется сигнал перезапуска микроЭВМ. В случае отсутствия перезапуска первого одновибратора 22 сигнал с его выхода запускается второй одновибратор 23, выходной импульс которого перезапускает микроЭВМ. Счетчик 25 подсчитывает количество перезапусков микроЭВМ и по достижении некоторого заданного числа останавливает работу микроЭВМ. 1 ил.

Изобретение относится к цифровой вычислительной технике и может быть

использовано в вычислительных устройствах с совмещенной магистралью команд и данных.

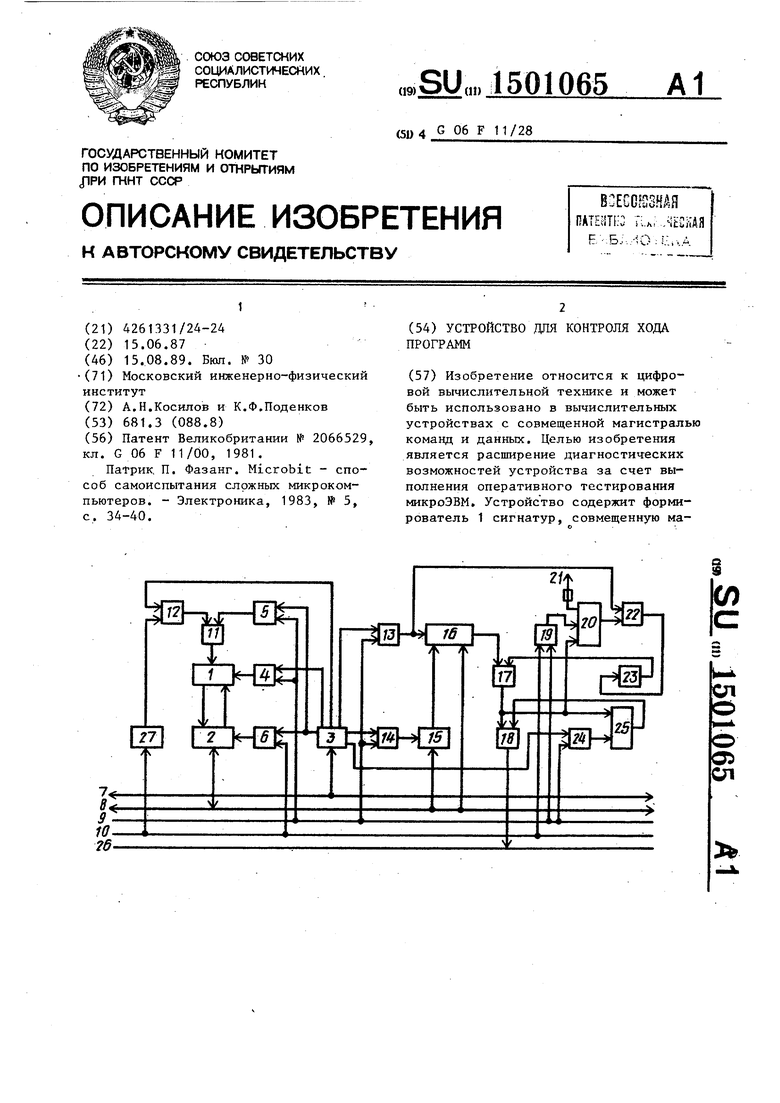

Цель изобретения - расширение диагностических возможностей устройства.На чертеже показана структурная схема устройства.

Устройство содержит формирователь 1 сигнатур, коммутатор 2, дешифратор 3 адреса, первьй 4, второй 5 и трети 6 элементы И, вход 7 адреса, совмещенную магистраль 8 команд и данных ЭВМ,.вход 9 Запись устройства, вхо 10 Чтение устройства, первый элемент ИЛИ 11, четвертый 12, пятьш 13 и шестой 14 элементы И, регистр 15 эталона, схему 16 сравнения, второй .17, третий 18 и четвертый 19 элементы ИЛИ, триггер 20, вход 21 единичного потенциала, одновибратор 22 с перезапуском, формирователь 23 импульсов, седьмой элемент И 24, счетчик 25 импульсов, выход 26 Перезапуск ЭВМ и элемент 27 задержки.

Устройство работает следующим образом.

Предполагается,что, поскольку устройство работает в составе микроЭВМ, кроме него к входу 7, магистрали 8, входам 9 и 10 и вьгкоду 26 подключены еще по меньшей мере процессор и ПЗУ (к выходу 26 подключен только процессор) . В дальнейшем предполагается также, что активному сигналу в уст5

0

з 0 5

о

ройстве соответствует уровень 1, а пассивному - уровень О. На линиях 9, 10 и 26 активные сигналы появляются во время выполнения процессором микроэвм операций, соответствующих их названиям. Все остальное время на этих линиях находятся уровни О, Пассивный сигнал с выхода элемента И 6 настраивает коммутатор 2 на передачу данных с магистрали 8 на информационный вход формирователя 1 сигнатур, Активньш сигнал с выхода элемента И 6 переключает коммутатор 2 на передачу данных с выхода формирователя 1 на магистраль 8. Активный сигнал на первом выходе дешифратора 3 адреса (выход, подклю- ченньш к входам элементов И 5 и 6) появляется при обращениях -процессора по адресу формирователя сигнатур. Все остальное время на первом выходе дешифратора 3 адреса присутствует уровень О. Активньм сигнал на втором выходе дешифратора адреса 3 (выход, подключенньй к входу элемента И 4) появляется при обращениях процессора по адресу сброса формирователя 1. Все остальное время на втором выходе дешифратора 3 адреса присутствует уровень О. Активный сигнал на третьем выходе дешифратора адреса 3 появляется при обращениях процессора по каждому из адресов, принадлежащих области памяти, в которой записана функциональная программа работы микроэвм (третий выход дешифратора адреса подключен к вхо, ду элемента И 12). Все остальное время на третьем выходе дешифратора 3 адреса присутствует уровень О.

Активный сигнал на четвертом выходе дешифратора адреса 3 (выход, подключенный к входу элемента И 13) появляется при обращениях процессора по адресу схемы 16. Все остальное время на четвертом выходе дешифратора адреса 3 присутствует уровень О. Активный сигнал на пятом выходе дешифратора 3 адреса (выход, подключенный к входу элемента И 14) появляется пр обращениях процессора по адресу регистра 15. Все остальное время на пятом выходе дешифратора 3 адреса присутствует уровень О. -Активный сигнал на шестом выходе дешифратора адреса 3 (выход, подключенный к входу элемента И 24) появляется при обращениях процессора по адресу сброса счетчика 25. Все остальное время на шестом выходе дешифратора адреса 3 присутствует уровень О. Сигналы на выходе 26 действуют на процессор следующим образом: при появлении активного сигнала процессор останавливается и находится в этом состоянии до тех пор, пока сигнал на выходе 26 вновь не станет пассивным, после чего мироЭВМ вьтолняет процедуру начального запуска. Предполагается также, что при включении питания устройства триггер 20 и счетчик 25 сбрасывается в состояние О. При наличии пассивного сигнала на выходе элемента И 13 схеме 16 запрещено сравнение и на ее выходе установлен пассивньй сигнал. В нормальном состоянии на выходе формирователя 23 установлен уровень О. Сброс и тактирование всех схем устройства про1|зводятся активными сигналами.

После начального запуска микроЭВМ при появлении любого из активных сигналов Запись или Чтение на соответствующих входах устройства на выходе элемента ИПИ 19 появляется активный сигнал, по фронту которого в триггер 20 записывается 1. По фронту выходного сигнала триггера 20 запускается одновибратор 22. При этом на его выходе появляется уровень О, По другому входу одновибратор 22 может быть перезапущен. Если этого не происходит, то после заданной вьщерж ки на выходе одновибратора 22 вновь устанавливается уровень 1 (пол

5010656

ностью сформирован выходной и myльc) по фронту которого на выходе формирователя 23 формируется единичный импульс заданной последовательности, KOTOpbtft через элементы ИЛИ 17 и 18 поступает на выход 26 и микроЭВМ перезапускается. Одновременно активный сигнал с выхода элемента ИПИ 17

10 сбрасывает в О триггер 20, а фронт этого сигнала увеличивает на единицу содержимое счетчика 25. После перезапуска микроэвм по первому активному сигналу на входах 9 или 10 вновь

5 запускается одновибратор 22, При достижении содержимым счетчика 25 некоторого заданного зара.нее числа (сброс счетчика не производите, а сбои в работе микроэвм фиксируются, т.е.

20 микроэвм после перезапуска не может войти в режим нормальной работы) на выходе счетчика 25 появляется уровень 1, которьй через элемент ИЛИ 18 поступает на выход 26 и останавливает

25 работу микроэвм. После этого микроЭВМ может быть вновь запущена в работу только внешним по отношению к ней сбросом счетчика 25 (например, выг ключением и затем включением питания микроэвм), Если максимально допустимое значение содержимого счетчика 25 не достигнуто, может быть осуществлен его программный сброс. Дпя этого процессор выполняет, операцию записи по адресу сброса счетчика 25. При этом на выходе элемента И 24 появляется активньй сигнал, сбрасывающий содержимое счетчика 25 в ноль. При выполнении программы коды команд, поступая по магистрали 8 из памяти на процессор для вьшол- нения, одновременно с этим подаются через коммутатор 2 на.информационные , входы формирователя 1. При этом на выходе элемента И 12 с задержкой, достаточной для надежного установления кода команды на информационных входах формирователя 1, появляется активньй сигнал, фронт которого че-

рез элемент ИЛИ 11 тактирует форми30

35

40

45

55

рователь 1, вызывая запись в него текущей входной информации. Требуемая задержка обеспечивается элементом 27 задержки. Таким образом по мере выполнения программы в формирователе 1 формируется сигнатура последовательности кодов команд, поступившых в процессор для выполнения. Сравнивая периодически текущие

сиг патуры с заранее определенными i эталонными, в случае их равенства делают вывод, что микроЭВМ работает верно, а в случае неравенства - неверно. Для обеспечения повторяемости сигнатур в самом начале выполнения программы выполняют сброс в О содержимого формирователя 1. Для этого процессор производит запись по адресу сброса формирователя 1. При этом на выходе элемента И 4 формируется активный сигнал, поступающий на вход сброса формирователя 1. При необходимости сформировать в автоном- ном режиме сигнатурку некоторого массива данных процессор последовател - но все слова массива записьгаает по адресу формирователя 1„ При этом коды слов массива поступают на инфор- мационные входы формирователя 1 через коммутатор 2, а на выходе элемента И 5 формируются активные сигналы, фронты которых через элемент ИЛИ 11 тактируют формирователь 1, за- письгоая в него текущую входну ю информацию, причем один тактирукяций фронт соответствует одному коду слова массива. Работа в этом режиме облегчается, если программа записи слов массива в формирователь 1 расположе- на вне области памяти функциональной программы, на адреса которой нйстро- ен третий выход дешифратора 3 адреса. При сравнении текущей сигнатуры с заранее определенной эталонной сигна- турой процессор вначале выполняет запись последней по адресу регистра 15, При этом на выходе элемента И 14 формируется активньй сигнал, поступающий на тактовый вход регистра 15. По приходу .этого сигнала значение эталонной сигнатуры запоминается в регистре 15. После этого процессор выполняет чтение текущей сигнатуры, для чего выполняет операцию чтения с ад- реса формирователя 1. При этом на выходе элемента И 6 появляется активный сигнал и значения разрядов информационных выходов формирователя 1 через коммутатор 2 поступают на магист- раль 8. Считав текущую сигнатуру, процессор выполняет операцию записи ее значения по адресу схемы сравнения 16, При этом на выходе элемента И 13 появляется активный сигнал, разрещающий сравнение схеме 16. Схема 16 выполняет сравнение кода содержащейся в регистре 15 эталонной сигнатуры с

5

Q n 0 35 40 45 50 55

кодом текущей сигнатуры, находящейся в это время на магистрали 8. В случае равенства этих кодов на выходе схемы 16 сохраняется уровень О и после окончания выполняющейся команды записи процессор продолжит дальнейщее выполнение программы. При неравенстве сравниваемых кодов на выходе схемы 16 появляется активный сигнал, кото- рьш через элемент ИЛИ 17 сбрасьшает в О триггер 20, инкрементирует содержимое счетчика 25 и через элемент ИЛИ 18 осуществляет.перезапуск микроэвм. Одновременно с разрешением сравнения схеме 16 активный сигнал с выхода элемента И 13 осуществляет перезапуск одновибратора 22. Таким образом, если в работе микроЭВМ произошла ошибка, выразившаяся в неправильной последовательности кодов команд программы, поступившых для выполнения на процессор, то при первой же после ошибки записи текущей сигнатуры по адресу схемы 16 микроЭВМ перезапускается. Если по каким-либо прининам запись текущей сигнатуры по адресу схемы 16 долгое время не производится, то микроэвм также перезапускается срабатыванием.формирователя 23. Реакцией на такие перезапуски может быть, к примеру, повторение участка программы начиная с некоторого контрольного адреса. Введя в функциональную программу .микроэвм командные вставки проверки текущей сигнатуры с таким расчетом, чтобы период записи по адресу схемы 16 не превышал длительности выходного импульса одновибратора 22, достигают достоверного и достаточна полного оперативного тестирования микроЭВМ.

Для работы предлагаемого устройства необходимо, чтобы в одних и тех же точках программы получались одни и те же сигнатуры независимо от пути вьшолнения программы. Для достижения этого можно использовать следукщий метод. В программе выделяют такие контрольные точки: Н (начало) - слово программы, вводимое в процессор первым после начального сброса сигнатурного регистра; КС 1 (контрольное слово перв ого типа) - слово программы, вводимое в процессор первым после вьшолнения команды безусловного перехода или команды условного перехода при выполненш условия; КС2 (контрольное слово

у15

второго типа) - слово программы, вво которого в процессор завершает формирование сигнатуры, сравниваемой затем с эталонным значением; СКП (слово команды перехода) - последнее вводимое в процессор слово каждой из команд условного и безусловного переходов; НП (начало подпрограммы) - первое вводимое в процессор слово подпрограммы при передаче ей управления; СВП (слово вызова подпрограммы) - последнее вводимое в процессор слово каждой из команд условного и безусловного вызовов подпрограмм; СКВ (слрво команды возврата) - слово команды условного и безусловного возвратов из подпрограмм -. (предполагает

одного слова). Каждому вьщеленному контрольному слову присваивают контрольный номер. При этом обязательно присваивают одинаковые контрольные номера взаимодополняющим словам СКП и КС1, а также словам СВП, НП, СКВ, относящимися к одной подпрограмме. Если S - слово программы, то S+1 - слово программы с адресом, на единицу адресации большим адреса слова S, а S-1 - слово программъ с адресом, на единицу адресации адреса слова S. Допустим, S - контрольное слово с контрольным номером J, такой же номер имеют и слова S+1 и S-1. Программу микроэвм разбивают на линейные отрезки а;, b-J, где 1, j - контрольные номера контрольных слов а и Ь, при этом а , НП

КС1, скп+1, скв+1, свп+1 , be

& кС1-1, СКП, СВП, СКв. Под линейностью отрезков в данном случае понимается отсутствие внутри них контрольных слов. Последние могут находиться только на границах отрезков. Предполагая, что в начале отрезка непосредственно перед вводом в процессор слова аt сигнатура равна i, путем ввода внутрь отрезка дополнительных командных вставок добиваются того, чтобы в случае правильной последовательности поступавших на процессор кодов команд отрезка, сразу после ввода в процессор слова Ь; сигнатура была равна j. Значение сигнатуры, полученное после начального сброса сигнатурного регистра, исполь зуют в качестве исходной при обработке отрезка н, bj . В точках КС2 выполняют вьщачу текущего значения сигнатуры по адресу схемы 16. Значе

10

1-5

0

5

0

5

5

0

5

0

ние эталонной сиг ;атуры огтределяют относительно ближайшего предшествующего по ходу программ. данному КС2 нумерованного слова. Если где-либо на участке программьг до данного КС2 произошла ошибка любой кратности и вида в последовательности кодов команд, поступающих на процессор, то текущая сигнатура в момент проверки не совпадает с эталонной и ошибка будет обнаружена. Дополнительные командные вставки, вводимые внутрь отрезков, должны позволять произвольным образом корректировать сигнатуру, получаемую в конце отрезка, на основе ее известного, значения в начале отрезка и при этом не должны влиять на функ щональ- ные результаты работы программы. Этим требованиям удовлетворяет команда записи слова по адресу регистра 15 с непосредственной адресацией (записываемое слово является вторым словом команды). В этом случае подбором второго слова команды корректируют требуемым образом получаемую в конце отрезка сигнатуру.

Формула изобретения

Устройство для контроля хода программ, содержащее формирователь сигнатур, коммутатор, дешифратор адреса, первый, второй и третий элементы И, причем выход коммутатора соединен с информационным входом формирователя сигнатур, выход которого соединен с информа щонным входом коммутатора, вход записи устройства соединен с первыми входами первого и второго эле- элементов И, выход первого элемента И соединен со входом начальной установки формирователя сигнатур, адрес- ньй вход устройства соединен с информационным входом дешифратора адреса, первый выход которого соединен со вторь м входом второго элемента И и с первым входом третьего элемента И, вход чтения устройства и второй, выход дешифратора адреса соединены со вторыми входами соответственно третьего и первого элементов И, выход третьего элемента И соединен с управляющим входом коммутатора, информационный вход-выход устройства через двухстороннюю магистраль соединен с входом- выходом коммутатора, отличающееся тем, что, с целью расширения диагностических во: можностей за счет оперативного тестирования микроЭВМ, в него введены четыре элемента ИЛИ, четвертый, пятый, шестой и седьмой элементы И, регистр эталона, схема сравнения, триггер, одновибратор с повторным запуском, формирователь импульсов, элемент задержки и счетчик импульсов, причем вход чтения устройства через элемент задержки сое соединен с первым входом четвертого элемента И, выход которого соединен с первым входом первого элемента ИЛИ, .выход второго элемента И соединен с вторым входом первого элемента ШШ, выход которого соединен с тактовым входом формирователя сигнатур, трет тий, четвертый, пятый и тестой выхЬ- ды дешифратора адреса соединены соответственно с вторым входом четвертого элемента И, первым входом пятого элемента И, первым входом шестого элемента И и первым входом, седьмого элемента И, выход пятого элемента И соединен с входом разрешения сравнения схемы сравнения и входом перезапус- ка одновибратора с повторным запуском, выход которого через формирователь импульсов соединен с первым входом второго элем€1нта ИЛИ, выход которого соединен с первым входом третье-

го элемента ИЛИ, со счетным входом счетчика импульсов и входом установки в О триггера, вход записи устройства соединен с первым входом четвертого элемента ИЛИ, вторым входом седьмого элемента И, вторым входом пятого и вторым входом шестого элемента И, выход которого соединен с входом записи регистра эталона, ин- формационньй вход устройства соединен с первым входом схемы сравнения и информационным входом регистра эталона, выход которого соединен с вторым входом схемы сравнения, выход неравенства которой соединен с вторым входом второго элемента ИЛИ, вход чтения устройства соединен с вторым входом четвертого элемента ИЛИ, выход которого соединен с тактовым входом триггера, информационный вход триггера соединен с шиной единичного потенциала, выход триггера соединен с входом запуска одновибратора с повторным запуском, выход седьмого элемента И соединен с входом, установки счетчика импульсов, выход которого соединен с вторым входом третьего элемента ШШ, выход которого является выходом перезапуска устройства.

| ДОЖДЕВАЛЬНЫЙ АППАРАТ | 1991 |

|

RU2066529C1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Патрик, П | |||

| Фазанг | |||

| Microbit - способ самоиспытания сложных микрокомпьютеров | |||

| - Электроника, 1983, № 5, с | |||

| Нивелир для отсчетов без перемещения наблюдателя при нивелировании из средины | 1921 |

|

SU34A1 |

Авторы

Даты

1989-08-15—Публикация

1987-06-15—Подача