I

Изобретение от1носится к вычислительной технике и может найти при.менение при построении за1поминаю:щих устройств.

Извест1ны за1поми1на1ондие устройства, соде1ржащие на:копител« с линейной выборкой инфорМации с разрядными обмотка мн, В1ключеняьгми но си:М.мет1ри.чиой бала1нсной схеме, н диодные адресные коммутаторы с дешнфраторайш.

В та,ких устройствах плохо компенсируется помеха, обусловленная ларазитиыми емкостями запертых диодов диодного адресного коммутатора и емкостЯ|МИ между адреснЕлми и разряднььми обмотка|ми.

Цель изобретения - повышение помехоустойчивости устройства.

Это достигается тем, что одни из адресных обмоток «акопителя и соответствующие им диоды ком,мутатора, подключенные к одному из ключей дешиф;ратО|ра, связаиы иидуктив нэ с одними из плеч разрядных обмоток, а другие адресные обмотки и диоды, подключенные к этому же ключу дешифратора, индуктивно связаны с другими плечами разрядных об.моток.

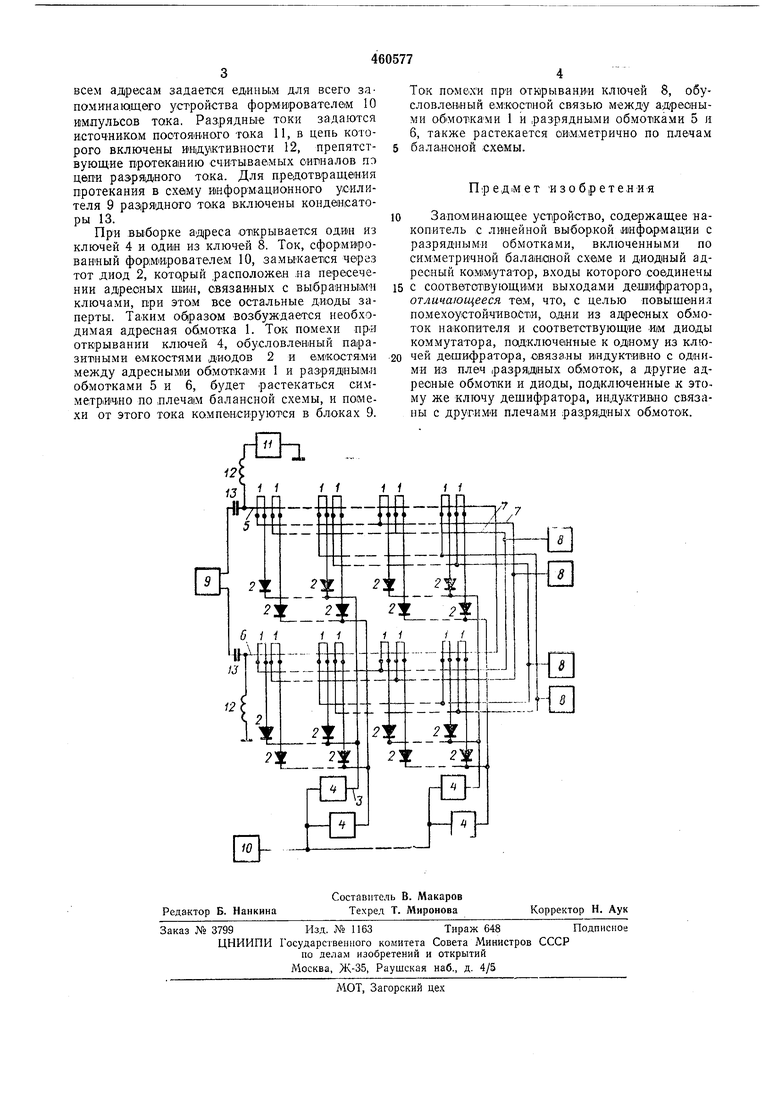

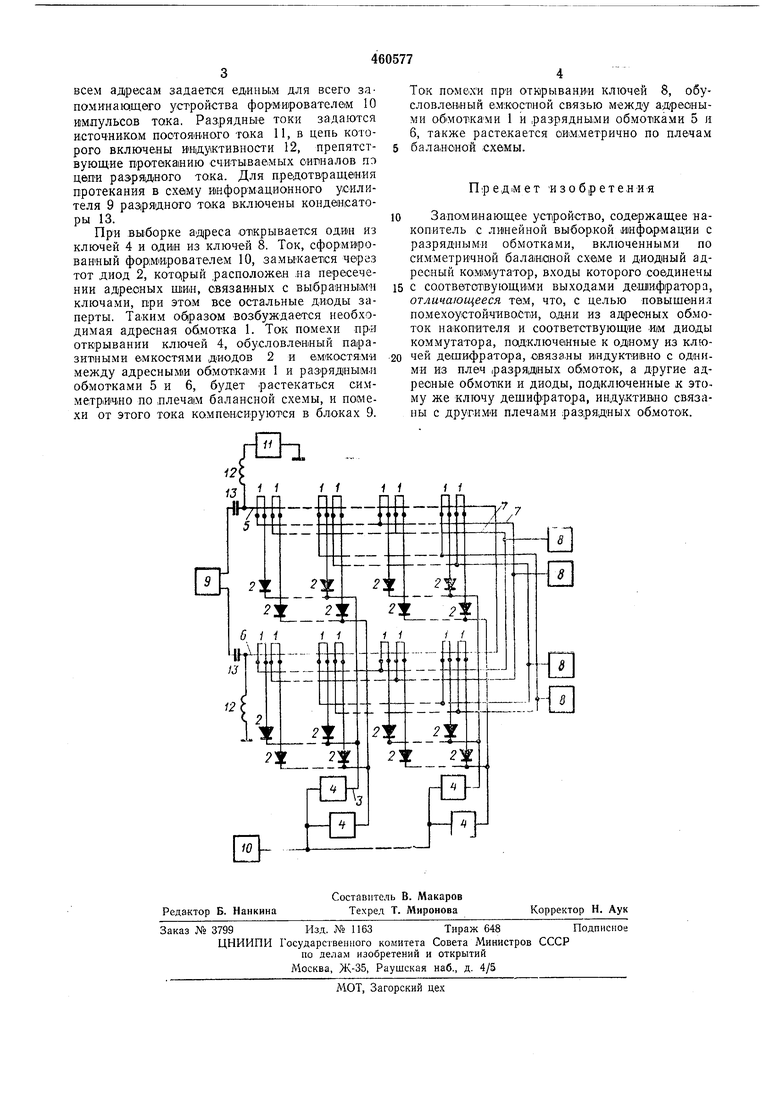

На чертеже приведена схема одного разряда запОМинаюндего устройства.

Последователыно адресным об:мотка:м 1 включены диоды 2 адресного коммутатора. Диоды 2 объеди1няются по групнам адресными

iJiEHa-MiH 3, подключенными к подготовительным |Ключа|М 4. Подготовительные ключи усЛОВ.НО разбиваются через один на четные и нечетные. Все адресные обмотки 1, подключенные через диоды 2 и адресные швны 3 к четным ключам 4 считываются четными, а все обмотки, подключенные к 1нечет1НЫ1М ключам 4, - «ечетнымИ. Пр|И этом каждая группа диодов 2 состоит из двух половин, одна половина

группы диодов подключена ,к адреоным обмоткам, связанным с разрядной обмоткой 5, включенной в одно плечо |балансной схе,мы, а другая половина группы диодов подключена к адреоным обмоткам, связан«ыд1 с разрядной

обмоткой 6, включанной в другое плечо балаеоной ;охемы.

Выходные контакты адресных обмоток 1 объединяются .по группам адресными шинами 7, подключанаьпми к разрешаюш,им ключа:м 8. При этом каждая группа выходных контактов состоит из двух половин, од«а половина группы объединяет четыре адресные обмотки, связа1нные с |разрядной обмоткой, включенной В одно плечо балансной схемы, а

другая половина грунны объединяет нечетные адресные обмотки, связаш1ые с разрядной обмоткой, включанной в другое плечо бала-нсной схемы.

Блоки 9 усиливают информадиоиные сигналы при считываиии информации. Ток по

| название | год | авторы | номер документа |

|---|---|---|---|

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1969 |

|

SU251004A1 |

| Запоминающее устройство | 1979 |

|

SU809367A1 |

| БЛОК ПАМЯТИ ЗАПОМИНАЮЩЕГО УСТРОЙСТВА НА МАГНИТНЫХ ПЛЕНКАХ | 1967 |

|

SU222469A1 |

| УНИВЕРСАЛЬНАЯ ЦИФРОВАЯ УПРАВЛЯЮЩАЯ МАШИНА | 1965 |

|

SU170218A1 |

| Система заряда аккумуляторной батареи асимметричным током | 1990 |

|

SU1723626A1 |

| УСТРОЙСТВО НЕПРЕРЫВНОГО АВТОМАТИЧЕСКОГО КОНТРОЛЯ И ВЫРАВНИВАНИЯ СТЕПЕНИ ЗАРЯЖЕННОСТИ АККУМУЛЯТОРОВ БЛОКА | 2018 |

|

RU2695081C1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1969 |

|

SU254571A1 |

| ДВУХТАКТНЫЙ МОСТОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2010 |

|

RU2455746C2 |

| Устройство для управления многофазным шаговым электродвигателем | 1982 |

|

SU1037410A1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО МОНИТОРИНГА БЛОКА АККУМУЛЯТОРОВ С КОНТРОЛЕМ ТЕМПЕРАТУРЫ | 2018 |

|

RU2686072C1 |

Авторы

Даты

1975-02-15—Публикация

1973-02-22—Подача