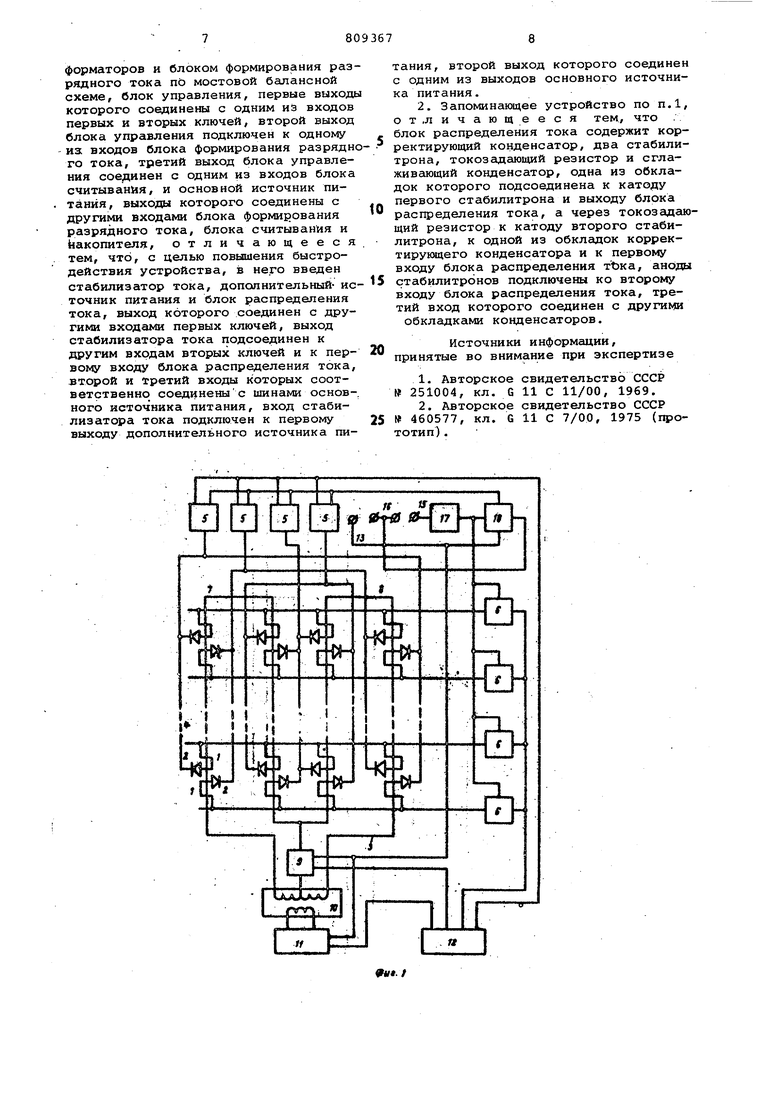

Изобретение относится к устройствам для записи информации в электрических цифровых накопителях и может быть использовано в вычислительной технике и системах обработки и хранё ния информации. Известно эапокшнаюцее устройство с линейной выборкой информации, с ра рядными шинаТШ, включеншлми по cи 4метричной мостовой схеме и содержащее диодный адресный ко шутатор, управляеьолй двумя дешифраторгши, при этом половина адресных обмоток и соответствующих им диодов, подключенны к любому ключу дешифратора связана с разрядными обмотками, включенными в одно мостовой схемы, а вторая половина адресных обмоток и диодов, подключенных к этому ключу, связана с разрядHifMH обмотк и 1и, включенными в противоположное плечо мостовой схе «. 1. В устройстве компенсируются помехи, обусловленные паразитными емкоетями запертых диодов адресного коммутатора и емкостями между адресными и разрядными обмотками. Однако в этом устройстве не устра няются выбросы на переднем фронте и спад вершины адресных импульсов, вызванные реактивностями адресных обмоток, что препятствует повьшению быстродействия и информационного объема известного устройства. Наиболее близким к изобретению по технической Сущности является запоминающее устройство, которое содержит накопитель с линейной выборкой информации с разрядными обмрткгши, включенными- по симметричной балансной схеме и диодный адресный коммутатор, выходы которого соединены с соответствующими выходгши управляемого дешифратора, содержащего две группы ключей, при 3toM один из адресных обмоток накопителя и соответствующие им диоды ко1«4утатора, подключенные к одному из ключей дешифратора связаны индуктивно с одниьо из плеч разрядных оёмоток, а другие адресные обмотки и соответствующие им диоды коммутатора, подключенные к этому же ключу дешифратора связашл индуктивно с другими плечами разрядных обмоток 2J . В известном устройстве также компенсируются помехи, обусловленные пара ЗИТНЫАШ емкостями запертых диодов адресного коммутатора и емкостями , между адресными и разрядными обмотками. Но в известном устройстве, использукндем единый формировате.ть импульсо тока, который прерывает работу в соответствии с обращением к запоминаю, тему устройству, не устраняются выбросы на переднем фронте и спад вершины импульсов адресного тока, свяранные с режимом насыщения транзисторов формирователя и Ключей, а также возникновением противо-ЭДС индукции адресных обмоток, что снижает быстродействие устройства, так как для устранения выбросов необходимо формировать импульсы с пологими фронтами, что приводит к увеличению времени обращения. Но ив этом случае фронт импульса тока должен оставаться дЪстаточно крутым (например, при исполь зовании в качестве запоминающего элемента цилиндрических магнитных пленок, длительность фронта должна быть tcpft30-60 не) . Спад вершины непосредственно связан с увеличением времени перемагничивания, что также приводит к увеличению времени обращения. Низкое быстродействие, в свою очередь, является преградой к увеличению информационной емкости накопителя. В известном устройстве для устранения указанных недостатков не используется энершя питания формирователя и ключей, так как нет возможности пере распределения тока, налример из адресных цепей в разрядные во время формирования импульсов адресного тока. Цель изобретения - повышение быст родействиясустройства. Поставленная цель достигается тем что в запоминающее устройство, содер жащее иакопитепь, одним из выводов адресных которого соединены через диоды адресного коммутатора с выходами первых ключей, другие выводы адресных обмоток подсоединеш 1 к выходам вторыЗ ключей, разрядные обмотки накопителя, включенные совмест но с первичными обмотксши развязываю щих трансформаторов и блоком формирования разрядного тока по балансной схеме, блок управления, первые йыходы которого соедкнешл с одним из вхо дов первых и вторых ключей, второй выход блока управления подключен к одному из входов блока формирования разрядного тока, третий выход блока ущ)авления соединен с одним из входов блока считывания, и основной источник питания, выходы которого соед иены с другими входами: блока формиро вания разрядного тока, блока считыва ния и накопителя, введен стабилизато тока, дополнительный источник питани и блок распределения тока, выход которрго соединен с другими входами первых ключей, выход стабилизатора т ко подсоединен к другим входам вторых ключей и к первому входу блока распределения тока, второй и третий входы которых соответственно соединены с шинами основного источника питания, вход стабилизатора тока подключен к первому выходу дополнительного источника питания, второй выход которого соединен с одним из выходов основного источника питания, а также тем, что блок распределения тока содержит корректирующий конденсатор, два стабилитрона, токозадающий резистор и согласовывающий конденсатор, одна из обкладок которого подсоединена к катоду первого стабилитрона и выходу блока распределения тока, а через токозадающий резистор., к катоду второго стабилитрона, к одной из обклсодок корректирующего конденсатора и к первому входу блока распределения тока, аноды стабилитронов подключены ко второму входу блока распре-/ деления тока, третий вход которого соединен с другими обклащками конденсаторов . На фиг. 1 изображена функциональная схема устройства; на фиг. 2 электрическая схема блока распределения тока и стабилизатора тока. Запоминающее устройство содержит адресные обмотки 1, диоды 2, адресные шины 3 и 4, ключи 5 и 6, разрядные обмотки 7 и 8, блок 9 формирования разрядного тока, развязывающие трансформаторы 10, блок 11 считывания, блок 12 управления, шины 13 и 14 основного источника питания, выходы 15 и 16 дополнительного источника питания, стабилизатор 17 тока и блок 18 распределения тока, состоящий из корректирующего конденсатора 19, стабилитронов 20 и 21 и сглаживающего конденсатора 22. Стабилизатор тока содержит транзистор 23, резистор 24 обратной связи, стабилитрон 25 и резистор 26 смещения. Устройство работает следующим образом. Когда ключи 6 и 5 раз амкнуты, ток из шины 15 дополнительного источника питания (например ) протекает через транзистор 23 и резистор 24 обратной связи стабилизатора 17 тока {фиг. 2), образуя напряжение обратной связи, которое (при изменении напряжения дополнительного источника питания либо нагрузки на выходе стабилизатора 17 тока) воздействует на .транзистор 23 и величина тока, протекающего через него, практически не изменяется. Далее ток протекает через стабилитроны 21 и 20 блока 18 и утилизируется в цепях питания блоков 9, 11. Стабилитрон 20, зашунтированный конденсатором 22, образует источник стабилизированного напряжения. Это нат пряжение подается к ключам 5 и является напряжением смещения. Таким образом, в случае, когда адрес не выбран, транзистор 23 стабилизатора тока 17 находится в активном режиме, рабочая точка его поддерживается постоянной и стабилизированный ток используется для питания блоков разрядного управления.

При выборе адреса блок 12 управления подает на входы ключей б и 5 импульсы управления, открывается один из ключей 6 и один из ключей 5, по(СЛедний фронт импульса адресного тока формируется в момент включения ключа 5, заданный фронт - ключа 6. При включении ключа 5, напряжение на адресной обмотке 1 ниже напряжения на стабилитроне 21 блока 18 (фиг. 2), но выше напряжения основного источника постоянного тока например U, +5В). Стабилитрон 21 закрыт К гщресной обмотке 1 прикладывается напряжение и быстро нарастает ток с крутым фронтом (например tq)fttOHc). Амплитуда и.мпульса адресного тока обеспечивается стабильной, благодаря каскгщу с общей базой на транзисторе 23 и нелинейной обратной связью стабилизатора 17 тока. Выбросы на переднем фронте импульса отсутствуют, так как до включения ключа 5 транзистор 23 стабилизатора 17 тока находился в активном режиме и рабочг1я точка транзистора lia выходной характеристике поддерживается постоянной. Конденсатор 19 блока 18 служит для коррекции частотной характеристики и также устраняет спад вершины импульса адресного тока. В момент времени, когда ключ 6 закрывается, напря жение на адресной обмотке 1 снижается, но оно будет больше напряжения на шине 13 основного источника постоянного тока, т.е. и ток из шины 13 не сможет затекать через стабилитрон 21 в адресную обмотку 1,

Сформированный тгцсим образом импульс адресного тока закикается через диод 2 (фиг. 1), который расположен на пересечении адресных шин 3 и 4, связанных с выбранными ключами 6 и 5. При этом все остальные диоды 2 заперты. Ток помехи при открывании ключей б и 5 и возбуждении адресной обмотки 1, обусловленный паразит1Ш1г ми емкостями диодов 2 и емкостями между адресными обмотками 1 и разрядными 7, 8, растекается симметрично по плеЧс1М балансной мостовой и компэнсируется в трансформаторах 10 и блоке 11 с штывания. После того, как ключ 6 закроется, ток на выходе стабилизатора 17 поддерживается неизменным и вызывает резкое увеличение напряжения на стабилитроне 21 блрка 18, что приводит к его пробою и протеканию в цепи питания блоков 9, 1Я

Таким образом, в основе технического решения заложен принцип перераспределения тока, благодаря чему транзистор 23 стабилизатора 17 всегда находится в активном режиме, и его

рабочая точка на выходной характеристике поддерживается постоянной. Этим устраняются выбросы на переднем фронте импульса адресного тока, спад вершины и обеспечивается высокое качество стабилиз ации, что повышает быстродействие устройства и исключает необходимость фор мровать импульсы с пологими фронтами в отличие от.известных схем, где работа стабилизатора или формирователя тока прерывается, и в начальный момент включения транзисторы этих устройств насыщаются, что гч иводит к появлению выбросов на переднем фронте импульсов.

После того, как ключ б закроется адресная обмотка 1 стремится сохранит неизменным адресный ток, поэтому возможны броски напряжен11я, для устранения которых и увеличения скорости спада заднего фронта импульса адресного тока могут быть применены известные способы, например при помощи дополнительных диодов и ключа. Ключи 5 и б, блоки 9 и 11 могут быть выполнены, в интегральном исполнении на микросхемах серии 169, трансформаторы 10 на базе малогабаритных импульсных трансформаторов типа БТИ-118, транзистор 23 стабилизатора 17 - типа 2Т904. Стабилитроны 20, 21 - типа Д815.

Использование новых элементов дополнительного источника питания, ста билизатора тока и блока распределения тока повышает быстродействие устройства за счет сокращения длительности переднего фронта и устранения выбросов и спада вершины импульсов адресного тока путем перераспределения тока стабилизатора при помощи устройства управления. Возможность утилизации части тока стабилизатора в цепи питания блоков разрядного управления позволяет уменьшить мощность рассеивания. Предложенное техническое решение не требует разработки специальных узлов, поэтому его применение в народном хозяйстве не вызывает необходимоо ти разработки новой элементной базы.

Предлагаемое изобретение принципиально не усложняет структурную схему запоминающего устройства и поэтому может быть использовано как при разработке новых запоминающих устройств, так и при модернизации существующих.

Формула изобретения

1. Запоминающее устройство, содержащее накопитель, одним из выводов адре.с,ных обмоток которого соединены через адресный коммутатор с выходами первых ключей, другие выводы адресных обмоток подсоединены к выходам вторых ключей, разрядные обмотки накопителя, включенные совместно с первичными обмотками развязывсцсяцих трансформаторов и блоком формирования раз рядного тока по мостовой балансной схеме, блок управления, первые выходы которого соединены с одним иэ входов первых и вторых ключей, второй выход блока управления подключен к одному из входов блока формирования разрядн го тока, третий выход блока управления соединен с одним из входов блока считывания, и основной источник питания, выходы которого соединены с другими входами блока формирования разрядного тока, блока считывания и йакопителя, отличающееся тем, что, с целью повышения быстродействия устройства, в него введен стабилизатор тока, дополнительный- ис точник питания и блок распределения тока, выход которого соединен с другими входами первых ключей, выход стабилизатора тока подсоединен к другим входам вторых ключей и к первому входу блока распределения тока, второй и третий входы которых соответственно соединеныс шинами основного источника питания, вход стабилизатора тока подключен к первому выходу дополнительного источника питания, второй выход которого соединен с одним из выходов основного источника питания. 2. Запоминающее устройство по п.1, отличающееся тем, что . блок распределения тока содержит корректирующий конденсатор, два стабилитрона, токозадающий резистор и сглаживсиощий конденсатор, одна из обкладок которого подсоединена к катоду первого стабилитрона и выходу блока распределения тока, а через токозадающий резистор к катоду второго стабилитрона, к одной из обкладок корректирующего конденсатора и к первому входу блока распределения тЪка, аноды стабилитронов подключены ко второму входу блока распределения тока, третий вход которого соединен с другими обкладками конденсаторов. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 251004, кл. G 11 С 11/00, 1969. 2.Авторское свидетельство СССР 460577, кл. G 11 С 7/00, 1975 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| ИСТОЧНИК ПИТАНИЯ НЕЛИНЕЙНОЙ ИЛИ ЛИНЕЙНОЙ НАГРУЗКИ | 2021 |

|

RU2768272C1 |

| ТРАНЗИСТОРНЫЙ КОММУТАТОР | 2000 |

|

RU2166836C1 |

| Устройство для выбора информации из блоков памяти | 1982 |

|

SU1019491A1 |

| Импульсный стабилизатор напряжения постоянного тока | 1978 |

|

SU752286A1 |

| Устройство для управления волновым шаговым двигателем | 1989 |

|

SU1700739A1 |

| ВЫСОКОВОЛЬТНЫЙ ИМПУЛЬСНЫЙ МОДУЛЯТОР СО СТАБИЛИЗАЦИЕЙ АМПЛИТУДЫ ИМПУЛЬСОВ И ЭЛЕКТРОННЫЙ КЛЮЧ ДЛЯ НЕГО (ВАРИАНТЫ) | 2006 |

|

RU2339158C2 |

| Устройство для управления шаговым двигателем | 1982 |

|

SU1102005A1 |

| Устройство для питания разрядной короткодуговой лампы высокого давления | 1990 |

|

SU1809551A1 |

| Стабилизированный конвертор | 1979 |

|

SU892425A1 |

| Запоминающее устройство | 1976 |

|

SU608197A1 |

Г

JL

0II

гг

D

ft

Авторы

Даты

1981-02-28—Публикация

1979-05-28—Подача