1

Устройство относится к области средств статистической обработки информации и может использоваться для контроля функционирования статистических анализаторов, работающих в широких диапазонах частот.

По основному авт. св. № 392501 известно устройство, содержащее тактовый генератор, выход которого ггодключен к входу первого формирователя образцового сигнала и к входу блока формирования запаздывания, выход последнего подключен к входу второго формирователя образцового сигнала. Выходы формирователей образцового сигнала через формирователи вида корреляционной зависимости соединены с входами фильтров нижних частот, выходы которых подключены к выходам устройства. Однако в процессе контроля или проверки прибора при формировании образцового сигнала могут возникать сбои, т. е. самопроизвольные перебрасывания триггеров ступеней сдвигающего регистра, обусловленные импульсными помехами, идущими по сети. Результатом сбоя является искажение формы генерируемого образцового сигнала и его характеристик, а также изменение его периода (как правило, уменьшение). Все это влечет за собой увеличение погрешности воспроизведения образцового сигнала, которая при контроле или проверке статистического

анализатора складывается с погрешностью самого прибора.

Цель изобретения - повышение точности и надежности измерений при контроле статистических анализаторов.

Это достигается тем, что устройство для контроля статистических анализаторов снабжено блоком контроля комбинаций образцового сигнала, четыре входа которого соединены соответственно с генератором тактовых импульсов, выходами соответствующих ступеней обоих формирователей образцового сигнала и выходом блока запаздывания, а выход блока контроля комбинаций образцового сигнала подключен к шинам сброса обоих формирователей образцового сигнала устройства. Блок контроля состоит из первого счетчика, вход которого подключен к первому входу блока, а выход первого счетчика соединен с первым входом первого элемента «И, второй вход которого подключен к второму входу блока, а выход первого элемента «И через запоминающее устройство подключен к первому входу второго элемента «И, другой вход которого соединен с выходом второго счетчика, вход которого подключен к четвертому входу блока, и входом третьего элемента «И, другой вход которого соединен с третьим входом блока, а выходы второго и третьего элементов «И подключены к входам сумматора по модулю два, выход которого соединен с выходОлМ блока контроля.

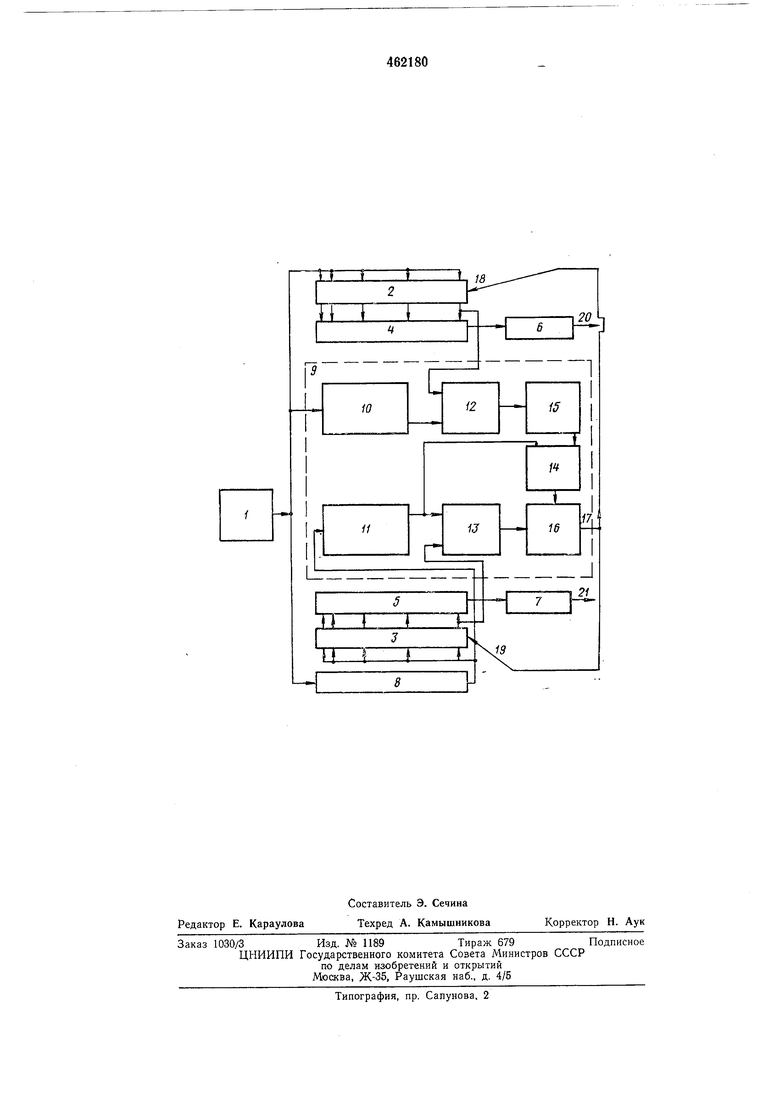

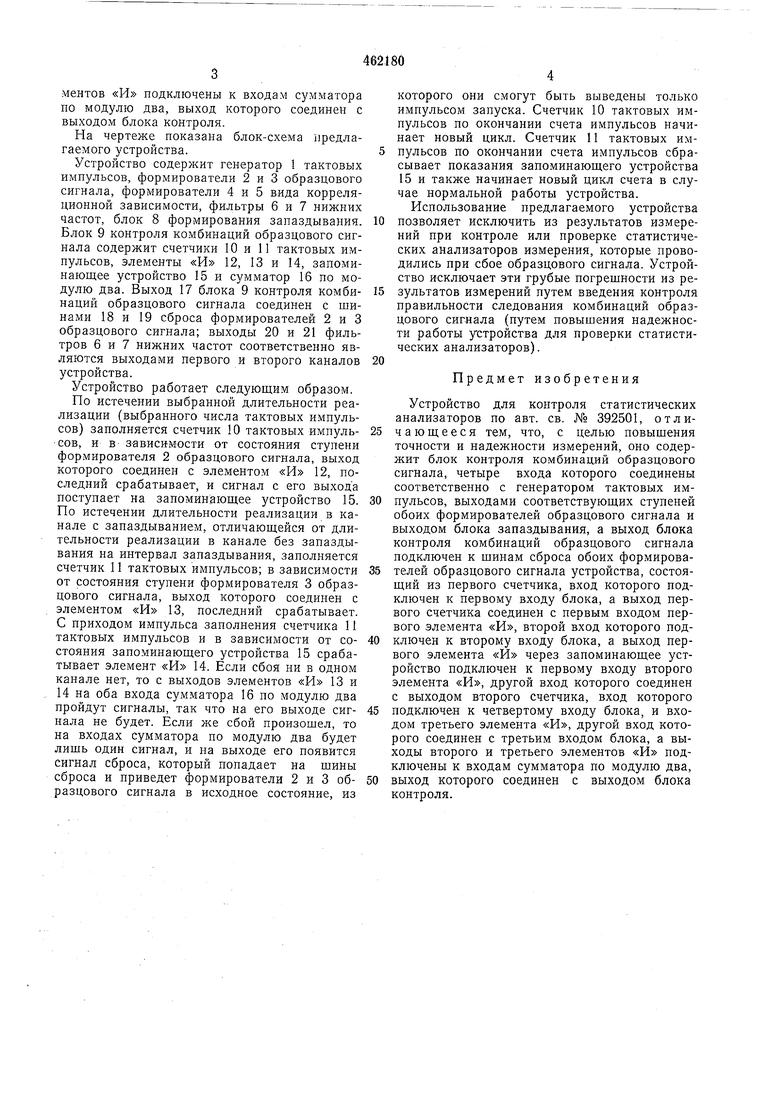

На чертеже показана блок-схема предлагаемого устройства.

Устройство содержит генератор 1 тактовых импульсов, формирователи 2 и 3 образцового сигнала, формирователи 4 и 5 вида корреляционной зависимости, фильтры 6 и 7 нижних частот, блок 8 формирования запаздывания. Блок 9 контроля комбинаций образцового сигнала содержит счетчики 10 и 11 тактовых импульсов, элементы «И 12, 13 и 14, запоминающее устройство 15 и сумматор 16 по модулю два. Выход 17 блока 9 контроля комбинаций образцового сигнала соединен с шинами 18 и 19 сброса формирователей 2 и 3 образцового сигнала; выходы 20 и 21 фильтров 6 и 7 нижних частот соответственно являются выходами первого и второго каналов устройства.

Устройство работает следующим образом.

По истечении выбранной длительности реализации (выбранного числа тактовых импульсов) заполняется счетчик 10 тактовых импульсов, и в з-ависимости от состояния ступени формирователя 2 образцового сигнала, выход которого соединен с элементом «И 12, последний срабатывает, и сигнал с его выхода поступает на запоминающее устройство 15. По истечении длительности реализации в канале с запаздыванием, отличающейся от длительности реализации в канале без запаздывания на интервал запаздывания, заполняется счетчик 11 тактовых импульсов; в зависимости от состояния ступени формирователя 3 образцового сигнала, выход которого соединен с элементом «И 13, последний срабатывает. С приходом импульса заполнения счетчика 11 тактовых импульсов и в зависимости от состояния запоминающего устройства 15 срабатывает элемент «И 14. Если сбоя ни в одном канале нет, то с выходов элементов «И 13 и 14 на оба входа сумматора 16 по модулю два пройдут сигналы, так что на его выходе сигнала не будет. Если же сбой произошел, то на входах сумматора по модулю два будет лишь один сигнал, и на выходе его появится сигнал сброса, который попадает на шины сброса и приведет формирователи 2 и 3 образцового сигнала в исходное состояние, из

которого они смогут быть выведены только импульсом запуска. Счетчик 10 тактовых импульсов по окончании счета импульсов начинает новый цикл. Счетчик 11 тактовых импульсов по окончании счета импульсов сбрасывает показания запоминающего устройства 15 и также начинает новый цикл счета в случае нормальной работы устройства.

Использование предлагаемого устройства позволяет исключить из результатов измерений при контроле или проверке статистических анализаторов измерения, которые проводились при сбое образцового сигнала. Устройство исключает эти грубые погрешности из результатов измерений путем введения контроля правильности следования комбинаций образцового сигнала (путем повышения надежности работы устройства для проверки статистических анализаторов).

Предмет изобретения

Устройство для контроля статистических анализаторов по авт. св. № 392501, отличающееся тем, что, с целью повышения точности и надежности измерений, оно содержит блок контроля комбинаций образцового сигнала, четыре входа которого соединены соответственно с генератором тактовых импульсов, выходами соответствующих ступеней обоих формирователей образцового сигнала и выходом блока запаздывания, а выход блока контроля комбинаций образцового сигнала подключен к шинам сброса обоих формирователей образцового сигнала устройства, состоящий из первого счетчика, вход которого подключен к первому входу блока, а выход первого счетчика соединен с первым входом первого элемента «И, второй вход которого подключен к второму входу блока, а выход первого элемента «И через запоминающее устройство подключен к первому входу второго элемента «И, другой вход которого соединен с выходом второго счетчика, вход которого подключен к четвертому входу блока, и входом третьего элемента «И, другой вход которого соединен с третьим входом блока, а выходы второго и третьего элементов «И подключены к входам сумматора по модулю два, выход которого соединен с выходом блока контроля.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля статистических анализаторов (его варианты) | 1982 |

|

SU1144111A1 |

| УСТРОЙСТВО для КОНТРОЛЯ СТАТИСТИЧЕСКИХ АНАЛИЗАТОРОВ | 1973 |

|

SU392501A1 |

| Двухканальный генератор образцовых случайных сигналов | 1973 |

|

SU490132A1 |

| Фотоэлектрический анализатор количества и размеров частиц | 1987 |

|

SU1518727A1 |

| Устройство для контроля статистическихАНАлизАТОРОВ | 1978 |

|

SU807339A1 |

| Устройство для приема и обработки избыточных сигналов | 1984 |

|

SU1233201A1 |

| Статистический анализатор конечной разности фазы | 1987 |

|

SU1422182A1 |

| Устройство для контроля канала связи | 1989 |

|

SU1695521A2 |

| КАРДИОМОНИТОР КВАНТИЛЬНЫЙ | 1994 |

|

RU2107455C1 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ДЛЯ ОПРЕДЕЛЕНИЯ ИНФОРМАЦИОННЫХ СВОЙСТВ ТЕСТА | 1991 |

|

RU2068580C1 |

Авторы

Даты

1975-02-28—Публикация

1973-03-19—Подача