которого соединены соответственно с первыми входами сумматоров по модулю два группы, вторые входы которых соединены соответственно с выходами элементов И группы, вьсходы сумматоров по модулю два группы соединены с входами второго элемента ИЛИ, выход которого соединен с вторым входом первого элемента ИЛИ и является выходом блока контроля образцового сигнала, соединенным с входом сброса блока задержки, информационные входы запоминающего блока образуют первую группу информационных входов блока контроля образцового сигнала, вторую группу информационных входов которого образуют вторые входы элементов И группы. I

2. Устройство для контроля статитических анализаторов, содержащее генератор импульсов, два формирователя образцового сигнала, два формирователя вида корреляционной зависимости, два фильтра нижних частот, блок задержки и блок контроля образцового сигнала, причем выход генератора импульсов соединен с информационными входами формирователя образцового сигнала и с первым входом блока задержки, первый выход которого соединен с информационными входами второго формирователя образцового сигнала, выходы первого и второго формирователей образцового сигнала соединены соответственно с входами первого и формирователей вида корреляционной зависимости соответственно, выходы которьпх соединены с входами первого и второго фильтров нижних частот соответственно, выходы которых образуют первый и второй выходы устройства соответственно, блок контроля образ.цового сигнала содержит запоминающий блок, причем выход блока контроля образцового сигнала соединен с входами сброса первого и второго формирователей образцового сигнала, отличающееся тем, что, с целью повышения производительност контроля, блок контроля образцового сигнала дополнительно содержит группу сумматоров по модулю два, группу элементов И, счетньп триггер, два формирователя импульсов и элемент ИЛИ, блок задержки содержит счетчик триггер и элемент И, выход которого является первым выходом блока задер

ки, первый вход которого соединен с первым входом элемента И и со счетным входом счетчика, выход счетчика соединен с 6 -входом триггера, с входом сброса счетчика и является вторым выходом блока задержки, который соединен с тактовым входом блока контроля образцового сигнала, второй .вход блока задержки соединен с R входом триггера, выход которого соединен с вторым входом элемента И, выходы первого и второго формирователей образцового сигнала соединены с первой и второй группами информационных входов блока контроля образцового сигна.па соответственно, тактовый вход блока контроля образцового сигнала соединен со счетным входом триггера, первый выход которого соединен через первый формирователь импульсов с входом разрешения записи запоминающего блока, информационные входы которого образуют первую группу информационных входов блока контроля образцового сигнала, второй выход триггера через второй формирователь импульсов соединен с первыми входами элементов И группы и с входом разрешения считывания запоминающего блока, выходы которого соединены соответственно с первыми входами сумматоров по модулю два группы, выходы элементов И группы соединены соответственно с вторыми входами сумматоров по модулю два группы, выходы которых соединены с входами элемента ИЛИ, выход которого является выходом блока контроля образцового сигнала и соединен с вторым входом блока задержки, вторая группа информационных входов блока контроля образцового сигнала соединен

с вторыми входами элементов И группы I

3. Устройство для контроля статистических анализаторов, содержащее генератор импульсов, два формирователя образцового сигнала, два формирователя вида корреляционной зависимости, два фильтра нижних частот, блок задержки и блок контроля образцового сигнала, причем выход генератора импульсов соединен с информационными входами первого формирователя образцового сигнала и с первым входом блока задержки, первьй вькод которого соединен с информационными входами второго формирователя образцового сигнала, выходы первого и второго формирователей образцового сигнала соединены соответственно с входами первого и второго формировате- , лей вида корреляционной зависимости соответственно,выходы котррьк соединены с входами первого и второго фильтров нижних частот соответствен- ; но, выходы которых образуют первьй и второй выходы устройства соответственно, блок контроля образцового сигнала содержит запоминающий блок и счетчик, счетный вход которого является тактовым входом блока контроля образцового сигнала, первый вькод которого соединен с входами сброса первого и второго формирователей образцового сигнала, отличающееся тем, чтр, с целью повьппения. производительности контроля, блок контроля образцового сигнала дополнительно содержит ;|;ва формирователя импульсов, группу сумматоров по модулю два, группу элементов И, .триггер и два элемента ИЛИ, блок задержки содержит счетчик, триггер и элемент И, выход которого яв- ляется первым выходом блока задержки, первый выход которого соединен с первым входом элемента И и со счетным входом счетчика, вход сброса которого является вторым входом блока задержки, ёыход счетчика блока задержки соединен с 5 -входом триггера и является вторым выходом блока задержки, который соединен с входом разрешения сравнения и с тактовым входом блока контроля образцового сигнала, третий вход блока задержки соединен с R -входом триггера, выход которого соединен с вторым входом .элемента И, вькод счетчика блока контроля образцового сигнала соединен с 6 -входом триггера,/с

11441

первым входом первого элемента ИЛИ и является вторым выходом блока контроля образцового сигнала, который соединен с вторым входом блоказадержки, вход разрешения сравн(ения блока контроля образцового сигнала соединен с R -входом триггера, пер.вЫй выход которого соединен через первьй формирователь импульсов с входом разрешения записи запо шнающего блока, информационные входы которого образуют первую группу информационных входов блока контроля образцового сигнала, второй выход триггера блока контроля образцового сигнала соединен через второй формирователь импульсов с первыми входами элементов И группы и с выходом разрешения считывания запоминаннцего блока, выходы которого соединены соответственно с первыми входами сумматоров по модулю два группы, выходы элементов И группы соединены соответственно с вторыми входами сумматоров по модулю два группы, выходы которых соединены с входами второго элемента ИЛИ, выход которого соединен с вторым входом первого элемента ИЛИ и является первым выходом блока контроля образцового сигнала, которьп соединен с третьим входом блока задержки, вторые входы элементов И группы.. образуют вторую группу информационных входов блока контроля образцового сигнала, выход первого .элемента ИЛИ которого соединен с входом сброса счетчика, первая и вторая группы информационных входов блока контроля образцового сигнала соединены с выходами первого и второго формирователей обр.азцового сигнала соответственно.

| название | год | авторы | номер документа |

|---|---|---|---|

| АВТОМАТИЗИРОВАННОЕ УСТРОЙСТВО КОНТРОЛЯ И ДИАГНОСТИРОВАНИЯ РАДИОЭЛЕКТРОННЫХ ИЗДЕЛИЙ | 1998 |

|

RU2174699C2 |

| Генератор псевдослучайных сигналов | 1986 |

|

SU1347166A1 |

| Устройство для контроля статистических анализаторов | 1973 |

|

SU462180A2 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Сигнатурный анализатор для контроля устройств памяти | 1987 |

|

SU1506449A1 |

| Устройство для контроля многоразрядных блоков оперативной памяти | 1987 |

|

SU1495854A1 |

| УСТРОЙСТВО ДЛЯ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ МНОГОКАНАЛЬНОЙ ЦИФРОВОЙ ИНФОРМАЦИИ | 1995 |

|

RU2107953C1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

| Сигнатурный анализатор | 1989 |

|

SU1756890A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ В КАНАЛЕ МНОЖЕСТВЕННОГО ДОСТУПА | 2002 |

|

RU2233038C1 |

1. Устройство для контроля статистических анализаторов, содержащее генератор импульсов, два формирователя образцового сигнала, два формирователя вида корреляционной зависимости, два фильтра нижних частот, блок задержки и блок контроля образцового сигнала, причем выход генератора импульсов соединен с первын тактовым входом блока контроля образцового сигнала, с информационными входами первого формирователя образцового сигнала и через блок задержки с вторым тактовым входом блока контроля образцового сигнала и. с, информационными входами второго формирователя образцового сигнала, выходы первого и второго формирователей образцового сигнала соединены соответственно с входами первого и второго формирователей вида корреляционной, зависимости соответственно, выходы которых соединены с входами первого и второго фильтров нижних частот соответственно, выходы которых образуют первый и второй выходы устройства соответственно, блок контроля образцового сигнала содер- , жит два счетчика и запоминающий блок, причем счетные входы первого и второго счетчиков являются первым и вторым тактовыми входами блока контроля образцового сигнала соответственно, выход блока контроля образцового сигнала соединен с входами сброса первого и второго формирователей образцового сигнала, о т л и ч а ющ е е с я тем, что, с целью повьпиения производительности контроля, блок контроля образцового сигнала дополнительно сЬдержит блок задания интервалов контроля, две схемы сравнения, группу сумматоров по мо-. (Л дулю два, группу элементов И и два элемента ИЛИ, причем выходы первого и второго формирователей образцового сигнала соедине-ы с первой и второй группами информационных входов блока контроля образцового сигнала соответственно, выходы блока 4 задания интервалов контроля соединеi( ны соответственно с первыми группами входов первой и второй схем сравнения, вторые группы входов которых соединены с выходами первого и второго счетчиков соответственно, выход первой схемы сравнения соединен с входом разрешения записи запрминающего блока и с первым входом первого элемента ИЛИ, выход которого соединен с входом сброса первого счетчика, выход второй схемы сравнения соединен с входом сброса второго счетчика, с первыми входами элементов И группы и с входом разрешения считывания .запоминающего блока, выходы

f ,

Изобретение относится к вычислительной технике и может быть использовано для автоматической проверки и контроля статистических анализаторов, в частности коррелометров.

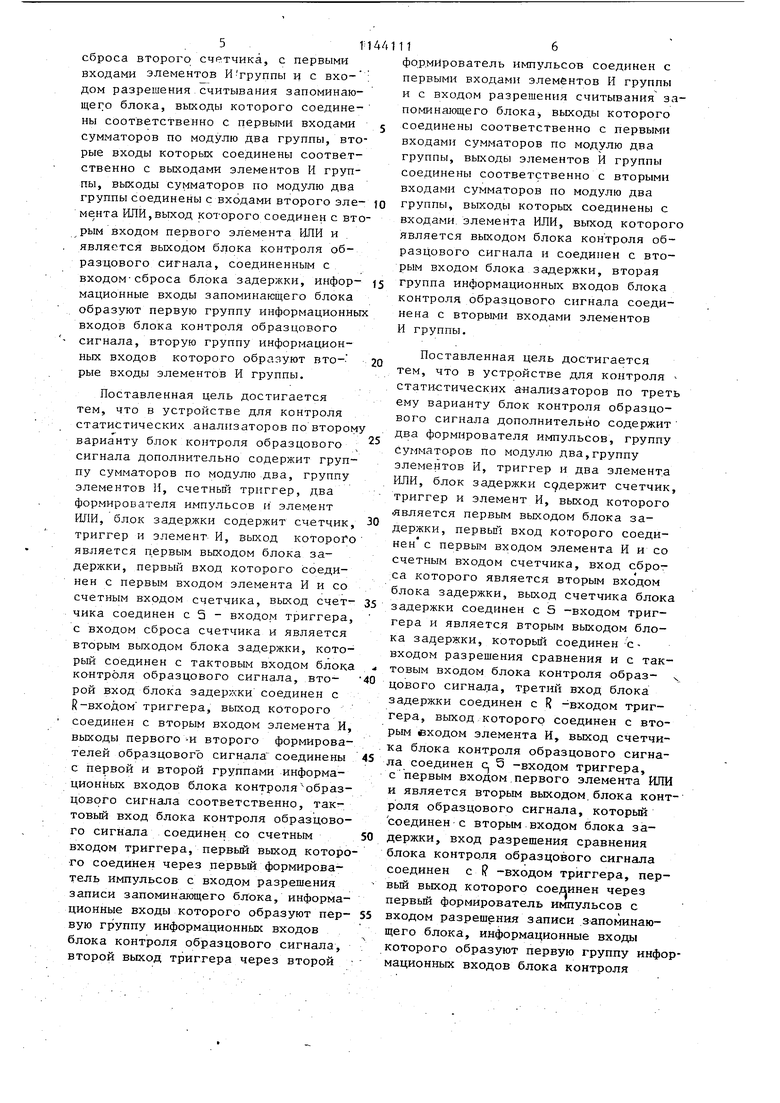

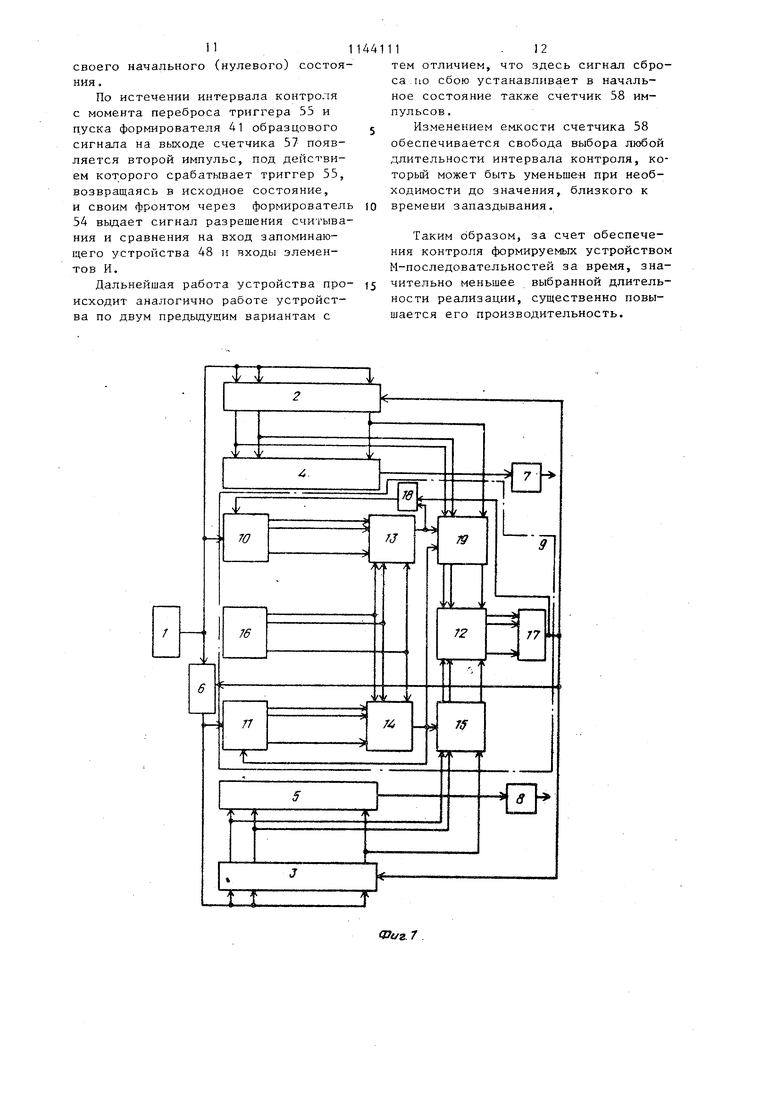

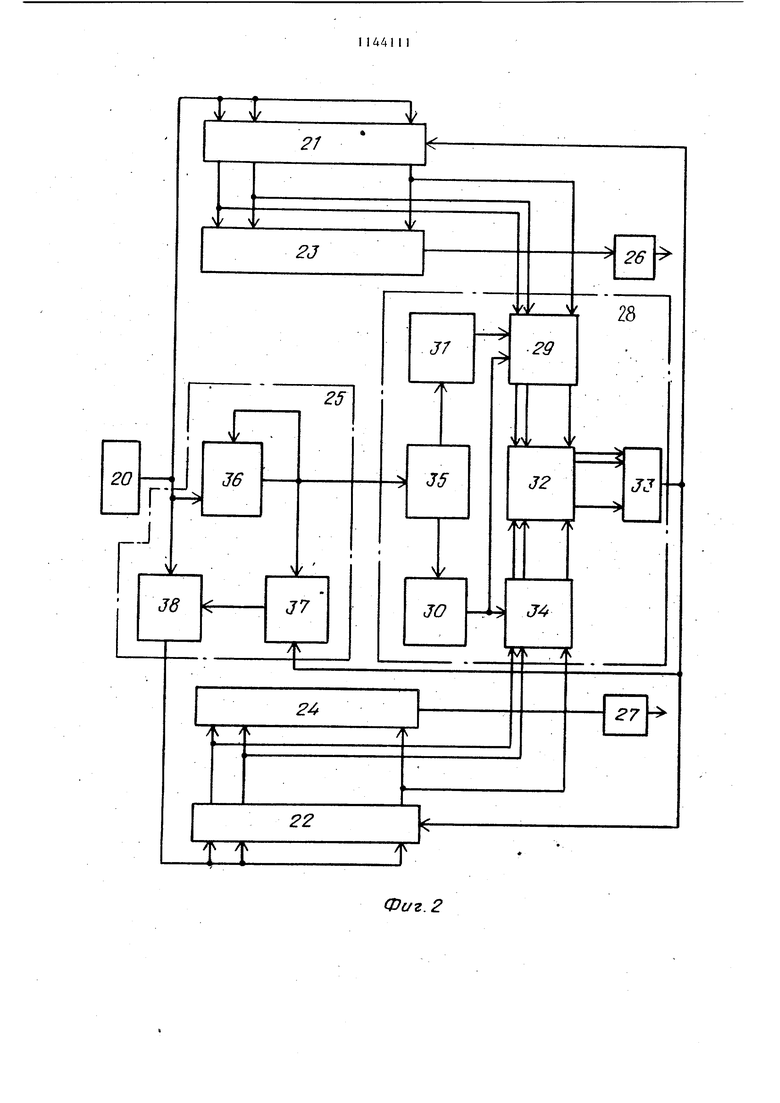

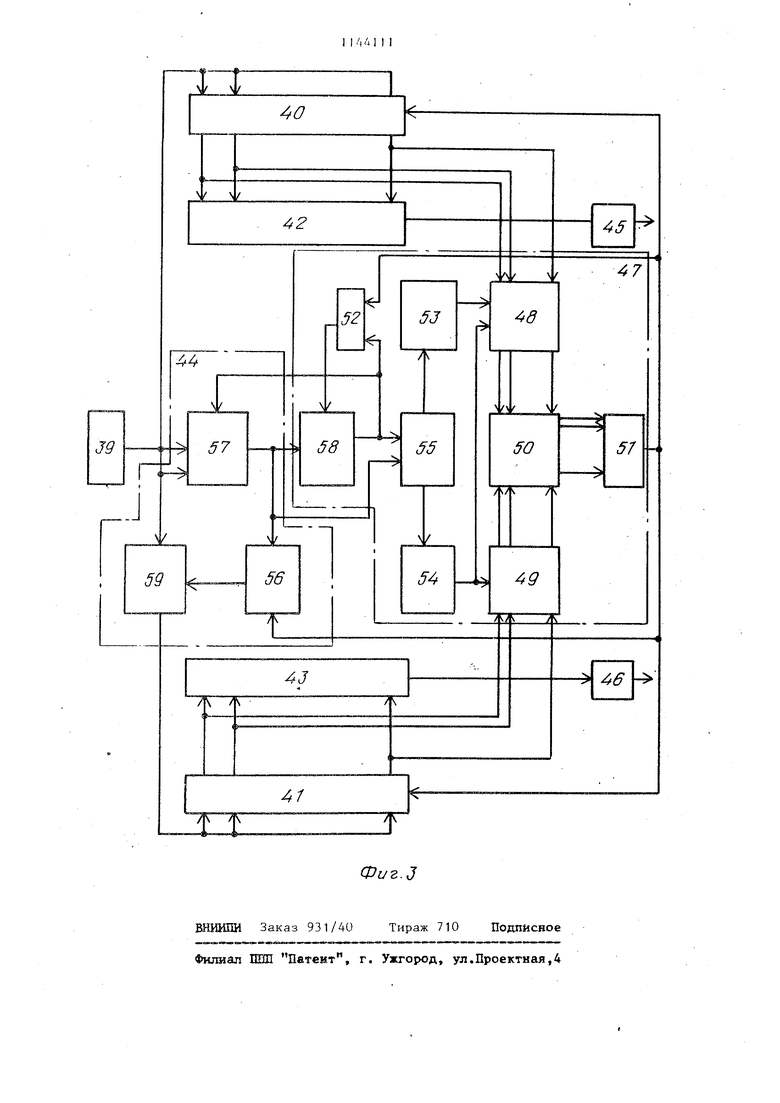

Известно устройство для контроля статистических анализаторов, содержащее два формирователя образцового сигнала, два формирователя вида корреляционной зависимости, два .фильтра нижних частот,тактовый генератор, блок формирования запаздывания, счетчик импульсов и сумматор по модулю два lj 3 Недостатком такого устройства является его низкая достоверность из-за отсутствия контроля формируемой М-последовательности, Наиболее близким по технической сущности к заявляемому является уст ройств.о для контроля статистически анализаторов, содержащее два формирователя образцового сигнала два формирователя вида корреляционной зависимости, два фильтра нижних час тот, генератор тактовых импульсов, блок запаздывания и блок контроля комбинаций образцового сигнала, чет ре входа которого соединены соответ ственно с генератором тактовых импульсов, выходами соответствующих ступеней обоих формирователей образ цового сигнала и выходом блока запаздывания, а выход блока контроля комбинаций образцового сигнала подключен к шинам сброса обоих формиро вателей образцового сигнала устройства, состоящий из первого счетчика вход которого подключен к первому входу блока, а выход первого счетчи ка соединен с первым входом первого элемента И, второй вход которого подключен к,второму входу блок а выход первого элемента И через запоминающее устройство подключен к первому входу второго элемента И, другой вход которого соединен с выходом второго счетчика, вход которо го подключен к четвертому входу бло ка, и входом третьего элемента И, другой вход которого соединен с третьим входом блока, а выходы второго и третьего элементов И подключены к входам сумматора по модулю два, выход которого соединен с выхо дом блока контроля 2. Недостатком известного устройства является низкая производительнос контроля, так как оно формирует сиг нал о сбое М-последовательности только один раз по истечении выбран ной длительности реализации, равной примерно не менее длительности одной трети М-последовательности, с.ос тавляющей десятки минут. Цель изобретения - повышение производительности контроля. Поставленная цель достигается те что в устройстве для контроля статистических анализаторов по первому варианту,содержащем генератор им114пульсов, два формирователя образцового сигнала,два формирователя вида корреляционной зависимости, два фильтра нижних частот, блок задержки и блок контроля образцового сигнала, причем выход генератора импульсов соединен с первым тактовым входом блока контроля образцового сигнала, с информационными входами первого формирователя образцового сигнала и через блок задержки - с вторым тактовым входом блока контроля образцового сигнала и с информационными входами второго формирователя образцового сигнала, выходы первого и второго формирователей образцового сигнала соединены соответственно с входами первого и второго формирователей вида корреляционной зависимости соответственно., выходы которых соединены с входами первого и второго фильтров нижних частот соответственно,выходы которых образуют первый и второй выходы устройства соответственно, блок контроля образцового сигнала содержит два счетчика и запоминающий блок, причем счетные входы первого и второго счетчиков являются первым вторым тактовыми входами блока контроля образцового сигнала соответственно, выход блока контроля образцового сигнала соединен с входами сброса первого и второго формирователей образцового сигнала, блок контроля образцового сигнала дополнительно содержит блок задания интервалов контроля, две схемы сравнения, группу сумматоров по модулю два, группу элементов И и два элемента ИЛИ, причем выходы первого и второго формирователей образцового сигнала соединены с первой и второй группами информационных входов блока контроля образцового сигнала соответственно, выходы блока задания интервалов контроля соединены соответственно с первыми группами входов первой и второй схем сравнения, вторые группы входов которых соединены с выходами первого и второго счетчиков соответственно, вькод первой схемы сравнения соединен с входом разрещения записи запоминающего блока и с первым входом первого элемента ИЛИ, выход которого соединен с входом сброса первого счетчика, выход второй схемы сравнения соединен с входом 5 .Г сброса второго) счетчика, с первыми входами элементов И-группы и с входом разрешения считывания запоминающего блока, вьсходы которого соединены соответственно с первыми входами сумматоров по модулю два группы, вто рые входы которых соединены соответственно с выходами элементов И группы, выходы сумматоров по модулю два группы соединены с входами второго эле мента ИЛИ,выход которого соединен с вт рым входом первого элемента ИЛИ и . является выходом блока контроля образцового сигнала, соединенным с входом-сброса блока задержки, информационные входы запоминающего блока образуют первую группу информационны входов блока контроля образцового сигнала, вторую группу информационных входов которого образуют вто-рые входы элементов И группы. Поставленная цель достигается тем, что в устройстве для контроля статистических анализаторов по втором варианту блок контроля образцового сигнала дополнительно содержит группу сумматоров по модулю два, группу элементов И, счетньм триггер, два формирователя импульсов н элемент ИЛИ, блок заде.ржки содержит счетчик, триггер и элемент И, выход которого является первым вькодом блока задержки, первый вход которого соединен с первым входом элемента И и со счетным входом счетчика, выход счетчика соединен с 5 - входом триггера с входом сброса счетчика и является вторым выходом блока задержки, который соединен с тактовым входом блока контроля образцового сигнала, второй вход блока задержки соединен с R-входом триггера, выход которого соединен с вторым входом элемента И выходы первого -и второго формирователей образцового сигнала соединены с первой и второй группами информационных входов блока контроля образцового сигнала соответственно, такгтовый вход блока контроля образцового сигнала соединен со счетным входом триггера, первый выход которо го соединен через первый формирователь импульсов с входом разрешения записи запоминающего блока, информационные входы которого образуют первую группу информационных входов блока контроля образцового сигнала, второй выход триггера через второй 11 6 формирователь импульсов соединен с первыми входами элементов И группы и с входом разрешения считывания запоминающего блока выходы которого соединены соответственно с первыми входами сумматоров по модулю два группы, вьЕходы элементов И группы соединены соответственно с вторыми входами сумматоров по модулю два группы, выходы которьЕХ соединены с входами элемента ИЛИ, выход которого является выходом блока контроля образцового сигнала и соединен с вторым входом блока задержки, вторая группа информационных входов блока контроля образцового сигнала соединена с вторыми входами элементов И группы. Поставленная цель достигается тем, что в устройстве для контроля статистических анализаторов по треть ему варианту блок контроля образцового сигнала дополнительно содержит два формирователя импульсов, группу сумматоров по модулю два,группу элементов И, триггер и два элемента ИЛИ, блок задержки содержит счетчик, триггер и элемент И, выход которого (Является первым выходом блока задержки, первьш вход которого соединен с первым входом элемента И и со счетным входом счетчика, вход сброса которого является вторым входом блока задержки, выход счетчика блока задержки соединен с 5 -входом триггера и является вторым выходом блока задержки, которьй соединен с входом разрешения сравнения и с тактовым входом блока контроля образ- ч цового сигнала, третий вход блока задержки соединен с R -входом триггера, выход которого соединен с вторым входом элемента И, выход счетчика блока контроля образцового сигнала соединен с 5 -входом триггера, с первым входом,первого элемента ИЛИ и является вторым выходом.блока контроля образцового сигнала, который соединен с вторым входом блока задержки, вход разрешения сравнения блока контроля образцового сигнала соединен с -входом триггера, первый выход которого соединен через первый формирователь импульсов с входом разрешения записи запоминающего блока, информационные входы которого образуют первую группу информационных входов блока контроля .711 образцового сигнала, второй выход триггера блока контроля образцового сигнала соединен через второй формирователь иг пульсов с первыми входами элементов И группы и с входом разрешения считывания запоминающего блока, выходы которого соединены соответственно с первыми входами сумматоров по модулю два группы, выходы элементов И группы соединены соответ ственно с вторыми входами сумматоров по модулю два группы, выходы которых соединены с входами второго элемента ИЛИ, выход которого соединен с вторым входом первого элемента ИЛИ и является первым выходом блока контроля образцового сигнала, которьй соединен с третьим входом блока задержки, вторые входы элементов И группы образуют вторую группу информацнонных входов блока контроля образцового сигнала, выход первого элемента ИЛИ которого соединен с вх дом сброса счетчика, первая и втора группы информационных входов блока контроля образцового сигнала соеди нены с выходами первого и второго формирователей образцового сигнала соответственно. На .фиг. 1 представлена функциональная схема устройства по первом варианту; на фиг. 2 - то же, по вто рому вариантуj на фиг. 3 - то же, по третьему варианту. Устройство по первому варианту содержит генератор 1 тактовых импул сов, формирователи 2 и 3 образцового сигнала, формирователи 4 и 5 вид корреляционной зависимости, блок 6 задержки, фильтры 7 и 8 нижних частот, блок 9 контроля образцового сигнала, счетчики 10 и 11, группу сумматоров 12 по модулю два, схемы 13 и 14 сравнения, группу элементов И 15, блок 16 задания интервалов контроля, элементы ИЛИ 17 и 18. и за поминающий блок 19. Устройство по второму варианту содержит генератор 20 тактовых импульсов, формирователи 21 и 22 обра цового сигнала, формирователи 23 и 24 вида корреляционной зависимости блок 25 задержки, фильтры 26 и 27 нижних частот, блок 28 контроля образцового сигнала, запоминающий блок 29, формирователи 30 и 31 импульсов, группу сумматоров 32 по мо дулю два, элемент ИЛИ 33, группу элементов И 34, счетный триггер 35, счетчик 36, триггер 37 и элемент И 38. Устройство по третьему варианту содержит генератор 39 тактовых импульсов, формирователи 40 и 41 образцового сигнала, формирователи 42 и 43 вида корреляционной зависимоети, блок 44задержки, фильтры 45 и 46 нижних частот, блок 47 контроля образцового сигнала, запоминающий блок 48, группу элементов И 49, группу сумматоров 50 по модулю два, элементы ИЛИ 51 и 52, формирователи 53 и 54 импульсов, триггеры 55 и 56, счетчики 57 и 58 и элемент И 59. Формирователь образцового сигнала может быть выполнен в виде регистра сдвига с обратными связями через сумматор по модулю два, а формирователь вида корреляционной зависимости - в виде цифроаналогового преобразователя. ( Устройство по первому варианту работает следукяцим образом. Тактовые импульсы с генератора 1 поступают на входы формирователя 2 образцового сигнала первого (незадержанного) канала и счетчик 10 блока 9 контроля образцового сигнала. Генерируемые М-последовательности с выходов формирователя 2 поступают на входы формирователя 4 вида корреляционной зависимости, а затем через фильтр 7 нижних частот на выход устройства. Интервал контроля задается блоком 16 в виде кода, который постоянно присутствует на входах схем 13 и 14 сравнения. Спустя время запаздывания с момента пуска и начала счета счетчиком 10 - внутри первого интервала контроля в канале без запаздьгеания начинают работать формирователь 3 образцового сигнала задержанного канала и счетчик 11. По истечении выбранной длительности контроля код счетчика 10 становится равным заданному блоком 16. коду, и на выходе схемы 1.3 сравнения формируется сигнал, по которому в запоминающий блок 19 записывается код М-последовательности, присутствующий в этом такте контроля на выходах формирователя 2. Одновременно под действием этого с.игнала. поданного через элемент 9. ИЛИ 18 на вход счетчика 10 импульсов, счетчик устанавливается в исхо мое состояние после чего снова начинает счет тактовых импульсов в следующем интервале контроля. При совпадении кода счетчика 11 кодом заданного интервала контроля на выходе схемы 14 сравнения формируется сигнал, по которому устанавливается в исходное состояние счетчик 11 и разрешается сравнение кода хранящегося в запоминающем блоке 19, с кодом, присутствующим в этом такте на выходах формирователя 3 образцового сигнала второго (задержанного) канала, В случае их несовпадения на выходе элемента ИЛИ 17 формируется сигнал сбоя, по которому устанавливаются в исходное состо ние формирователи 2 и 3, блок 6 задержки и счетчик 10. В случае отсутствия сбоя процесс формирования образцового сигнала в обоих каналах и счет тактов продолжаются аналогично описанному. Устройство по второму варианту работает следующим образом. Формирование и выдача М-последовательностей осуществляются аналогично первому варианту. По истечении выбранного интервал задержки с выхода счетчика 36 блок 25 на вхоД счетного триггера 35 в такте контроля поступает импульс, под действием которого триггер 35 срабатывает через формирователь 3-1, на вход запоминающего блока 29 подается сигнал записи кода М-последо вательности, присутствующего в этом такте на выходах формирователя 21 образцового сигнала. Одновременно на S -вход триггера 37 поступает им пульс, под действием которого этот триггер перебрасывается из начально го (нулевого) состояния, и через элемент 38 тактовые импульсы с выхо да генератора 20 поступают на входы формирователя 22 образцового сигнал а счетчик 36 возвращается в исходно состояние. По истечении двойного времени за паздьшания (с момента пуска) на вхо счетного триггера 35 в следующем такте контроля снова поступает сле дующий (второй) импульс с выхода счетчика 36 формирования запаздывания, под действием которого счетный триггер 35 перебрасывается в началь 1110 ное состояние, и своим фронтом, действующим через формирователь 30 импульсов, выдает сигнал разрешения считывания (он же сигнал разрешения сравнения) на управляющие входы запоминающего блока 29 и группы элементов И 34. Под действием этого сигнала коды - хранящийся в запоминающем блоке 29 и присутствукнций в этом такте на выходах формирователя 22 образцового сигнала - поступают одновременно на входы сумматоров 32 по модулю два группы, выходы которых объединены элементом ИЛИ 33. В случае несовпадения кодов вырабатывается сигнал сбоя и сброса в начальное состояние, поступающий на управляющие входы блока 25 и формирователей 21 и 22, Дальнейшая работа устройства происходит аналогично указанной работе устройства, при этом интервал между тактами контроля равен vдвoeннoмy запаздыванию, а запоминающий блок всегда адноадресный. Устройство по третьему варианту. работает следующим образом. Формирование и выдача М-последовательностей осуществляются айалогично двум предыдущим вариантам. По истечении выбранной длительности интервала контроля, складывающейся из времени заполнения счетчиков 37 и 58,на S -вход триггера 55 в такте контроля поступает импульс, под действием которого триггер устанавливается в единицу из начального состояния, и через формирователь 53 поступает на вход запоминающего блока 48 сигнал разрешения записи, под действием которого код М-последовательности, присутствующий в этом такте на выходах формирователя 40 образцового сигнала, записывается в 3апоминакяций блок 48. Ранее этого момента на время работы счетчика 58 по истечении времени запаздывания с момента пуска Мпоследовательности, задаваемого счетчиком 57, с его выхода на S -вход триггера 56 поступает импульс, под действием которого триггер устанавливается в единичное состояние, открывая элемент И 59 для пропускания тактовых импульсов генератора 39 на вход формирователя 41 образцового сигнала, а триггер 55 не изменяет

111

своего начального (нулевого) состояния.

По истечении интервала контроля с момента переброса триггера 55 и пуска формирователя 41 образцового сигнала на выходе счетчика 57 появляется второй импульс, под действием которого срабатывает триггер 55, возвращаясь в исходное состояние, и своим фронтом через формирователь 54 выдает сигнал разрешения считывания и сравнения на вход запоминающего устройства 48 и входы элементов И.

Дальнейшая работа устройства происходит аналогично работе устройства по двум предыдущим вариантам с

тем отличием, что здесь сигнал сброса- по сбою устанавливает в начальное состояние также счетчик 58 импульсов.

Изменением емкости счетчика 58 обеспечивается свобода выбора любой длительности интервала контроля, который может быть уменьше-н при необходимости до значения, близкого к времени запаздывания.

Таким образом, за счет обеспечения контроля формируемых устройством М-последовательностей за время, значительно меньшее . выбранной длительности реализации, существенно повышается его производительность.

Фиг. 2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| УСТРОЙСТВО для КОНТРОЛЯ СТАТИСТИЧЕСКИХ АНАЛИЗАТОРОВ | 0 |

|

SU392501A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для контроля статистических анализаторов | 1973 |

|

SU462180A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-03-07—Публикация

1982-11-23—Подача