f

(21)4302367/23-25

(22)04.09.87

(46) 30.10.89. Бюл. 40

(71)Институт технической теплофизики АН УССР

(72)В.В Шейко, А.В. Примак, А.А. Аксенов и М.П Анисимов

(53)539.215.4(088.8)

(56)Авторское свидетельство СССР № 968915, кл. G 01 N 15/02, 1980.

Авторское свидетельство СССР № 1400254, кл. G 01 N 15/02, 1988,

(54)ФОТОЭЛЕКТРИЧЕСКИЙ АНАЛИЗАТОР КОЛИЧЕСТВА И РАЗМЕРОВ ЧАСТИЦ

(57)Изобретение относится к области измерительной техники, предназначено для контроля параметров дисперсных сред и может быть использовано в металлургической, энергетической и других областях промьшшенности, Целью изобретения является повыгаеьше точности измерения за счет расширения динамического диапазона алгоритмическим путем, Устройство содержит фотодатчик, коммутатор, аналоговый сумИзобретение относится к измерительной технике, предназначено для контроля параметров дисперсных сред, и быть использовано в металлургической , знергетической и других отраслях промышлен - ности.

Целью изобретения является повышение точности измерения за счет расширения динамического диапазона алгоритмическим путем.

матор, источник образцового напряжения, накапливающиеся сумматоры, ЦАП, АЦП, задатчик цифрового кода, элементы И, вычислитель, схему И, элемент задержки, двоичные счетчики, элементы ИЛИ, D-триггер, реверсивный счетчик, дешифратор, микроЭВМ. Аналоговый сумматор- выполнен на базе операционного усилителя, инвертирующий вход которого через резистор отрицательной обратной связи соединен с выходом, а неинвертирующий вход подключен к шине нулевого потенциала. Накапливающий сумматор включает в себя задатчик, ступени цифрового кода, запоминающий регистр, сумматор, элемент задержки и элемент ИЛИ. Особенностью алгоритма работы данного анализатора является то, что сигнал на выходе АЦП изменяется незначительно - в пределах шага квантования, хотя входной сигнал фотодатчика изменяется в широких пределах от О до ид,,, в соответствии с изменением размера частиц. 1 ил

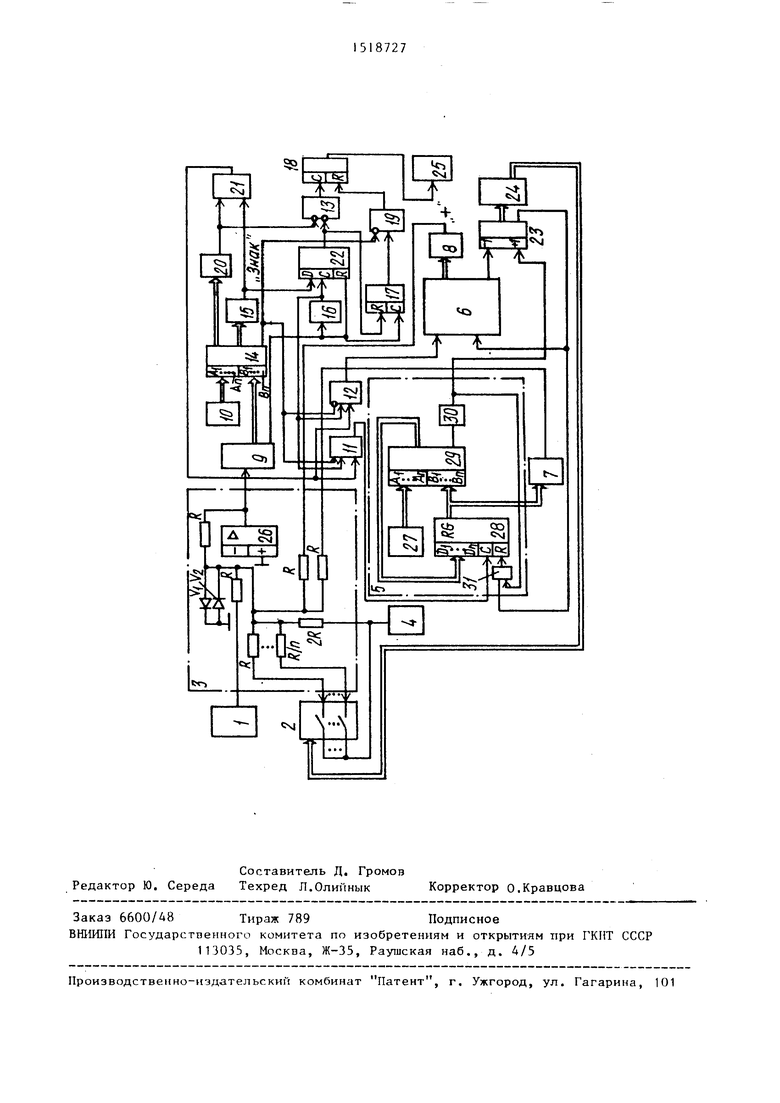

На чертеже приведена структурная схема предлагаемого устройства.

Устройство содержит фотодатчик 1, коммутатор 2, аналоговый сумматор 3, источник 4 образцового напряжения, накапливающие сумматоры 5 и 6, цифро- аналоговый преобразователь (ЦАП) 7 и 8, аналого-цифровой преобразователь (АЦП) 9, задатчик 10 цифрового кода, элементы И 11-13, блок 14 вычи- |тания, схему И 15, элемент 16 задержки, двоичные счетчики 17 и 18, элес S

(Л

СП

00 VI

to

менты ИЛИ , D-триггер 22, реверсивный счетчик 23, дешифратор 24, микроэвм 25,

Аналоговый сумматор 3 выполнен на базе операционного усилителя 26, инвертирующий вход которого через резистор R отрицательной обратной связи соединен с выходом, а неинвертирующий вход подключен к шине нулевого потенциала. При этом инвертирующий вход операционного усилителя 26 связан посредством резисторов с входами аналогового сумматора следующим образом: через разистор R - с первым, через резистор 2 R - с вторым, через резисторы R, через резисторы R/2,,,, .,,,R/n соответственно с (п+3) и (п+4 Кроме того, через параллельную цепочку из раЗНОПОЛЯрНО включенных дно-

дов инвертирующий вход усилителя подключен к шине нулевого потенциала

Накапливающий сумматор 5 включает в себя задатчик 27 ступени цифрового кода, запоминающий регистр 28, сумма- тор 29, элемент 30 задержки и элемент ИЛИ 31, причем тактовый вход запоминающего регистра 28 является тактовым входом накапливающего сумматора, выходы запоминающего регистра 28 подключены к второй группе входов сумматора 29 и являются выходами накапливающего сумматора. Первая группа входов сумматора 29 соед11Нена с выходами задатчика 27 ступени цифрового кода, а выходы этого сумматора подключены соответственно к информационным входам запоминающего регистра 28, установочный вход которого соединен с выходом элемента ИЛИ 31, один из входов которого является установочным входом накапливающего сумматора, а другой подключен к выходу элемента 30 задержки. При этом вход элемента 30 задержки подключен к дополнительному выходу сумматора 29, а выход его является выходом накапливающего сумматора Накапливающий сумматор 6 устроен аналогично.

Устройство работает следующим образом.

До запуска устройства все позиционные элементы схемы (триггеры, счетчики, регистры) находятся в нулевом состоянии о На выходе задатчика 10 устанавливается код, соответствующий цифровому эквиваленту аналогового сигнала U/2, сформт1ро- ванпого на выходе аналогового сумма

10

15

). JQ

18727

тора

3, на выходе задатчика 27 - код, соответствующий шагу квантования, причем количество подключенных выходных разрядов блока 14 вычитания к схеме И 15 также должно соответствовать шагу квантования, цифровой эквивалент которого, например, равен 1 бит. На первьй вход аналогового сумматора поступает напряжение с выхода фотодатчика 1, U, а на остальные - напряжение источника образцового напряжения U. Напряжение на выходе аналогового сумматора 3 образуется из ряда составляющих

и

Вых

Ud

R-U fg -и

R R/n

-I

Q

5

0

5

R

где +U )tUo« ,

R-II R- U

UR 2R

DR R/n

и

2

U. .

составляющая выходного сигнала фотодатчика 1 ; составляющая напряжения от второго входа аналогового сумматора} составляющая напряжения, поступающего с одного из п - выходов коммутатора 2;

составляющая напряжения сигнала образованного на выходе ЦАП 7;

-и„ -и.составляющая напряжения сигнала, образованного на выходе ЦАП 8;

±и,рщ - напряжение ошибки за счет суммарного дрейфа нуля входных сигналов операционного усилителя 26, На первом этапе работы устройства осуществляется автоподстройка смещения нуля операционного усилителя 26, При этом отсутствует информационный сигнал на выходе фотодатчика 1, разомкнуты ключи коммутатора 2, а на выходах ЦАП 7 и 8 напряжение равно нулю. Выходной сигнал операционного усилителя 26 образован двумя составляющими: от второго входа - у и сигнала опшбки ±Uouj и рагеи

Uau. ±и„„, .(2

8CIH

I иош,

аналогового сигнала. Если при этом

51

причем - равно полшкалы преобразования и выбрано для удобства автоподстройки и выбора диапазона ступени цифрового кода, которая может быть больше, чем в указанном примере, т.е. 1 бит. Автоподстройка нуля осуществляется следующим образом. АЦП 9 непрерывно с циклической последовательностью производит преобразование выходного аналогового сигнала операционного усилителя 26 в цифровой двоичный код. Время преобразования (как было указано) выбирается из условия

, В конце каждого цикла

преобразования на управляющем выходе АЦП 9 появляется короткий импульс Конец преобразования (КП), синхронизирующий работу всего устройства Блок 14 вычитания производит вычитание из текущего значения кода, поступающего на вторые входы кода, установленного на выходе цифрового за- датчика 10 и эквивалентного значению

и

2

(на этапе автоподстройки) , равно нулю, то и выходной код блока 14 вычитания равен О, а соответстве 1но блокированы элементы И 11 и И 12 и на их выходах не вьфабатываются импульсы, управляющие работой того или иного накапливающего сумматора 5 или 6 в соответствии со знаком И, , При отрицательном значении и., на ныхо- де И 11 вырабатываются по сигналу КП положительные импульсы. В этом случае работает накапливающий сумматор 5, причем он отрабатывает необходимое количество тактов в зависимости от количества ступеней, необходимых для компенсации -U. Пусть аналоговьй эквивалент ступеньки цифрового кода, равной N, установленной на выходе задатчика 27, отрабатывается схемой И 15, соответствует значению -4U, для коррекции нуля. Тогда требуемое количество i ступеней равUow Т1

но 1 . В первом такте по управляющему импульсу в регистр 28 переписывается выходное значение N сумматора 29, а на выходе ЦАП 7 формируется значение -4U, во втором такте аналогичным образом формируется значение -2ди и т.д. вплоть до значения -iuU, когда произойдет полная

7276

компенсация , с точностью до значений указанной ступени о Лпя компенсации на выходе операционного усилителя 26 Пдщ положительной полярности - аналогичным образом функционирует накапливающий сумматор 6 и НАЛ 8.

После автоподстройки нуля, на выO ходах блока 14 вычитания поддерживается нулевой код. При этом счетчик 18 может в процессе автоподстройки, когда цифровой код на выходе блока 14 вычитания изменяется ступенчато и :

5 на последней ступени срабатывает схема И 15, получит приращение 1, эквивалентное шагу KBairTounntui,, Однако дпя микроэвм 25 это значение не является И1{формативным и оно не принима0 ется для вычисления. 1

В процессе измерения диаметра движущейся частицы включается в работу фотодатчик I и при прохождении этой

5 частицей счетной зоны MOHOTCI . JO возрастает выходно1 сигнал операционного усилителя 26 от О до +U, В соответствии с измене1шем U ияменяется выходной код А1ДП 9. В результате вычиQ тания на информационных выходах блока 14 вычитания формируется модуль разности, а на знаковом выходе - знак разности кодов задатчика 10 и выходного кода АЦП 9. В процессе вхождения частицы знак разности име ет высокий логический уровень, блоки- р тощий входы элементов ИЛИ 19 и И 12 и разрешающий вход элемента И 11„ По достижению разности этих кодов значения указанной ступеньки срабатывает схема И 15, а через некоторое вре- мя, необходимое на установление на ее выходе сигнала высокого логического уровня по фронту задержанного импульса КП, производится запись этого сигнала в D-триггер 22, работающий как триггер - защелка. В результате этого D-триггер 22 изменяет свое состояние из П в 1. Парал.пйльно с

0

5

этим въфабатывается задержанный импульс КП на выходе элемента И 11 и осуществляет запись в запоминающий регистр) 28 выходного кода сумматора 29, соо.тветствующий значению ступени AN. На выходе ЦАП 7 при этом вырабатывается аналоговый эквивалент -ЛИ цифровой ступени ЛН, компеь сирующий приращение вьсходного сигнала фотодатчика 1 .

В следующий момент времени по срезу импульса КГ1 D-триггер 22 возвращается в исходное положение, а счетчик 18 получает приращение I

Очередное приращение аналогового сигнала U до значения, равного цифровому эквиваленту /3 N, вызывают указанные выше действия. При этом компенсирующее выходное напряжение ЦАП 7 становится равным -24U , счетчик 18 получает приращение 1 2, что соответствует значению d, и учитывается микроэвм 25.

В процессе работы после отработ- ки 256 ступени сумматор 29 вырабатывает на выходе сигнал переполнения, по которому обнуляется регистр 28, выход ЦАП 7 устанавливается в О, а -реверсивный счетчик 23 получает при- ращение 1, в результате чего с помощью дешифратора 24 подключается па- пряжение -и образцового источника 4 через первый канал коммутатора 2 к третьему входу аналогового суммато- ра 3. При этом компенсирующее напряжение входного сигнала, пересчитанное на выход операционного усилителя 26, равно значению U.

Таким образом, на выходе ЦАП 7 на- пряжение изменяется ступенчато с размером ступеньки в бит, а на п выходах коммутатора - с размером ступени бит.

После срабатывания последнего ка- нала коммутатора вырабатывается компенсирующее напряжение (ли 256) Счетчик 18 при этом регистрирует двоичный код, равный (256n+i) бит, что пересчитывается микроЭВМ 25 в значе- ние диаметра, равное 100 мкм Вместе с тем, выходное напряжение операционного усилителя 26 изменяется в узком интервале +11+JU, где п - количество подключенных входов схемы И 15, что исключает ошибку, связанную с нелинейностью характеристики АЦП 9, С момента полного вхождетгя частицы в счетную зону коммутатора 2, блока 14 вычитания, ЦАП 17, операционный уси- литель 26, D-триггер 22 и счетчик 18 сохраняют указанные состояния. По третьему сигналу КП счетчик 17 на выходе вырабатывает сигнал переполнения, а счетчик 18 устанавливается в О, Микроэвм 25 запоминает соответствующее значение для частицы. С момента выхода частицы из счетной зоны на знаковом выходе блока 14 вычитания устанавливггется О, блокирует элемент И II и счетчик 18, по открывает элемент И 12. При этом аналогично указанному работает накапливающий сумматор 6 и ЦАП 8, а реверсив- ньй счетчик 23 получает вычитание 1„ После отработки последней п ступени Все каналы коммутатора выключены и если значение , зафиксированное на выходе ЦАП 7, не компенсируется iнапряжением на выходе ЦАП 8, то тогда при следующем сигнале вычитания реверсивный счетчик 23 вырабытывает сигнал на дополнительном выходе, посредством которого устанавливаются в О ЦАП 7 и ЦАП 8. ,Цо появления следующей частицы осуществляется автоподстройка нуля о

Если в процессе работы устройства возникает сбой, т.е. не отрабатываются в соответствии с указанным алгоритмом ступени приращения выходного кода ЦАП 9, то на выходе элемента ИЛИ 21 вырабатывается сигнал высокого логического уровня, регистрируемый как сигнал Авария,

Формула изобретения

Фотоэлектрический анализатор количества и размеров частиц, содержащий фотодатчик, аналого-цифровой преобразователь, блок вычиташш, D-триггер, элемент задержки, первый элемент И, первый элемент ИЛИ, первый и второй двоичные счетчики и микроЭБМ, причем информационгше выходы аналого-цифрового преобразователя подключены к первой группе входов блока вычитания первая группа выходов которого соединена с входаж- первого элемента И, управляющий выход аналого-цифрового преобразователя подключен к установочному, а также через элемент задержки - к тактовому входам 1 -триГ- гера, информационный вход которого соединен с выходом схемы И, а выход подключен к установочному входу первого двоичного счетчика, выход которого соединен с первым входом первог элемента ИЛИ, второй вход которого подключен к дополнительному выходу блока вычитания, выход первого элемента ИЛИ соединен с установочным входом второго двоичного счетчика, выходы которого подключены к входам микроэвм, а управляющий выход аналого-цифрового преобразователя сое 1

динен с входом первого двоичного счетчика, отличающийся тем, что, с целью повышения точности измерения за счет расширения динамического диапазона алгоритмическим путем, он дополнительно снабжен аналоговым сумматором, коммутатором, источником образцового напряжения, первым и .вторым накапливающими сумматорами, вторыми, третьим и четвертым элементами И, первым и вторым цифро- аналоговыми преобразователями, за- датчиком цифрового кода, вторым и третьим элементами ИЛИ, реверсивным счетчиком и дешифратором, при этом выход фотодатчика соединен с первым, выход источника образцового напряжения - с вторым, а п выходов коммутатора - с п+2 входами аналогового сумматора, выход которого подключен к входу аналого-цифрового преобразователя, п информационных входов коммутатора соединены с выходом источника образцового напряжения, выходы задатчика цифрового кода соединены с второй группой входов блока вычитания, вторая группа выходов которого подключена к входам второго элемента ИЛИ, дополнительный выход блока вычитания подключен к первому входу второго элемента И и к первому инверсному входу третьего элемента И, выход элемента задержки подключен к вторым входам второго и третьего эле872710

ментов И, выход третьего элемента ИЛИ соединен с третьими входами второго и третьего элементов И, выходы которого подключены соответственно к тактовым входам первого и второго накапливающих сумматоров, группы информационных выходов которых соединены соответственно с входами первого

0 и второго цифроаналоговых преобразователей, а управляющие выходы первого и второго накапливающих сумматоров подключены соответственно к входам сложения и вычитания реверсив5 ного счетчика, выход реверсивного счетчика соединен с входом дешифратора, выход которого подключен к управляющим входам коммутатора, выходы первого и второго цифроаналоговых

0 преобразователей соединены соответственно с п+3 и п+4 входами аналогового сумматора, выход первого элемента И с оединен с первым входом третьего элемента ИЛИ, второй вход кото5 рого подключен к выходу второго элемента ИЛИ и одновременно к первому входу четвертого элемента И, второй вход которого соединен с выходом D-триггера, выход четвертого элемен-

0 та И подключен к счетному входу второго двоичного счетчика, а дополнительный выход реверсивного счетчика соединен с установочными входами первого и второго накапливающих суммато ров.

| название | год | авторы | номер документа |

|---|---|---|---|

| АЦП С ПЕРИОДИЧЕСКОЙ ПОДСТРОЙКОЙ ПОСТОЯННОЙ СОСТАВЛЯЮЩЕЙ | 2001 |

|

RU2198463C1 |

| Аналого-цифровой преобразователь с автоматической коррекцией функции преобразования | 1988 |

|

SU1667246A1 |

| Устройство двухступенчатого аналого-цифрового преобразования | 1985 |

|

SU1266003A1 |

| Устройство для контроля аналого-цифровых преобразователей | 1984 |

|

SU1236609A1 |

| Устройство для контроля объектов | 1990 |

|

SU1725233A1 |

| Формирователь повторяющихся частотно-модулированных сигналов | 1988 |

|

SU1555806A1 |

| Устройство для измерения дрейфа аналого-цифровых преобразователей | 1981 |

|

SU991599A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1562971A1 |

| Устройство регулирования электрической мощности переменного тока | 1991 |

|

SU1830523A1 |

| Интерполирующий фильтр | 1982 |

|

SU1100715A1 |

Изобретение относится к области измерительной техники, предназначено для контроля параметров дисперсных сред и может быть использовано в металлургической энергетической и других областях промышленности. Целью изобретения является повышение точности измерения за счет расширения динамического диапазона алгоритмическим путем. Устройство содержит фотодатчик, коммутатор, аналоговый сумматор, источник образцового напряжения, накапливающиеся сумматоры, ЦАП, АЦП, задатчик цифрового кода, элементы И, вычислитель, схему И, элемент задержки, двоичные счетчики, элементы ИЛИ, Д-триггер, реверсивный счетчик, дешифратор, микро-ЭВМ. Аналоговый сумматор выполнен на базе операционного усилителя, инвертирующий вход, которого через резистор отрицательной обратной связи соединен с выходом, а не инвертирующий вход подключен к шине нулевого потенциала. Накапливающий сумматор включает в себя задатчик, ступени цифрового кода, запоминающий регистр, сумматор, элемент задержки и элемент ИЛИ. Особенностью алгоритма работы данного анализатора является то, что сигнал на входе АЦП изменяется незначительно - в пределах шага квантования, хотя входной сигнал фотодатчика изменяется в широких пределах от 0 до Имакс в соответствии с изменением размера частиц. 1 ил.

Авторы

Даты

1989-10-30—Публикация

1987-09-04—Подача