Изобретение относится к области автоматики и вычислительной техники и может быть 1;рименено в резервироваииых цифровых устройствах.

Известен мажоритарный триггер, состоящий из мажоритарного элемента инвертора и п идентичных каналов, каждый из которых содержит резервный триггер со схемой «ИЛИ на счетном входе и схемой «И иа каждом из выходов, причем ко вторым входам схем «И подключен выход источника сдвинутых тактовых импульсов, а выходы схем «И соединены со входами схемы ИЛИ, к одному из входов которой подключен также выход источника входных импульсов.

Цель изобретения - повышение иадежиости работы устройства и. расширения функциональных возможностей.

Для этого в него дополнительно введены п -4 мажоритарных элементов и инверторов, при этом каждый вход любого мажоритарного элемента соединен с аналогичными входами других мажоритарных элементов и подключен к неинверсиому выходу резервного триггера соответствующего канала, а выход мажоритарного элемента непосредственно и через инвертор соединен со входами схем «И соответствующего канала.

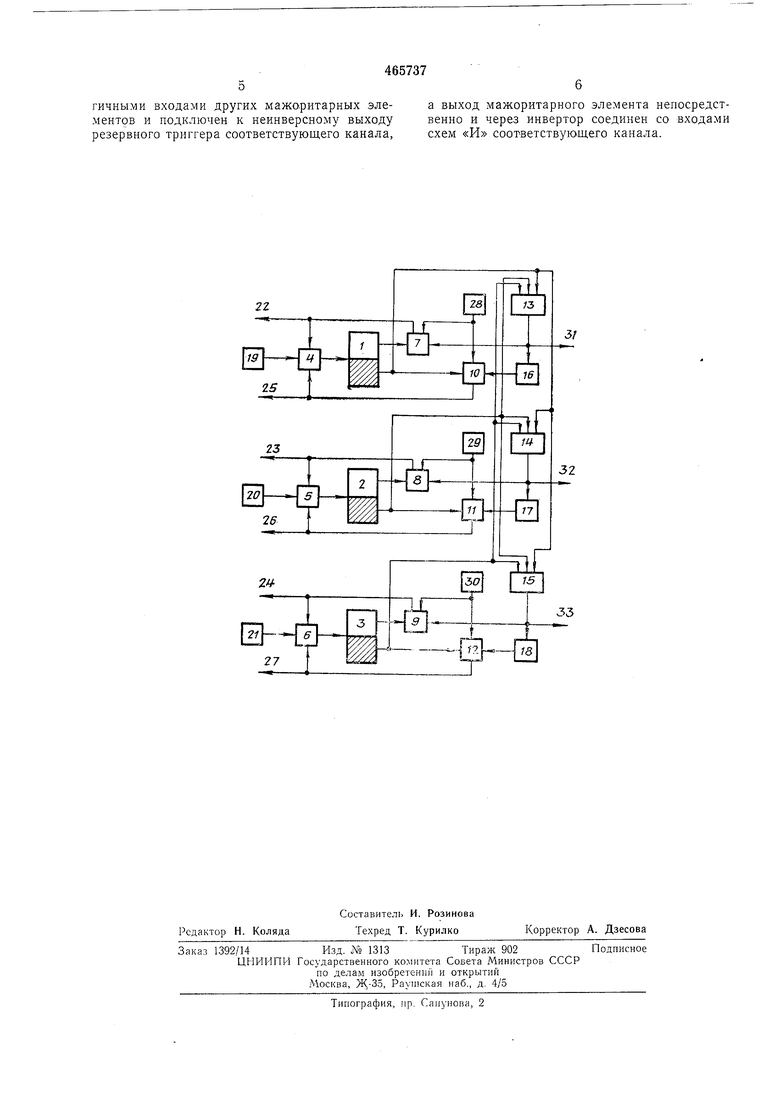

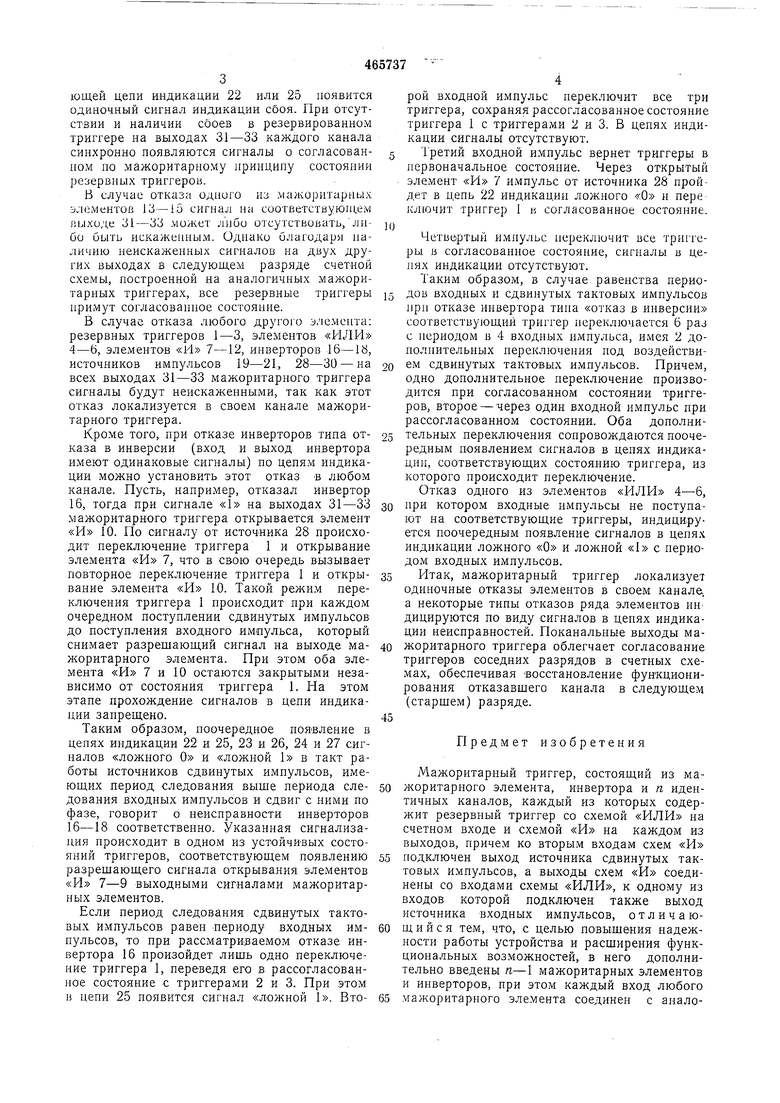

На чертеже представлена блок-схема мажоритарного триггера, содержащего резервпые триггеры I-3, элементы «ИЛИ 4-6, на счетных входах триггеров, элементы «И 7- 9 для обнаружения отказа типа «ложный О, элементы «И 10-12 для обнаружения отказа типа «ложная 1, мажоритарные элементы 13-15, инверторы 16-18, источники входных сигналов 19-21, . цепи 22-24 индикации «ложного О и цепи 25-27 индикации «ложной 1 на входах резервных триггеров 1-3 соответственно, источники 28-30 вторых (сдвинутых) тактовых импульсов, выходы 31-33 мажоритарного триггера.

При согласованном состоянин всех резервных триггеров 1-3 элементы «И 7-12 закрыты для прохождения сдвинутых тактовых импульсов от источников 28-30, так как на входы элементов «PI с триггеров и мажоритарных элементов поступают сигналы в противофазе.

Поэтому в этом случае схема устойчиво сохраняет свое состояние. При сбое одного из резервных триггеров, например триггера 1 (в зависимости от фазы сбоя: при переключении из состояния «1 в состояние «О или наоборот) на входах соответствующих элементов 7 или 10 окажутся синфазные сигналы, благодаря чему импульс источника 28 поступает через элемент «ПЛИ на вход сбившегося триггера 1 и переводит его в согласованпое состояние. При этом в соответствующей цепи индикации 22 или 25 появится одиночный сигнал индикации сбоя. При отсутствии и наличии сооев в резервированном триггере на выходах 31-33 каждого канала синхронно появляются сигналы о согласованном но мажоритарному принципу состоянии резервных триггеров.

Б случае отказа одного из малсоритарны.к элементов 13-15 сигнал на соответствую1цем выходе 31-33 может либо отсутствовать, ли00 быть искажеаным. Однако благодаря наличию неискаженных сигналов на двух других выходах в следующем разряде счетной схемы, построенной на аналогичных мажоритарных триггерах, все резервные триггеры примут согласованное состояние.

В случае отказа любого другого элемента: резервных триггеров 1-3, элементов «ИЛИ 4-6, элементов «И 7-12, инверторов 16-18, источников имнульсов 19-21, 28-30 - на всех выходах 31-33 мажоритарного триггера сигналы будут неискаженными, так как этот отказ локализуется в своем канале мажоритарного триггера.

Кроме того, при отказе инверторов тина отказа в инверсии (вход и выход инвертора имеют одинаковые сигналв) но ценям индикации можно установить этот отказ -в любом канале. Пусть, например, отказал инвертор 16, тогда при сигнале «1 на выходах 31-33 мажоритарного триггера открывается элемент «И 10. По сигналу от источника 28 происходит переключение триггера 1 и открывание элемента «И 7, что в свою очередь вызывает повторное иереключение триггера 1 и открыванне элемента «И 10. Такой режим переключения триггера 1 происходит при каждом очередном поступлении сдвинутых импульсов до поступления входного импульса, который снимает разрешающий сигнал на выходе мажорнтарного элемента. При этом оба элемента «И 7 и 10 остаются закрытыми независимо от состояния триггера 1. На этом этане прохождение сигналов в цени индикации занрещено.

Таким образом, поочередное появление в цепях индикации 22 и 25, 23 и 26, 24 и 27 сигналов «ложного О и «ложной 1 в такт работы источников сдвинутых импульсов, имеющих период следования выще периода еледования входных импульсов и сдвиг с ними по фазе, говорит о неисправности инверторов 16-18 соответственно. Указанная сигнализация происходит в одном из устойчивых состояний триггеров, соответствующем появлению разрешающего сигнала открывания элементов «И 7-9 выходными сигналами мажоритарных элементов.

Если период следования сдвинутых тактовых импульсов равен лериоду входных импульсов, то при рассматриваемом отказе инвертора 16 произойдет лишь одно переключение триггера 1, переведя его в рассогласованное состояние с триггерами 2 и 3. При этом в цепи 25 появится сигнал «ложной 1. Второй входной импульс переключит все три триггера, сохраняя рассогласованное состояние триггера 1 с триггерами 2 и 3. В цепях индикации сигналы отсутствуют.

Третий входной и.мпульс вернет триггеры в первоначальное состояние. Через открытый элемент «И 7 импульс от источника 28 пройдет в цепь 22 индикации ложного «О и пере ключит триггер 1 в согласованное состояние.

Четвертый импульс нереключит все триггеры в согласованное состояние, сигналы в цепях индикации отсутствуют.

Таким образом, в случае равенства периодов входных и сдвинутых тактовых импульсов при отказе инвертора тина «отказ в инверсии соответствующий триггер переключается 6 раз с нериодом в 4 входных импульса, имея 2 дополнительных нереключения под воздействием сдвинутых тактовых импульсов. Причем, одно дополнительное переключение производится при согласованном состоянии триггеров, второе - через один входной импульс при рассогласованном состоянии. Оба дополнительных переключения сопровождаются поочередным появлением сигналов в цепях индикации, соответствующих состоянию триггера, из которого происходит переключение.

Отказ одного из эле.ментов «ИЛИ 4-6, при котором входные импульсы не поступают на соответствующие триггеры, индицируется поочередным появление сигналов в цепях индикации ложного «О и ложной «1 с нериодом входных импульсов.

Итак, мажоритарный триггер локализует одиночные отказы элементов в своем канале., а некоторые типы отказов ряда элементов индицируются по виду сигналов в цепях индикации неисправностей. Поканальные выходы мажоритарного триггера облегчает согласование триггеров соседних разрядов в счетных схемах, обеспечивая восстановление функционирования отказавшего канала в следующем (старщем) разряде.

Предмет изобретения

Мажоритарный триггер, состоящий из мажоритарного элемента, инвертора и п идентичных каналов, каждый из которых содержит резервный триггер со схемой «ИЛИ на счетном входе и схемой «И на каждом из выходов, причем ко вторым входам схем «И подключен выход источника сдвинутых тактовых импульсов, а выходы схем «И соединены со входами схемы «ИЛИ, к одному из входов которой подключен также выход источника входных импульсов, отличающийся тем, что, с целью повышения надежности работы устройства и расширения функциональных возможностей, в него дополнительно введены п-1 мажоритарных элементов и инверторов, при этом каждый вход любого мажоритарного элемента соединен с аналогичными входами других мажоритарных элементов и подключен к неинверсному выходу резервного триггера соответствующего канала,

а выход мажоритарного элемента непосредственно и через инвертор соединен со входами схем «И соответствующего канала.

| название | год | авторы | номер документа |

|---|---|---|---|

| ВСЕСОЮЗНАЯ I'ilVief? г; -п.п.. ..,,-, J .4^ iSc.i •; .. ,-..v-, ,, .:.i;...»fj | 1971 |

|

SU318945A1 |

| Устройство для управления @ -фазным преобразователем | 1983 |

|

SU1290463A1 |

| ВСЕСОЮЗНАЯ ПА:ГЕ11иЛ-Гсл,:^Л5НАЯ 6иблиотеиа_№_А____РЕЗЕРВ^ | 1970 |

|

SU282422A1 |

| Резервированный счетчик | 1982 |

|

SU1040603A1 |

| Трехканальное резервированноеуСТРОйСТВО для СиНХРОНизАции СигНАлОВ | 1979 |

|

SU822187A1 |

| Трехканальная резервированная микропроцессорная система | 1985 |

|

SU1378287A1 |

| Программное устройство | 1977 |

|

SU734646A1 |

| Трехканальный резервированныйРАСпРЕдЕлиТЕль иМпульСОВ | 1978 |

|

SU798848A1 |

| Мажоритарный триггер | 1976 |

|

SU644042A1 |

| Резервированный счетчик импульсов | 1981 |

|

SU987815A1 |

22

Авторы

Даты

1975-03-30—Публикация

1973-12-11—Подача