Изобретение относится к вычислительной технике и может быть использовано при построении высоконадежных вычислительных управляющих систем.

Цель изобретения - расширение функциональных возможностей системы, повышение ее надежности и контролепригодности.

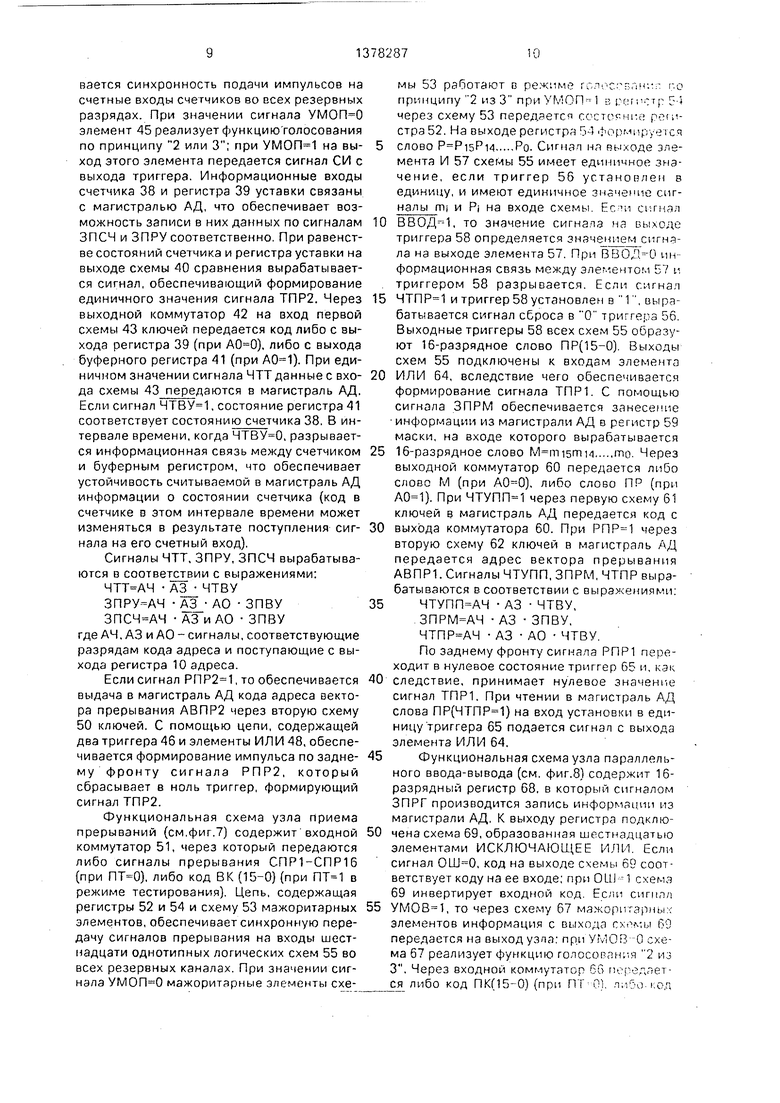

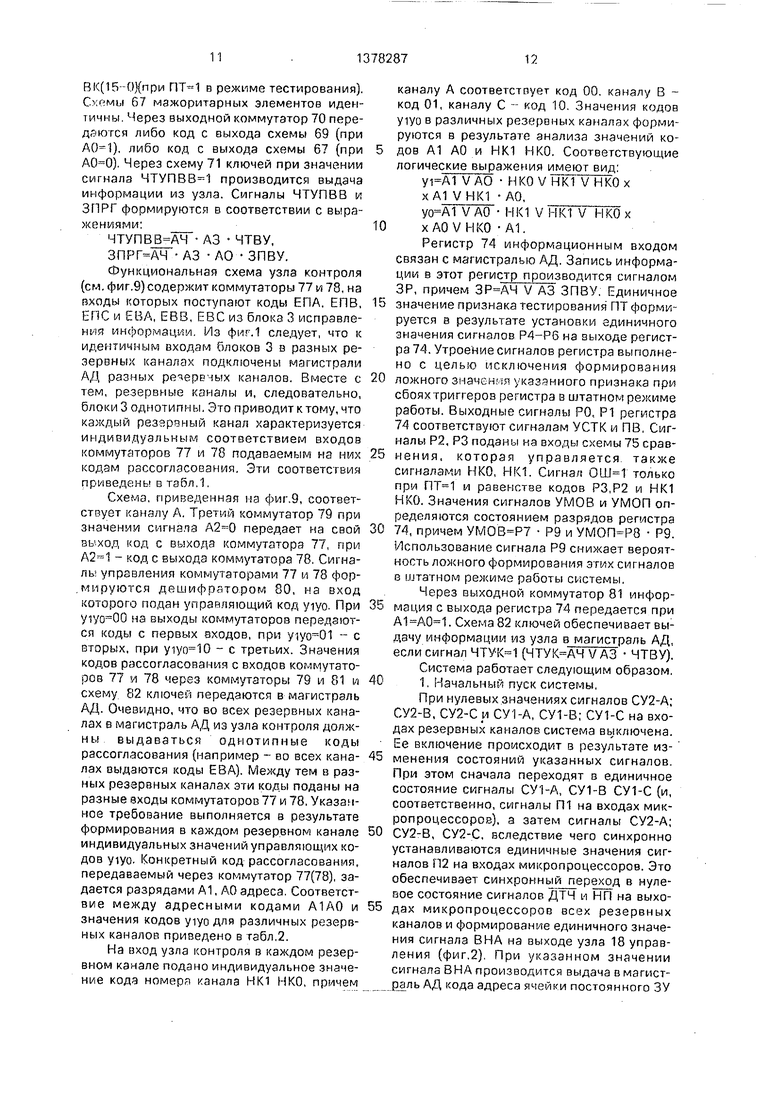

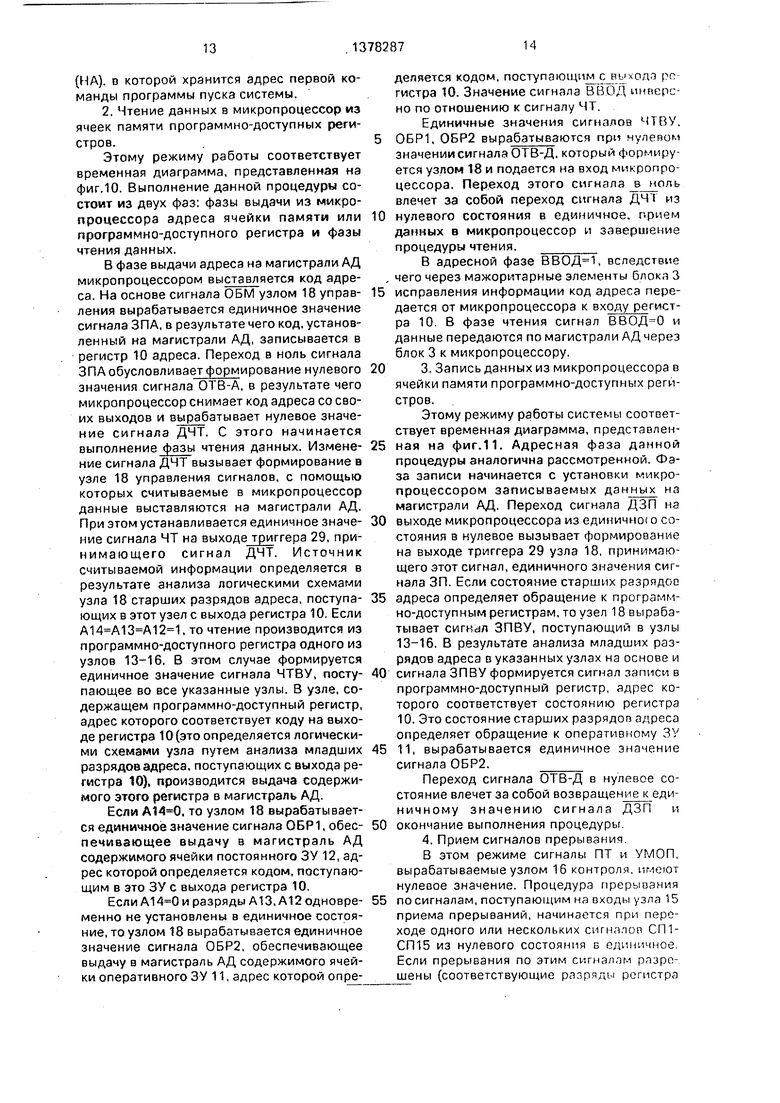

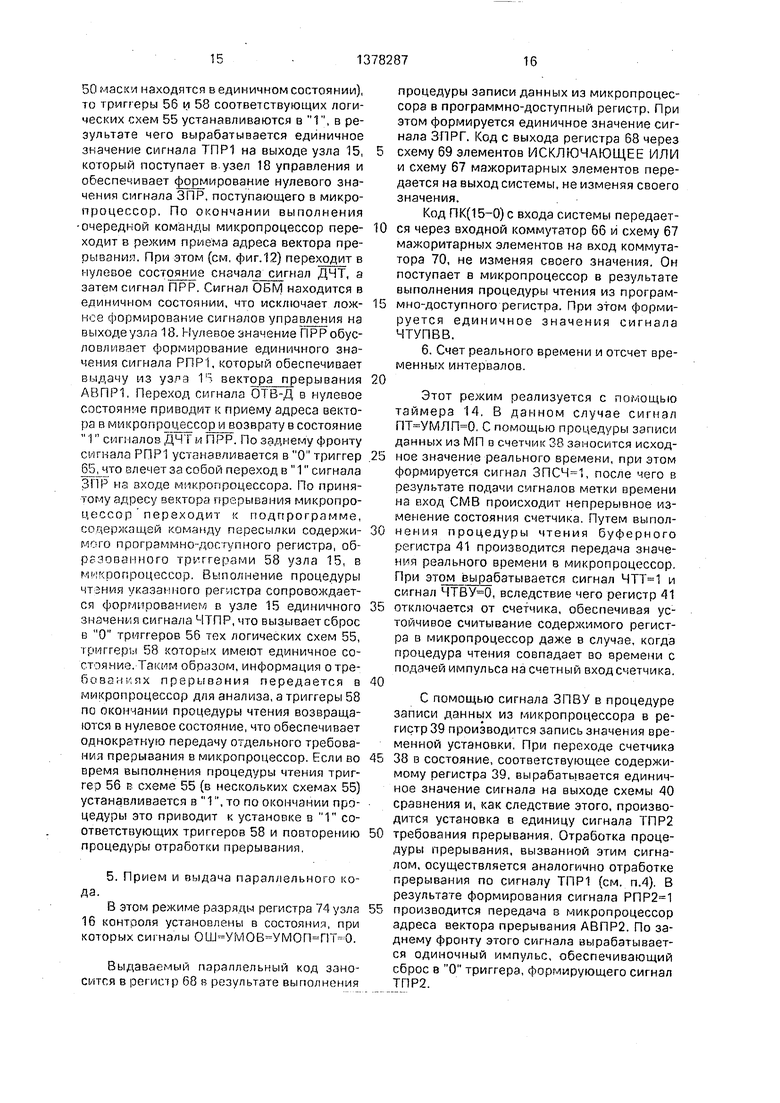

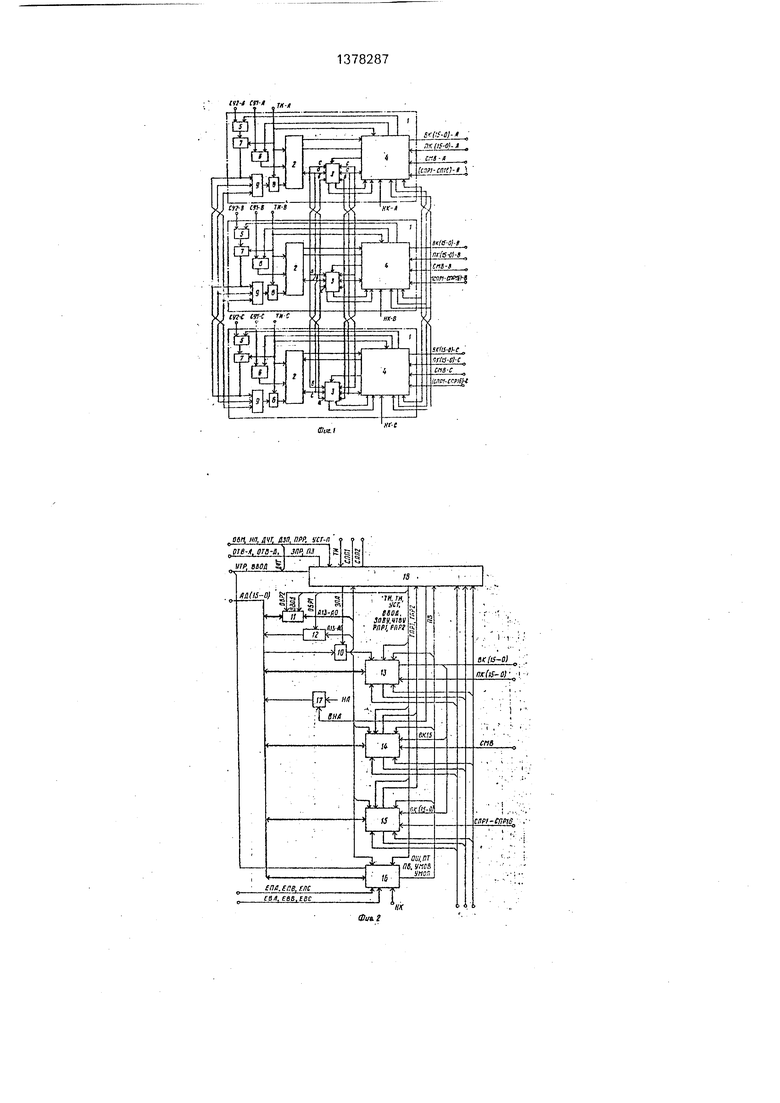

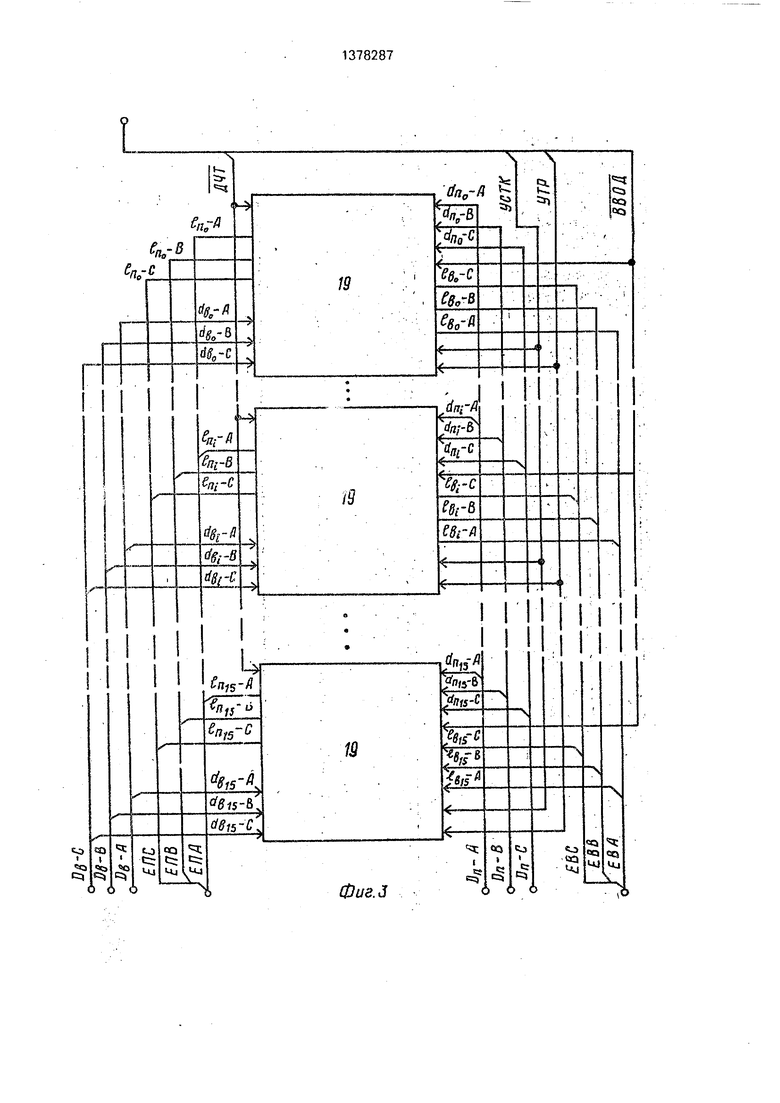

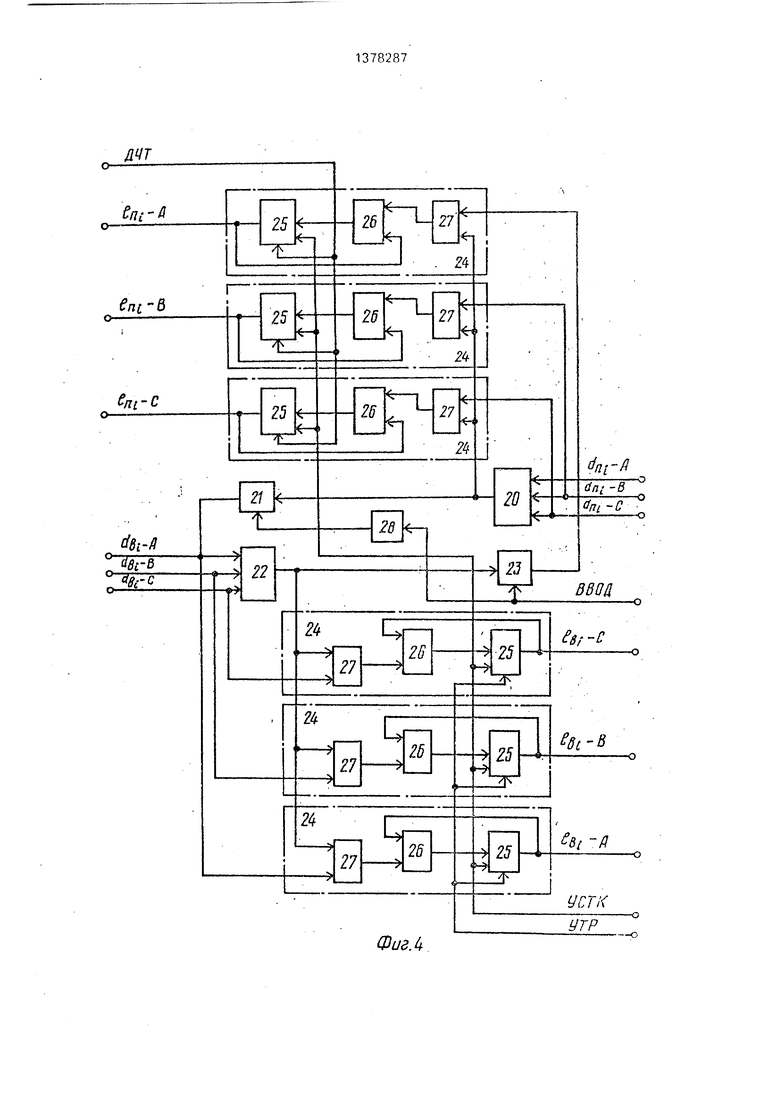

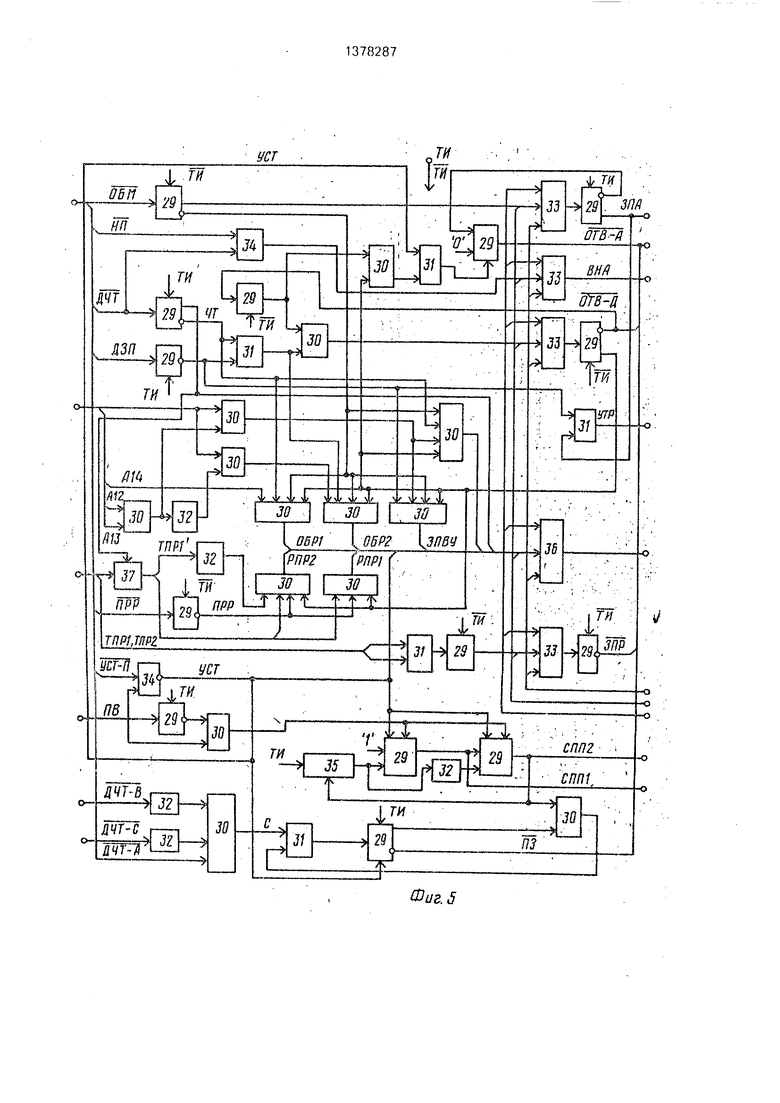

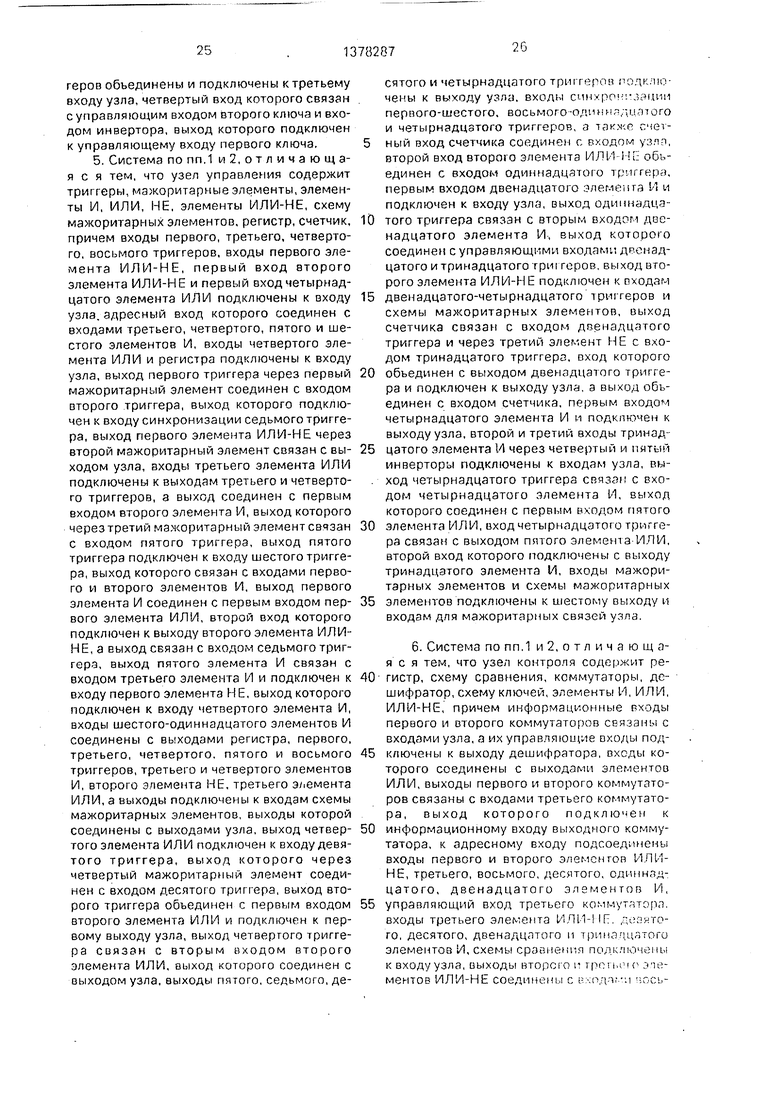

На фиг.1 приведена блок-схема предлагаемой системы; на фиг.2 - блок-схема блока памяти и внешнего сопряжения; на фиг.З - блок-схема блока исправления информации; на фиг.4 - функциональная схема однозарядного узла исправл ения информации; на фиг.5 - функциональная схема узла управления; на фиг.6 - функциональная схема таймера; на фиг.7 - функциональная схема узла приема прерываний; на фиг.8 - функциональная схема узла параллельного ввода-вывода; на фиг.9 - функциональная схема узла контроля; на фиг. 10 временная диаграмма работы системы в режиме чтения данных в микропроцессор; на фиг.11 - временная диаграмма работы системы в режиме записи данных, выдаваемых из микропроцессора; на фиг. 12 - временная диаграмма работы микропроцессора в режиме прерывания.

Система включает три однотипных резервных канала Т, каждый из которых содержит микропроцессор 2, блок 3 исправления информации, блок 4 памяти и внешнего сопряжения, элементы И 5 и 6, триггеры 7 и 8, мажоритарный элемент 9. Блок 4 памяти и внешнего сопряжения имеет регистр 10 адреса, оперативное запоминающее устройство 11, постоянное запоминающее устройство 12, узел 13 параллельного вводз- вывода, таймер 14, узел 15 приема прерып,- ний, узел 16 контроля, узел 17 ключон и узел 18 управления. Блок 3 испраплеинр iiHi|fOpI аляеа

|СлЗ

мации содержит однотипные одноразрядные узлы 19 исправления информации, каждый из которых включает мажоритарный элемент 20, ключ 21, мажоритарный элемент 22, ключ 23 и однотипные схемы 24 фиксации рассогласования. Каждая схема фиксации рассогласования имеет триггер 25, элемент ИЛИ 26, элемент ИСКЛЮЧАЮ- Ш,ЕЕ ИЛ И 27, В состав одноразрядного узла 19 входит также элемент НЕ 28.

Узел 18 управления содержит триггеры 29, элементы И 30, элементы ИЛИ 31, элементы НЕ 32, мажоритарные элементы 33, элемент ИЛИ-НЕ 34, счетчик 35, схему 36 мажоритарных элементов и регистр 37.

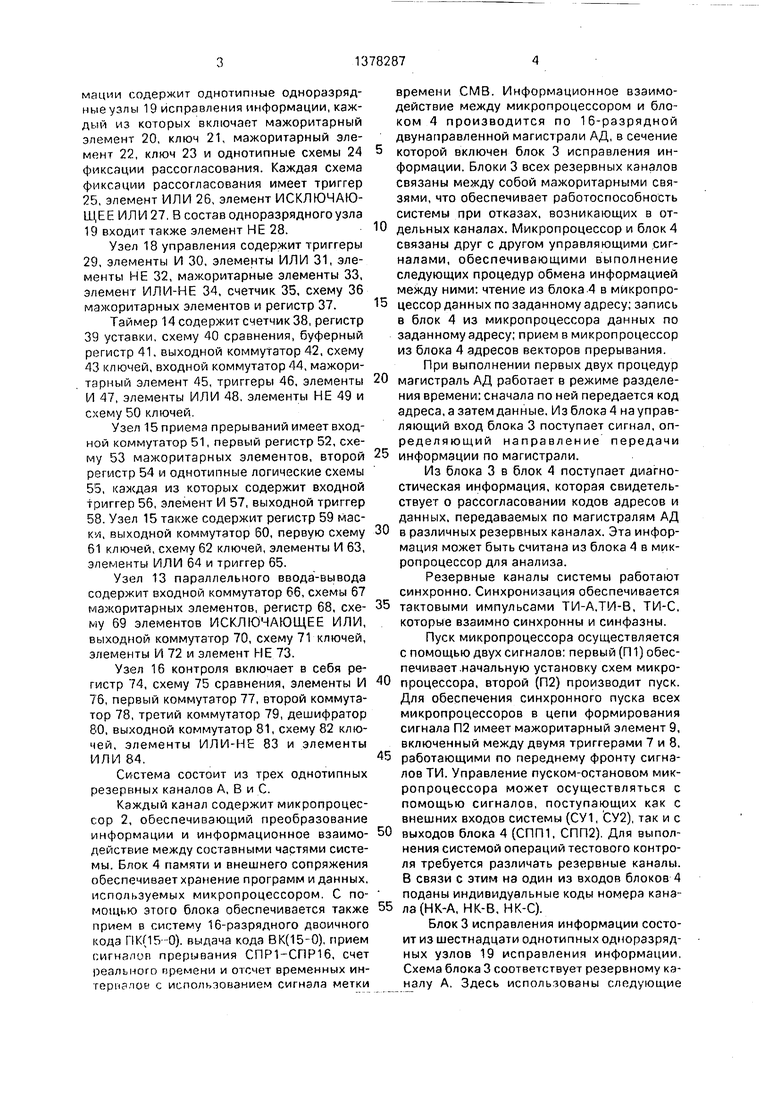

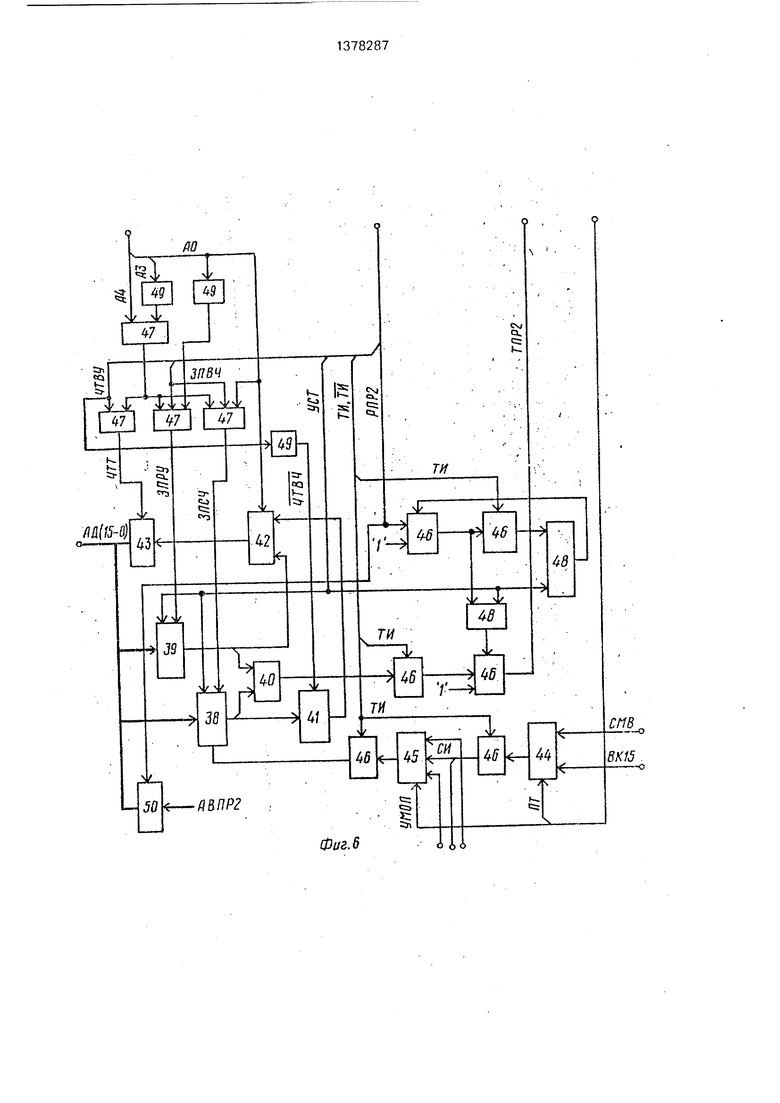

Таймер 14 содержит счетчик 38, регистр 39 уставки, схему 40 сравнения, буферный регистр 41, выходной коммутатор 42, схему 43 ключей, входной коммутатор 44, мажоритарный элемент 45, триггеры 46, элементы И 47, элементы ИЛИ 48. элементы НЕ 49 и схему 50 ключей.

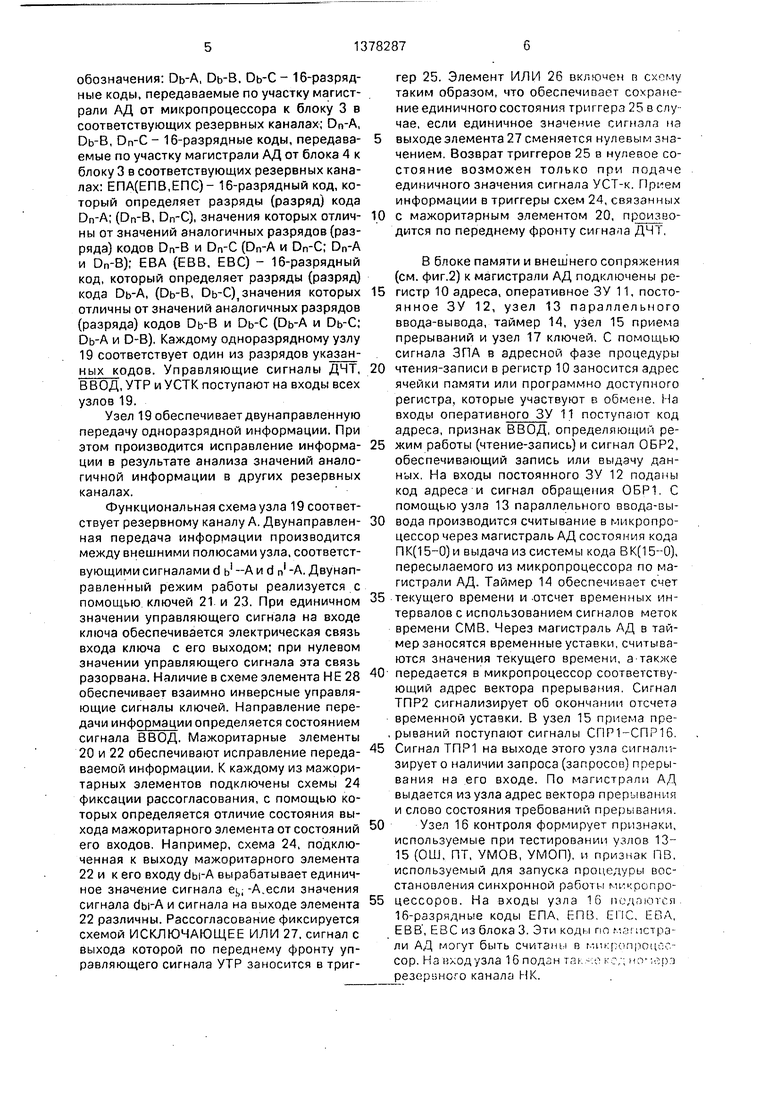

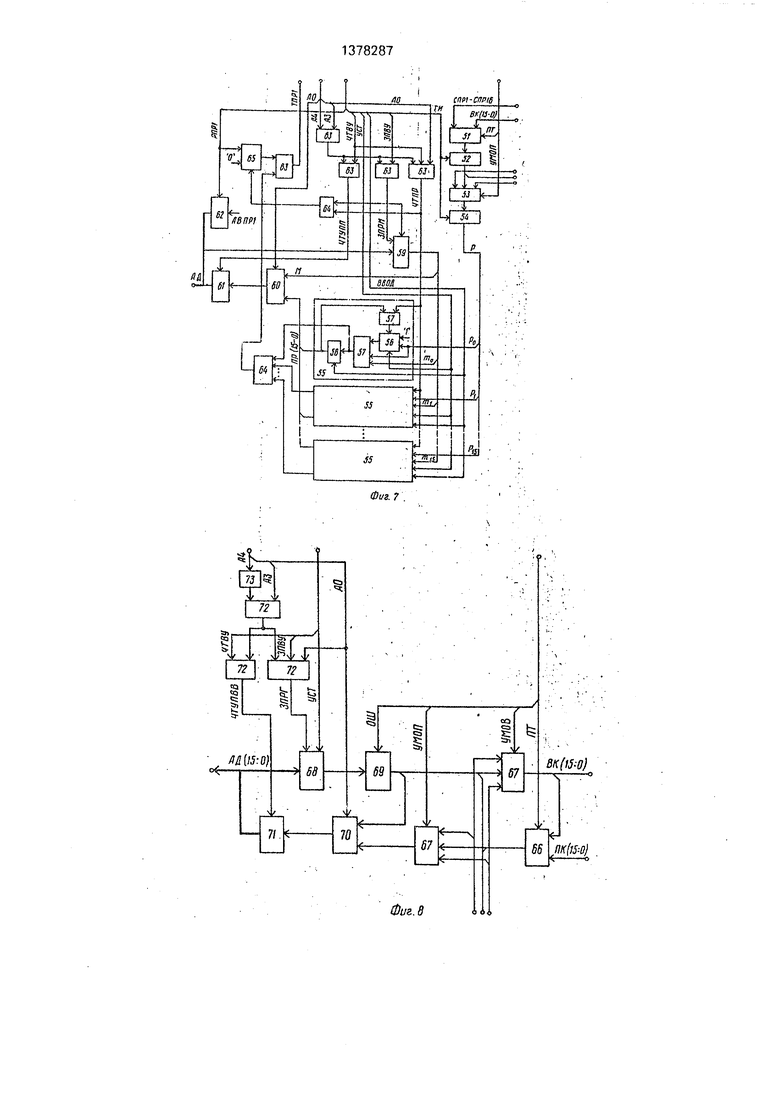

Узел 15 приема прерываний имеет входной коммутатор 51, первый регистр 52, схему 53 мажоритарных элементов, второй регистр 54 и однотипные логические схемы 55, каждая из которых содержит входной 1риггер 56, элемент И 57, выходной триггер 58. Узел 15 также содержит регистр 59 маски, выходной коммутатор 60, первую схему 61 ключей, схему 62 ключей, элементы И 63, элементы ИЛИ 64 и триггер 65.

Узел 13 параллельного ввода-вывода содержит входной коммутатор 66, схемы 67 мажоритарных элементов, регистр 68. схему 69 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, выходной коммутатор 70, схему 71 ключей, элементы И 72 и элемент НЕ 73.

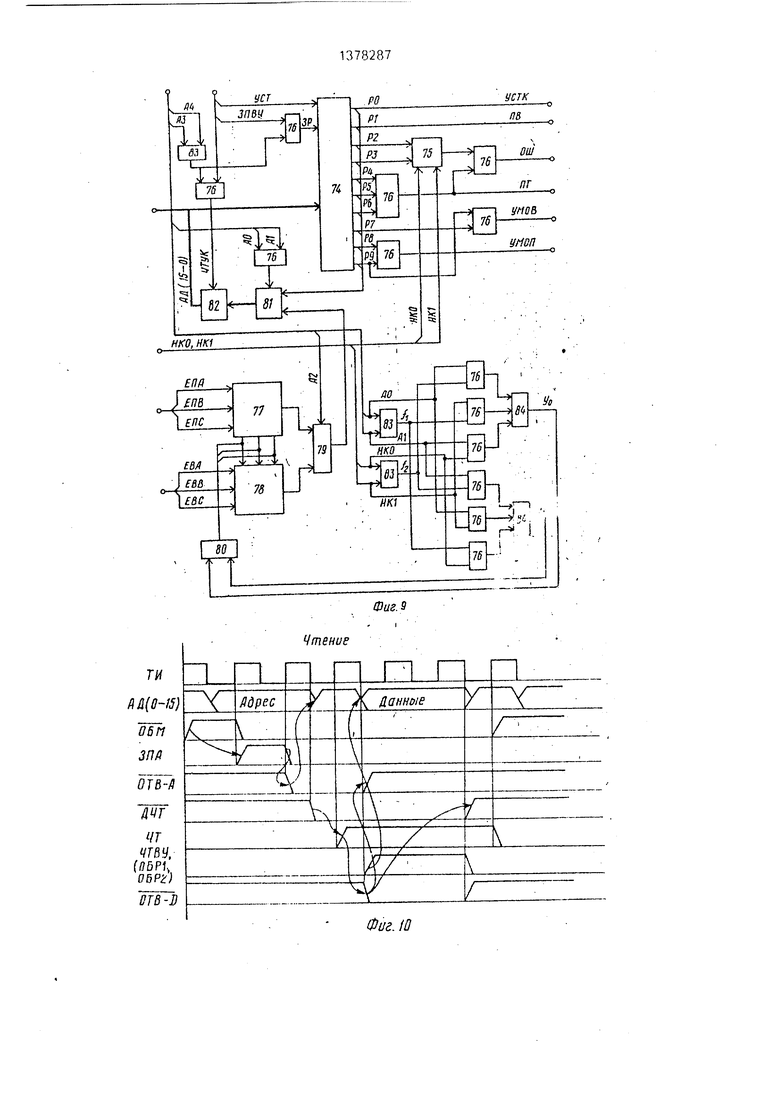

Узел 16 контроля включает в себя регистр 74, схему 75 сравнения, элементы И 76, первый коммутатор 77, второй коммутатор 78, третий коммутатор 79, дешифратор 80, выходной коммутатор 81, схему 82 ключей, элементы ИЛИ-НЕ 83 и элементы ИЛИ 84.

Система состоит из трех однотипных резервных каналов А, В и С.

Каждый канал содержит микропроцессор 2, обеспечивающий преобразование информации и информационное взаимодействие между составными частями системы. Блок 4 памяти и внешнего сопряжения обеспечивает хранение программ и данных, используемых микропроцессором. С помощью этого блока обеспечивается также прием в систему 16-разрядного двоичного кода ПК{15-0). выдача кода ВК(15-0). прием сигналоп прерывания СПР1-СПР16, счет реального премени и отсчет временных ин- терпалой с использованием сигнала метки

времени СМВ. Информационное взаимодействие между микропроцессором и блоком 4 производится по 16-разрядной двунаправленной магистрали АД, в сечение

которой включен блок 3 исправления информации. Блоки 3 всех резервных каналов связаны между собой мажоритарными связями, что обеспечивает работоспособность системы при отказах, возникающих в от0 дельных каналах. Микропроцессор и блок 4 связаны друг с другом управляющими .сигналами, обеспечивающими выполнение следующих процедур обмена информацией между ними: чтение из блока.4 в микропро5 цессор данных по заданному адресу; запись

в блок 4 из микропроцессора данных по

заданному адресу; прием в микропроцессор

из блока 4 адресов векторов прерывания.

При выполнении первых двух процедур

0 магистраль АД работает в режиме разделения времени: сначала по ней передается код адреса, а затем данные. Из блока 4 на управляющий вход блока 3 поступает сигнал, определяющий направление передачи

5 информации по магистрали.

Из блока 3 в блок 4 поступает диагностическая информация, которая свидетельствует о рассогласовании кодов адресов и данных, передаваемых по магистралям АД

0 в различных резервных каналах. Эта информация может быть считана из блока 4 в микропроцессор для анализа.

Резервные каналы системы работают синхронно. Синхронизация обеспечивается

5 тактовыми импульсами ТИ-А,ТИ-В, ТИ-С, которые взаимно синхронны и синфазны.

Пуск микропроцессора осуществляется с помощью двух сигналов: первый (П1) обеспечивает .начальную установку схем микро0 процессора, второй (П2) производит пуск. Для обеспечения синхронного пуска всех микропроцессоров в цепи формирования сигнала П2 имеет мажоритарный элемент 9, включенный между двумя триггерами 7 и 8,

5 работающими по переднему фронту сигналов ТИ. Управление пуском-остановом микропроцессора может осуществляться с помощью сигналов, поступающих как с внешних входов системы (СУ1, СУ2), так и с

0 выходов блока 4 (СПП1, СПП2). Для выполнения системой операций тестового контроля требуется различать резервные каналы. В связи с этим на один из входов блоков 4 поданы индивидуальные коды номера кана5 ла(НК-А, НК-В, НК-С).

Блок 3 исправления информации состоит из шестнадцати однотипных одноразрядных узлов 19 исправления информации. Схема блока 3 соответствует резервному каналу А. Здесь использованы следуюа1ие

обозначения: Оь-А, Оь-В, Оь-С - 16-разрядные коды, передаваемые по участку магистрали АД от микропроцессора к блоку 3 в соответствующих резервных каналах; Dn-A, Db-B, Dn-C - 16-разрядные коды, передаваемые по участку магистрали АД от блока 4 к блоку 3 в соответствующих резервных каналах: ЕПА(ЕПВ,ЕПе)- 16-разрядный код, который определяет разряды (разряд) кода Dn-A; (Dn-B, Dn-C), значения которых отличны от значений аналогичных разрядов (разряда) кодов Dn-B и Dn-C (Dn-A и Dn-C; Dn-A и Dn-B); ЕВА (EBB, ЕВС) - 16-разрядный код, который определяет разряды (разряд) кода Db-A, (Db-B, Db-C)значения которых отличны от значений аналогичных разрядов (разряда) кодов Db-B и Db-C (Db-A и Db-C; Db-A и D-B), Каждому одноразрядному узлу

19соответствует один из разрядов указанных кодов. Управляющие сигналы ДЧТ, ВВОД, УТР и УСТК поступают на входы всех узлов 19.

Узел 19 обеспечивает двунаправленную передачу одноразрядной информации. При этом производится исправление информации в результате анализа значений аналогичной информации в других резервных каналах.

Функциональная схема узла 19 соответствует резервному каналу А. Двунаправленная передача информации производится между внешними полюсами узла, соответствующими сигналами d ь -А и d п -А. Двунаправленный режим работы реализуется с помощью ключей 21 и 23. При единичном значении управляющего сигнала на входе ключа обеспечивается электрическая связь входа ключа с его выходом; при нулевом значении управляющего сигнала эта связь разорвана. Наличие в схеме элемента НЕ 28 обеспечивает взаимно инверсные управляющие сигналы ключей. Направление передачи информации определяется состоянием сигнала ВВОД. Мажоритарные элементы

20и 22 обеспечивают исправление передаваемой информации. К каждому из мажоритарных элементов подключены схемы 24 фиксации рассогласования, с помощью которых определяется отличие состояния выхода мажоритарного элемента от состояний его входов. Например, схема 24, подключенная к выходу мажоритарного элемента 22 и к его входу dbi-A вырабатывает единичное значение сигнала ei,; -А,если значения сигнала dbi-A и сигнала на выходе элемента 22 различны. Рассогласование фиксируется схемой ИСКЛЮЧАЮЩЕЕ ИЛИ 27. сигнал с выхода которой по переднему фронту управляющего сигнала УТР заносится в триг0

гер 25. Элемент ИЛИ 26 включен в схему таким образом, что обеспечивает сохранение единичного состояния триггера 25 в случае, если единичное значение сигнала на выходе элемента 27 сменяется нулевым значением. Возврат триггеров 25 в нулевое со- стояние возможен только при подаче единичного значения сигнала УСТ-к. Прием информации в триггеры схем 24, связанных с мажоритарным элементом 20, произво- дится по переднему фронту сигнапа ДЧТ,

В блоке памяти и внешнего сопряжения (см. фиг.2) к магистрали АД подключены регистр 10 адреса, оперативное ЗУ 11, постоянное ЗУ 12, узел 13 параллельного ввода-вывода, таймер 14, узел 15 приема прерываний и узел 17 ключей. С помощью сигнала ЗПА в адресной фазе процедуры

чтения-записи в регистр 10 заносится адрес ячейки памяти или программно доступного регистра, которые участвуют в обмене. На входы оперативного ЗУ 11 поступают код адреса, признак ВВОД, определяющий режим работы (чтение-запись) и сигнал ОБР2, обеспечивающий запись или выдачу данных. На входы постоянного ЗУ 12 поданы код адреса и сигнал обращения ОБР1, С помощью узла 13 параллельного ввода-вывода производится считывание в микропроцессор через магистраль АД состояния кода ПК(15-0)и выдача из системы кода ВК(15-0), пересылаемого из микропроцессора по магистрали АД. Таймер 14 обеспечивает счет

текущего времени и -отсчет временных интервалов с использованием сигналов меток времени СМВ. Через магистраль в таймер заносятся временные уставки, считываются значения текущего времени, а-также

передается в микропроцессор соответствующий адрес вектора прерывания. Сигнал ТПР2 Сигнализирует об окончании отсчета временной уставки. В узел 15 приема пре- рываний поступают сигналы СПР1-СПР16,

Сигнал ТПР1 на выходе этого узла сигнализирует о наличии запроса (запросов) прерывания на его входе. По магистрали АД выдается из узла адрес вектора прерывания и слово состояния требований прерывания.

Узел 16 контроля формирует признаки,

используемые при тестировании узлов 13- 15 (ОШ, ПТ, УМОВ, УМОП), и признак ПВ, используемый для запуска процедуры восстановления синхронной работы микропроцессоров. На входы узла 16 поллютсл . 16-разрядные коды ЕПА, ЕПВ, ЕПС, ЕВл, EBB, ЕВС из блока 3. Эти коды по ,м, М11стра- и АД могут быть считан1:1 в г.1ик ктроцоо.- ор. На вход узла 16 подан кс;; ио ; .1)з резервного канала НК.

Для обеспечения информационного обмена между микропроцессором и программно-доступным регистром узлов 13-16 в них подаются адреса с выхода регистра 10 и следующие сигналы из узла 18 управления: С1 :гнал УСТ, обеспечивающий начальную установку триггеров и регистров узлов; сигнал ЗПВУ записи информации в программно- доступные регистры; сигнал ЧТВУ чтения информации мз программно-доступных регистров; сигнал ВВОД, используемый для буферизации данных, выдаваемых в магист- раль АД; тактовые импульсы ТИ, ТИ; сигналы РПР1, РПР2, обеспечивающие выдачу адресов векторов прерывания из узлов 14 и 15.

Для обеспечения тестирования узлов 14 и 15 в первый из них подается сигнал ВК15, а во второй - ВК(15-0),

Узел 17 лючей предназначен для выдачи в магистраль АД начального адреса (НА) при пуске системы. Выдача производится при единичном значении сигнала В НА,

Регистр 10 содержит ТБ-разрядный код адреса (А14-0), с помощью которого производится адресация ячеек памяти и програм- но-доступных регистров. Разряд Al соответствует старшему разряду магистрали АД. При адресуются ячейки посто- якного ЗУ 12; гфи 1 - программио-доступные регистры узлов 13- 16, остальные значения адресов соответствуют оперативному ,V 11,

На вход узла 18 управления из микропроцессора поступают: сигнал ОБМ, фиксирующий начало процедур адресного чтения и записи; сигнал НП сопровождения операции чтения начального адреса в микропро- цессор при пуске системы; сигнал ДЧТ сопровождения операции чтения данных в микропроцессор; сигнал ДЗП сопровожде- нии операции записи: сигнал УСТ-П начальной установки; сигнал ПРР разрешения чтения адреса вектора прерывания в микропроцессор.

Из узла 18 в микропроцессор выдаются: сигнал ОТВ-А, фиксирующий окончание ад- ресной фазы з процедуре обмена; сигнал ОТВ-Д, оповещающ.ий микропроцессор о приеме выдаваемой им информации либо о подаче информации на его вхо сигнал ЗПР запроса прерывания; сигнал ПЗ запрета работы микропроцессора.

Функциональная схема узла 18 содержит логические элементы И 30, ИЛИ 31, НЕ . 32, ИЛИ-НЕ 34 и триггеры 29 синхронизации, обеспечивающие формирование управляющих сигналов и соблюдение необходимых временных соотношений между ними, С целью повышение надежности в цепи выработки сигналов управления включены мажоритарные элементы 33 и схема мажоритарного элемента 36.

Сигнал ЗПА формируется на основе сигнала ОБМ с помощь ю логической схемы, содержащей два триггера синхро н12 з ции и мажоритарный элемент. Сигнал ОТВ-А вырабатывается на выходе триггера, который устанавливается в ноль по заднему фронту

сигнала ЗПА и возвращается в единичное состояние при установке в ноль сигнала ОТВ-Д, Сигналы ОБР1, ОБР2, ЗПВУ, ЧТВУ, РПР1, РПР2, ВНА, УТР, ЗПР, УСТ вырабатываются в соответствии с выражениями:

А14 ОБМ ОТВ-Д;

А14 А13 А12 ОБМ ОТВ-Д; А14 А13 А12 ОБМ ОТВ-Д; А14 А13 А12 ОБМ ОТВ-Д; -JTIPJ ОТВ-Д;

-ТПРГ ТПР2 ОТВ-Д;

25

.ВНА ДЧТУНП; V ЗПА; УТПР2;

0

5

0

5

0

5

УСТ УСТ-П V ПВ;

где ЧТ и ЗП - сигнал на инверсных выходах триггеров, принимающих сигналы ДЧТ и ДЗП соответственно; ОБМ - Сигнал на ин- версном в ь1 ходе триггера, принимающего

сигнал ОБМ; V ЗП: ПВ - признак с выхода узла 16 контроля; ТПР1 , ТПР2 - сигналы на выходе регистра 37.

Сигнал ВВОД соответствует сдвинутому во времени сигналу ДЧТ, Сигналы СПП и СПП2 вырабатываются на вь1ходах триггеров, входы синхронизации которых управляются сигналом с выхода счетчика 35,. На входы установки в единицу этих триггеров подан сигнал УСТ, на входы установки в ноль-импульсный сигнал, формируемый по переднему фронта признака ПВ, Сигнал ПЗ вырабатывается триггером, установка в единицу которого производится в результате формирования единичного значения сигнала С, определяемого выражением

С-ДЧТ--А дчт-в дчт-с.

Это выражение соответствует резервному каналу А, выражения для других каналов имеют аналогичный вид.

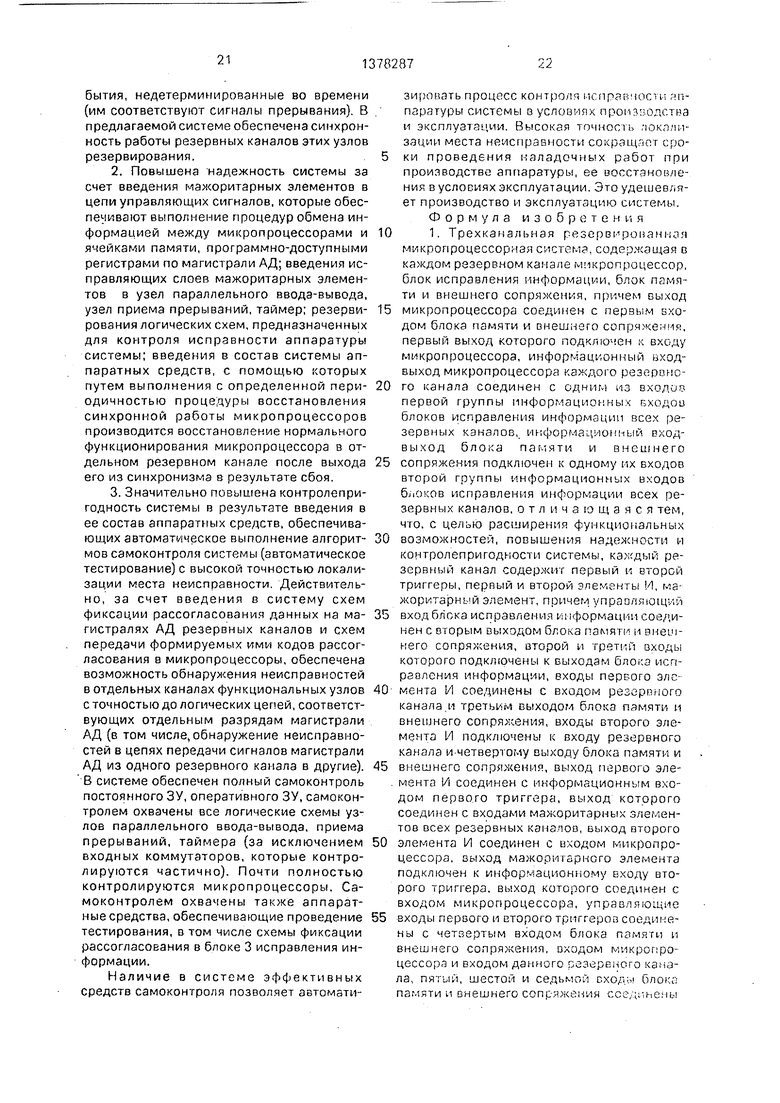

Функциональная схема таймера (см, фиг,6) содержит входной коммутатор 44, на выход которого передается либо сигнал метки времени СМВ (при ), либо сигнал ВК15 (при в режиме тестирования). Сигнал с выхода коммутатора 44 через цепь, содержащую триггеры 46 и мажоритарный элемент 45, подается на счетный вход 16- разрядного счетчика 38, Триггеры связаны с элементом 45 таким образом, что обеспечивается синхронность подачи импульсов на счетные входы счетчиков во всех резервных разрядах. При значении сигнала элемент 45 реализуетфункциютолосования по принципу 2 или при на выход этого элемента передается сигнал СИ с выхода триггера. Информационные входы счетчика 38 и регистра 39 уставки связаны с магистралью АД, что обеспечивает возможность записи в них данных по сигналам ЗПСЧ и ЗПРУ соответственно. При равенстве состояний счетчика и регистра уставки на выходе схемы АО сравнения вырабатывается сигнал, обеспечивающий формирование единичного значения сигнала ТПР2. Через выходной коммутатор 42 на вход первой схемы 43 ключей передается код либо с выхода регистра 39 (при ), либо с выхода буферного регистра 41 (при ). При единичном значении сигнала ЧТТ данные с входа схемы 43 передаются в магистраль АД. Если сигнал , состояние регистра 41 соответствует состоянию счетчика 38. В интервале времени, когда , разрывается информационная связь между счетчиком и буферным регистром, что обеспечивает устойчивость считываемой в магистраль АД информации о состоянии счетчика (код в счетчике в этом интервале времени может изменяться в результате поступления сигнала на его счетный вход).

Сигналы ЧТТ, ЗПРУ, ЗПСЧ вырабатываются в соответствии с выражениями:

А3 ЧТВУ

ЗПРУ--АЧ АО ЗПВУ

A3 и АО ЗПВУ где АЧ, A3 и АО - сигналы, соответствующие разрядам кода адреса и поступающие с выхода регистра 10 адреса.

Если сигнал , то обеспечивается выдача в магистраль АД кода адреса вектора прерывания АВПР2 через вторую схему 50 ключей. С помощью цепи, содержащей два триггера 46 и элементы ИЛИ 48, обеспечивается формирование импульса по заднему фронту сигнала РПР2, который сбрасывает в ноль триггер, формирующий сигнал ТПР2.

Функциональная схема узла приема прерываний (см.фиг.7) содержит входной коммутатор 51, через который передаются либо сигналы прерывания СПР1-СПР16 (при ), либо код ВК (15-0) (при в режиме тестирования). Цепь, содержащая регистры 52 и 54 и схему 53 мажоритарных элементов, обеспечивает синхронную передачу сигналов прерывания на входы шестнадцати однотипных логических схем 55 во всех резервных каналах. При значении сигнала мажоритарные элементы схемы 53 работают в ре. голг С.. ппи .1;: по принципу 2 из 3 при УМОП- 1 в регистр Г- через схему 53 передается состоянг.а ро(и- стра 52. На выходе регистра С)-- Формируется 5 слово P Pi5Pi iРО. Сигнал нл выходе элемента И 57 схемы 55 имеет единичное значение, если триггер 56 установлен в единицу, и имеют единичное значение сиг- налы mi и Pi на входе схемы. Ес т С1 ;гнал

0 , то значение сигнала на выходе триггера 58 определяется значением ciirH.g- ла на выходе элемента 57. При BFJO/ KO информационная связь между элементо.м 57 и . триггером 58 разрывается. Если сигнал

5 и триггер 58 установлен в 1. вырабатывается сигнал сброса в О триггера 56. Выходные триггеры 58 всех схем 55 образуют 16-разрядное слово ПР(15-0). Выходы схем 55 подключены к входам элемента

0 ИЛИ 64, вследствие чего обеспечивается

формирование сигнала ТПР1. С помоидью

сигнала ЗПРМ обеспечивается занесение

информации из магистрали АД в регистр 59

маски, на входе которого вырабатывается

5 16-разрядное слово M mi5mi-imo. Через

выходной коммутатор 60 передается либо слово М (при ), либо слово ПР (при ). При ЧТУПП 1 через первую схему 61 ключей в магистраль АД передается код с

0 выхода коммутатора 60. При через вторую схему 62 ключей в магистраль передается адрес вектора прерывания АВПР1. Сигналы ЧТУПП, ЗПРМ, ЧТПР вырабатываются в соответствии с выражениями:

5ЧТУПП АЧ A3 ЧТВУ,

A3 ЗПВУ, A3 АО ЧТВУ. По заднему фронту сигнала РПР1 переходит в нулевое состояние триггер 65 и, как

0 следствие, принимает нулевое значение сигнал ТПР1. При чтении в магистраль АД слова ПР() на вход установки в единицу триггера 65 подается сигнал с выхода элемента ИЛИ 64,

5 Функциональная схема узла параллельного ввода-вывода (см. фиг.8) содержит 16- разрядный регистр 68, в который сигналом ЗПРГ производится запись информации из магистрали АД. К выходу регистра подклю0 чена схема 69, образованная шестнадцатью элементами ИСКЛЮЧАЮЩЕЕ ИЛИ. Если сигнал , код на выходе схемы 69 соответствует коду на ее входе; при ОШ-Ч схема 69 инвертирует входной код. Если сигилл

5 , то через схему 67 мажорптарныл элементов информация с выхода 69 передается на выход узпа: при УМОВ 41 схема 67 реализует функцию голосован;1я 2 из 3. Через входной коммутатор 6G передг-ет- ся либо код ПК(15-0) (при ПТ О). либо i:o,a

ВК(15-ОХпри ПТ в режиме тестирования). Схемы 67 мажоритарных элементов идентичны. Через выходной коммутатор 70 передаются либо код с выхода схемы 69 (при ). либо код с выхода схемы 67 (при ). Через схему 71 ключей при значении сигнала ЧТУПВВ 1 производится выдача инфорг 1ации из узла. Сигналы ЧТУПВВ и ЗПРГ формируются в соответствии с выражениями:

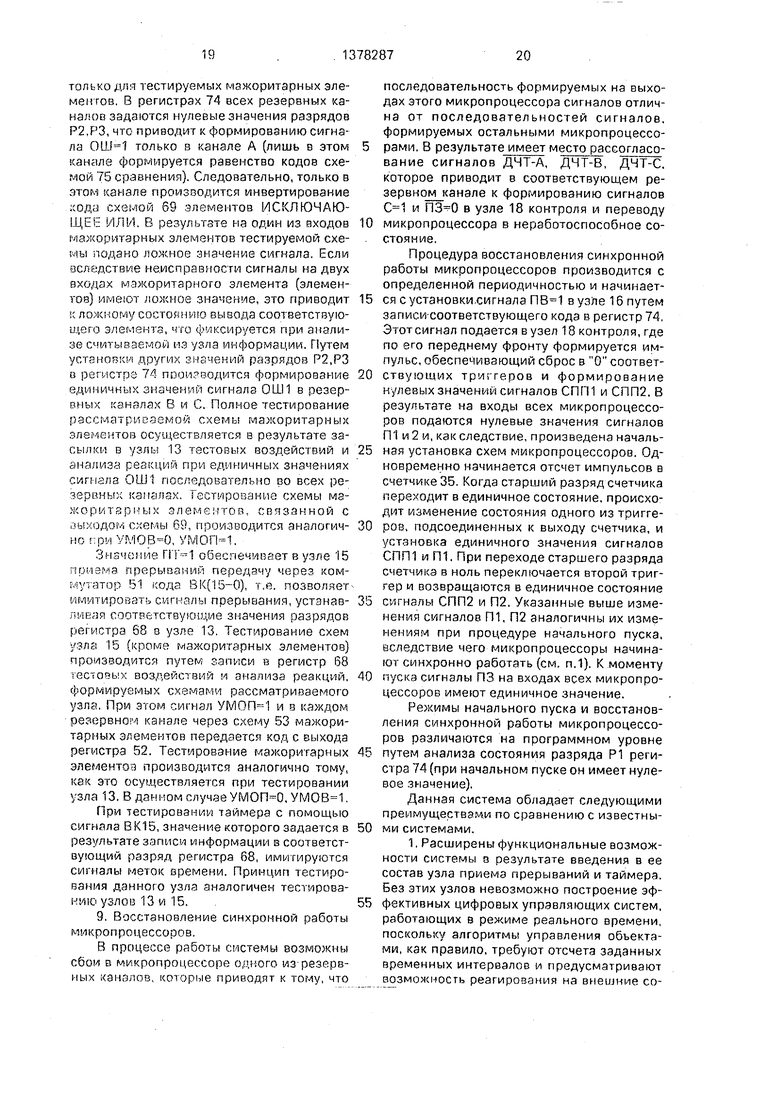

ЧТУПВ АЧ A3 ЧТВУ, -АЗ АО ЗПВУ. Функциональная схема узла контроля (см, фиг.9) содержит коммутаторы 77 и 78, на входы которых поступают коды ЕПА. ЕПВ, ЕПС и ЕВА, EBB, ВВС из блока 3 исправления информации. Из фиг.1 следует, что к идентичным входам блоков 3 а разных резервных каналах подключены магистрали АД разных ре-червчых каналов. Вместе с тем, резервные кгзналы и, следовательно, блоки 3 однотипны. Это приводит к тому, что каждый резервный канал характеризуется индивидуальным соответствием входов коммутаторов 77 и 78 подаваемым на них кодам рассогласования. Эти соответствия приведень в тзбл.1.

Схема, приведенная на фиг.9, соответствует каналу А. Третий коммутатор 79 при значении сигнала передает на свой выход код с выхода коммутатора 77, при - код с выхода коммутатора 78. Сигналы управления коммутаторами 77 и 78 фор- .мируются дешифратором 80, на вход которого подан управляющий код yiyo. При на выходы коммутаторов передаются коды с первых входов, при - с вторых, при - с третьих. Значения кодов рассогласования с входов коммутаторов 77 и 78 через коммутаторы 79 и 81 и схему 82 ключей передаются в магистраль А/,. Очевидно, что 80 всех резервных каналах в магистраль АД из узла контроля долж- ны выдаваться однотипные коды рассогласования (например - во всех кана- лах выдаются коды ЕВА). Между тем а разных резервных каналах эти коды поданы на разные входы коммутаторов 77 и 78. Указанное требование выполняется в результате формирования в каждом резервном канале индивидуальных значений управляющих кодов yiyo. Конкретный код рассогласования, передаваемый через коммутатор 77(78), задается разрядами А1, АО адреса. Соответствие между адресными кодами А1АО и значения кодов yiyo для различных резервных каналов приведено в табл.2.

На вход узла контроля в каждом резервном канале подано индивидуальное значение кода номера канала НК1 НКО, причем

каналу А соответствует код 00. каналу В - код 01, каналу С - код 10. Значения кодов yiyo в различных резервных каналах формируются в результате анализа значений кодов А1 АО и НК1 НКО. Соответствующие логические выражения имеют вид:

V АО НКО V НК1 V НКО х

X А1 VHK1 АО,

V АО НК1 V НК1 V НКО х

XAOVHKO-A1.

Регистр 74 информационным входом связан с магистралью АД. Запись информации в этот регистр производится сигналом ЗР, причем V A3 ЗПВУ. Единичное значение признака тестирования ПТ формируется в результате установки единичного значения сигналов P4-PG на выходе регистра 74. Утроение сигналов регистра выполнено с целью исключения формирования ложного значения указанного признака при сбоях триггеров регистра в штатном режиме работы. Выходные сигналы РО, Р1 регистра 74 соответствуют сигналам УСТК и ПВ, Сигналы Р2, РЗ поданы на вхо,цы схемы 75 сравнения, которая управляется также сигналами НКО, НК1. Сигнал только при и равенстве кодов РЗ,Р2 и НК1 НКО. Значения сигналов УМОВ и УМОП определяются состоянием разрядов регистра 74, причем Р9 и Р9. Использование сигнала Р9 снижает вероятность ложного формирования этих сигналов в штатном режиме работы системы.

Через выходной коммутатор 81 информация с выхода регистра 74 передается при . Схема 82 ключей обеспечивает выдачу информации из узла в магистраль АД, если сигнал ( V A3 ЧТВУ).

Система работает следующим образом.

1. Начальный пуск системы.

При нулевых значениях сигналов СУ2-А; СУ2-В, СУ2-С и СУ1-А, СУ1-В; СУ1-С на входах резервных каналов система вь,1ключена. Ее включение происходит в результате изменения состояний указанных сигналов. При этом сначала переходят в единичное состояние сигналы СУ1-А, СУ1-В СУ1-С (и, соотеетственно, сигналы П1 на входах микропроцессоров), а затем сигналы СУ2-А: СУ2-В, СУ2-С, вследствие чего синхронно устанавливаются единичные значения сигналов П2 на входах микропроцессоров. Это обеспечивает синхронный переход в нулевое состояние сигналов ДТЧ и НП на выходах микропроцессоров всех резервных каналов и формирование единичного значения сигнала ВНА на выходе узла 18 управления (фиг.2). При указанном значении сигнала ВНА производится выдача в магист- АД кода адреса ячейки постоянного ЗУ

(НА), в которой хранится адрес первой команды программы пуска системы.

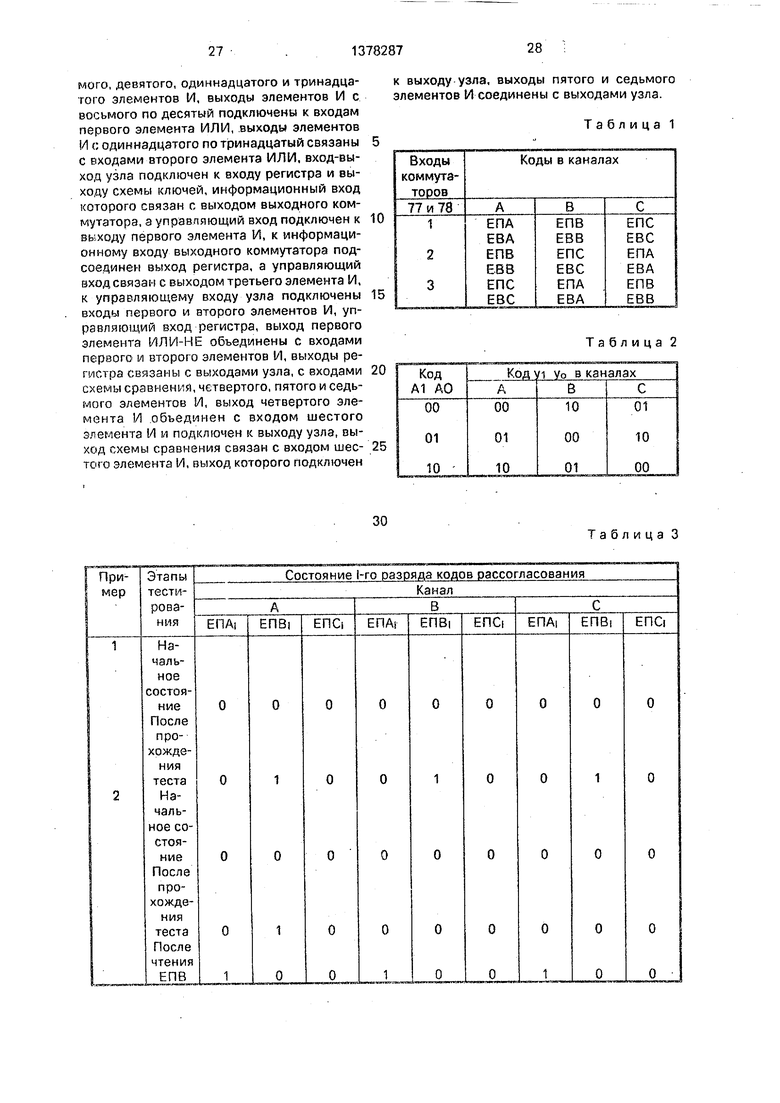

2. Чтение данных в микропроцессор из ячеек памяти программно-доступных регистров.

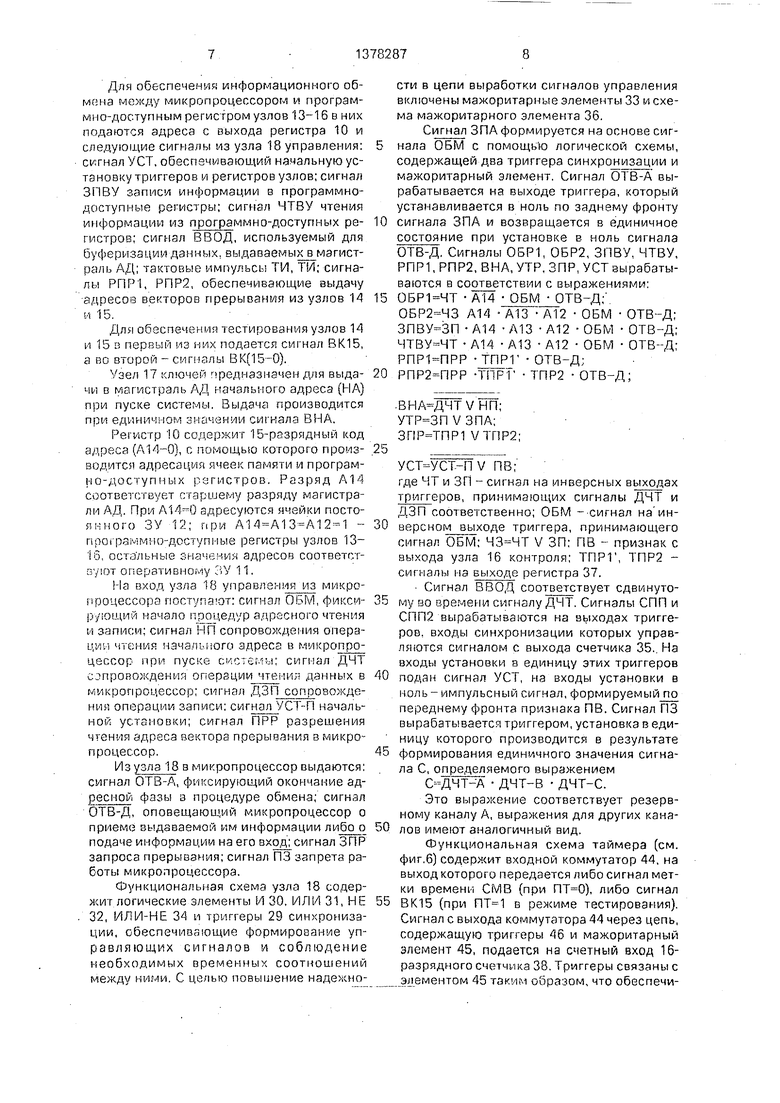

Этому режиму работы соответствует временная диаграмма, представленная на фиг.10. Выполнение данной процедуры состоит из двух фаз: фазы выдачи из микропроцессора адреса ячейки памяти или программно-доступного регистра и фазы чтения данных.

В фазе выдачи адреса на магистрали АД микропроцессором выставляется код адреса. На основе сигнала ОБМ узлом 18 управ- ления вырабатывается единичное значение сигнала ЗПА, в результате чего код, установленный на магистрали АД, записывается в регистр 10 адреса. Переход в ноль сигнала ЗПА обусловливает формирование нулевого значения сигнала ОТВ-А, в результате чего микропроцессор снимает код адреса со своих выходов и вырабатывает нулевое значение сигнала ДЧТ. С этого начинается выполнение фазы чтения данных. Измене- ние сигнала ДЧТ вызывает формирование в узле 18 управления сигналов, с помощью которых считываемые в микропроцессор данные выставляются на магистрали АД. При зтом устанавливается единичное значе- ние сигнала ЧТ на выходе триггера 29, при- нимающего сигнал ДЧТ. Источник считываемой информации определяется в результате анализа логическими схемами узла 18 старших разрядов адреса, поступа- ющих в этот узел с выхода регистра 10. Если , то чтение производится из программно-доступного регистра одного из узлов 13-16. В этом случае формируется единичное значение сигнала ЧТВУ, посту- пающее во все указанные узлы. В узле, содержащем программно-доступный регистр, адрес которого соответствует коду на выходе регистра 10 (это определяется логическими схемами узла путем анализа младших разрядов адреса, поступающих с выхода регистра 10), производится выдача содержимого этого регистра в магистраль АД.

Если , то узлом 18 вырабатывается единичное значение сигнала ОБР 1, обес- печивающее выдачу в магистраль АД содержимого ячейки постоянного ЗУ 12, адрес которой определяется кодом, поступающим в это ЗУ с выхода регистра 10.

Если и разряды А13,А12 одновре- менно не установлены в единичное состояние, то узлом 18 вырабатывается единичное значение сигнала ОБР2, обеспечивающее выдачу в магистраль АД содержимого ячейки оперативного ЗУ 11, адрес которо определяется кодом, поступающим с выход; ре гистра 10. Значение сигнала ВВОД пнперс- но по отношению к сигналу ЧТ.

Единичные значения сигналов ЧТВУ. ОБР1, ОБР2 вырабатываются при ну/тевом значении сигнала ОТВ-Д, который формируется узлом 18 и подается на вход микропроцессора. Переход этого сигнала влечет за собой переход сигнала ДЧТ из нулевого состояния в единичное, прием данных в микропроцессор и завершение процедуры чтения.

В адресной фазе , вследствие чего через мажоритарные элементы блекл 3 исправления информации код адреса передается от микропроцессора к входу регист- ра 10. В фазе чтения сигнал и данные передаются по магистрали АД через блок 3 к микропроцессору.

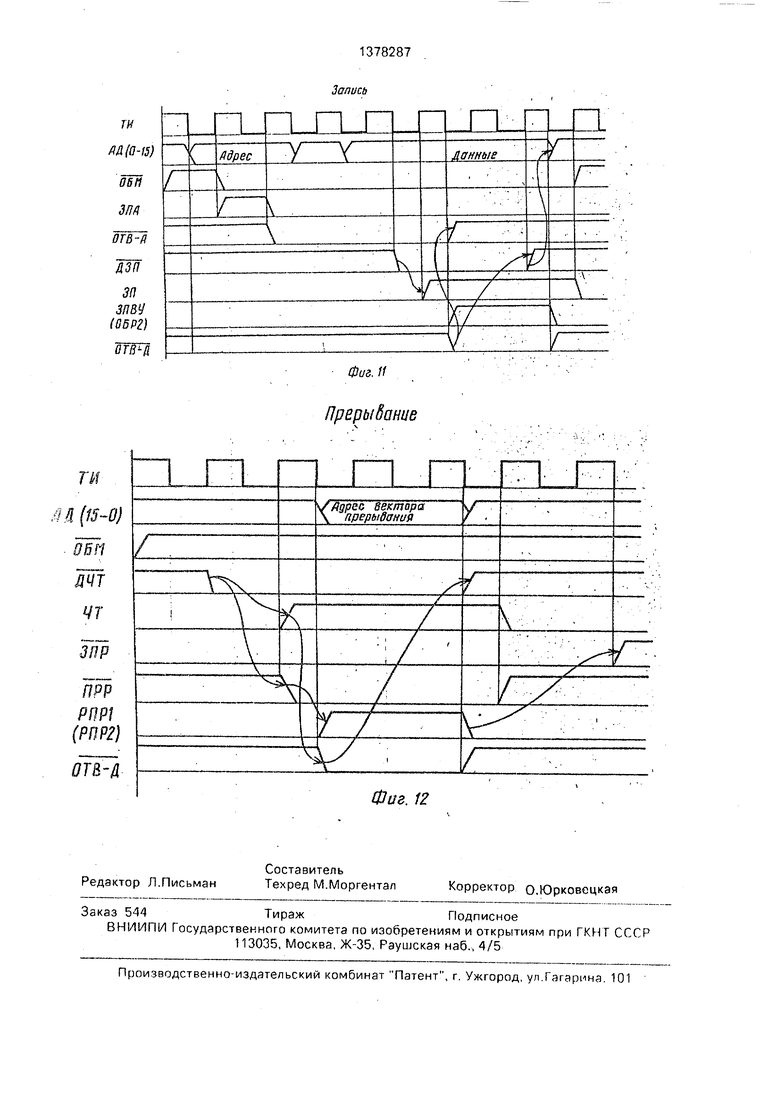

3.Запись данных из микропроцессора в ячейки памяти программно-доступных регистров.

Этому режиму работы системы соответствует временная диаграмма, представленная на фиг.11. Адресная фаза данной процедуры аналогична рассмотренной. Фаза записи начинается с установки микропроцессором записываемых данных на магистрали АД. Переход сигнала ДЗП на выходе микропроцессора из единично о состояния в нулевое вызывает формирование на выходе триггера 29 узла 18, принимающего этот сигнал, единичного значения сигнала ЗП. Если состояние старших разрядоо адреса определяет обращение к программно-доступным регистрам, то узел 18 вырабатывает сигнал ЗПВУ, поступающий в узлы 13-16. В результате анализа младших разрядов адреса в указанных узлах на основе и сигнала ЗПВУ формируется сигнал записи в программно-доступный регистр, адрес которого соответствует состоянию регистра

10.Это состояние старших разрядов адреса определяет обращение к оперативному ЗУ

11,вырабатывается единичное значение сигнала ОБР2.

Переход сигнала ОТВ-Д в нулевое состояние влечет за собой возвращение к еди- ничному значению сигнала ДЗП и окончание выполнения процедуры.

4.Прием сигналов прерывания.

В зтом режиме сигналы ПТ и УМОП, вырабатываемые узлом 16 контроля, имеют нулевое значение. Процедура прерывания по сигналам, поступающим на входы узла 15 приема прерываний, начинается при перо- ходе одного или нескольких сигналоп СП1- СП15 из нулевого состояния в единичное. Если прерывания по этим сигналам разрешены (соответствующие разряды регистра

50 маскм находятся в единичном состоянии), то триггеры 56 и 58 соответствующих логических схем 55 устанавливаются в 1, в результате чего вырабатывается единичное значение сигнала ТПР1 на выходе узла 15, который поступает в узел 18 управления и обеспечивает формирование нулевого значения сигнала ЗПР, поступающего в микропроцессор. По окончании выполнения -очередной команды микропроцессор переходит в режим приема адреса вектора прерывания. При этом (см, фиг.12) переходит в нулевое состояние сначала сигнал ДЧТ, а затем сигнал ПРР. Сигнал ОБМ находится в единичном состоянии, что исключает ложнее формирование сигналов управления на выходе узла 18, Нулевое значение ПРР обусловливает формирование единичного значения сигнала РПР1, который обеспечивает выдачу из узла IS вектора прерывания АЕШР1, Переход сигнала ОТВ-Д в нулевое состоянме приводит к приему адреса вектора в микропроцессор и возврату в состояние 1 смгмалов ДЧТ м ПРР, По заднему фронту сигнала РПР1 устанавливается в О триггер влечет за собой переход в 1 сигнала ЗГТР на входе микропроцессора. По приня- TOP-iy адресу вектора гферывания микропроцессор переходит к подпрограмме, содержащей команду пересылки содержимого программно-доступного регистра, об- резованного триггерами 58 узла 15, в микропроцессор. Выполнение процедуры чтения указанного регистра сопровождается форр ированием в узле 15 единичного значения сигнала ЧТПР, что вызывает сброс в О триггеров 56 тех логических схем 55, триггеры 58 которых имеют единичное состоя нив. Таким образом, информация о требованиях прерь(взния передается в микропроцессор для анализа, а триггеры 58 по окончанми процедуры чтения возвращаются в нулевое состояние, что обеспечивает однократную передачу отдельного требования прерывания в микропроцессор. Если во время выполнения процедуры чтения триггер 56 в схеме 55 {в нескольких схемах 55) устанавливается в 1, то по окончании процедуры это приводит к установке в 1 соответствующих триггеров 58 и повторению процедуры отработки прерывания,

5, Прием и выдача параллельного кода,

В этом режиме разряды регистра 74 узла 16 контроля установлены в состояния, при которых сигналы ,

Выдаваемый параллельный код заносится в регистр 68 в результате выполнения

процедуры записи данных из микропроцессора в программно-доступный регистр. При этом формируется единичное значение сигнала ЗПРГ, Код с выхода регистра 68 через

схему 69 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и схему 67 мажоритарных элементов передается на выход системы, не изменяя своего значения.

Код ПК(15-0) с входа системы передает0 ся через входной коммутатор 66 и схему 67 мажоритарных элементов на вход коммутатора 70, не изменяя своего ,значеиия. Он поступает в микропроцессор в результате выполнения процедуры чтения из програм5 мно-доступного регистра. При этом формируется единичное значения сигнала ЧТУПВВ,

6, Счет реального времени и отсчет временных интервалов,

0

Этот режим реализуется с помощью таймера 14, В данном случае сигнал , С помощью процедуры записи данных из МП Q счетчик 38 заносится исход5 ное значение реального времени, при этом формируется сигнал , после чего в результате по,дачи сигналов метки времени на вход CMS происходит непрерывное изменение состояния счетчика. Путем выпол0 нения процедуры чтения буферного регистра 41 производится передача значе- реального времени в микропроцессор, При этом вырабатывается сигнал и сигнал , вследствие чего регистр 41

6 отключается от счетчика, обеспечивая устойчивое считывание содержимого регистра в микропроцессор даже в случае, когда процедура чтения совпадает во времени с подачей импульса на счетный вход счетчика,

0

С помощью сигнала ЗПВУ в процедуре записи данных из микропроцессора в регистр 39 производится запись значения временной установки. При переходе счетчика

5 38 в состояние, соответствующее содержимому регистра 39, вырабатывается единичное значение сигнала на выходе схемы 40 сравнения и, как следствие этого, производится установка в единицу сигнала ТПР2

0 требования прерывания. Отработка процедуры прерывания, вызванной этим сигналом, осуществляется аналогично отработке прерывания по сигналу ТПР1 (см, п.4), В результате формирования сигнала

5 производится передача в микропроцессор адреса вектора прерывания АВПР2, По заднему фронту этого сигнала вырабатывается одиночный импульс, обеспечивающий сброс в О триггера, формирующего сигнал ТПР2,

7. Тестирование микропроцессоров, оперативных ЗУ и постоянных ЗУ резервных каналов.

Данная процедура выполняется с использованием аппаратных средств блоков 3 рассогласования и узлов 16 контроля резер- вных каналов системы. В начале процедуры тестирования отдельного узла путем выполнения двух операций записи в регистр 74 узлов 16 формируется единичное значение сигнала УСТК в каждом канале: при первой операции в разряд РО регистра заносится 1, при второй - О, В результате производится установка в нулевое состояние всех триггеров 3 блоках 3 рассогласования. Вслед за этим на магистрали АД каждого канала выполняется последовательность операций записи данных из микропроцессора в оперативное ЗУ и чтени-я данных из ОЗУ и ПЗУ в микропроцессор, с помощью которых обеспечивается передача в тести- руемый узел тестовых воздействий, снятие с тестируемого узла реакций на эти воздействия, формирование эталонных значений реакций, выполнение в микропроцессоре операций сравнения реакций с эталонными значениями. В результате реализации на программном уровне соответствующего алгоритма тестирования фиксируются отказы однотипных логических схем в двух резервных каналах. Наличие отказов в схемах тес- тируемых узлов отдельных резервных каналов определяется схемами фиксации рассогласования в блоках 3. Выполняя операции чтения кодов рассогласования ЕПА, ЕПВ, ЕПС, ЕВА, EBB, ЕВС из узлов 16 и анализа их в микропроцессорах, можно определить место отказа с точностью до логической цепи узла отдельного резервного канала, определяющий значение сигнала на отдельной линии магистрали АД. Коды рас- согласования позволяют определить, имело ли место рассогласование при передаче данных от микропроцессора или к нему.

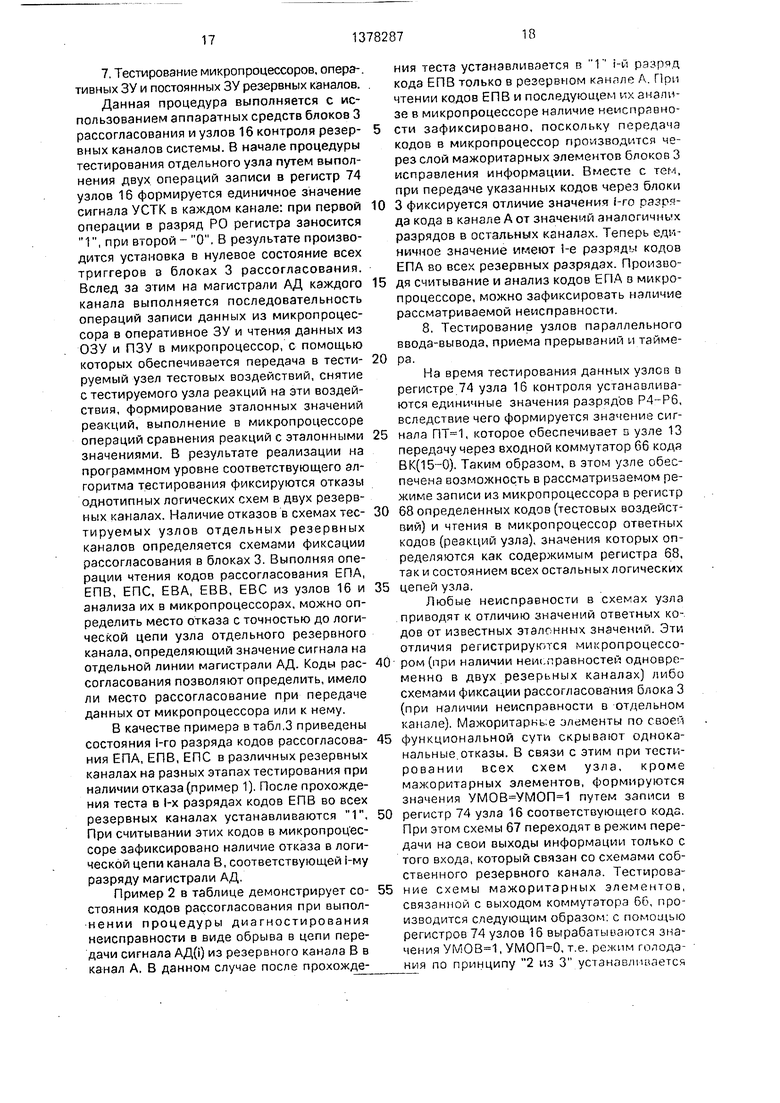

В качестве примера в табл.З приведены состояния i-ro разряда кодов рассогласова- ния ЕПА, ЕПВ, ЕПС в различных резервных каналах на разных этапах тестирования при наличии отказа(пример 1). После прохождения теста в 1-х разрядах кодов ЕПВ во всех резервных каналах устанавливаются 1, При считывании этих кодов в микропроцессоре зафиксировано наличие отказа в логической цепи канала В, соответствующей i-му разряду магистрали АД.

Пример 2 в таблице демонстрирует со- стояния кодов рассогласования при выполнении процедуры диагностирования неисправности в виде обрыва в цепи передачи сигнала АД(|) из резервного канала В в канал А. В данном случае после прохождения теста устанавливается в 1 i-й разряд кода ЕПВ только в резервном канале А. При чтении кодов ЕПВ и последующем их анализе в микропроцессоре наличие немспрйвно- сти зафиксировано, поскольку передача кодов в микропроцессор производится через слой мажоритарных элементов блоков 3 исправления информации. Вместе с тем, при передаче указанных кодов через блоки 3 фиксируется отличие значения 1-го разряда кода в канале А от значений аналогичных разрядов в остальных каналах. Теперь единичное значение 1-е разряды кодов ЕПА во всех резервных разрядах. Производя считывание и анализ кодов ЕПА в микропроцессоре, можно зафиксировать наличие рассматриваемой неисправности.

8. Тестирование узлов параллельного ввода-вывода, приема прерываний и таймера.

На время тестирования данных узлов tj регистре 74 узла 16 контроля устанавливаются единичные значения разрядов Р4-Р6, вследствие чего формируется значение сигнала , которое обеспечивает п узле 13 передачу через входной коммутатор 66 кода ВК(15-0). Таким образом, в этом узле обеспечена возможность в рассматриваемом режиме записи из микропроцессора в регистр 68 определенных кодов (тестовых воздействий) и чтения в микропроцессор ответных кодов (реакций узла), значения которых определяются как содержимым регистра 68, так и состоянием всех остальных логических цепей узла.

Любые неисправности в схемах узла приводят к отличию значений ответных кодов от известных эталонных значений. Эти отличия регистрируются микропроцессором (при наличии неи(,;1равностей одновременно в двух резервных каналах) либо схемами фиксации рассогласования блока 3 (при наличии неисправности в отдельном канале). Мажоритарные элементы по своей функциональной сути скрывают однока- нальные.отказы. В связи с этим при тестировании всех схем узла, кроме мажоритарных элементов, формируются значения путем записи в регистр 74 узла 16 соответствующего кодз. При этом схемы 67 переходят в режим передачи на свои выходы информации только с того входа, который связан со схемами собственного резервного канала. Тестирование схемы мажоритарных элементов, связанной с выходом коммутатора 66, производится следующим образом: с помощью регистров 74 узлов 16 вырабатываются значения , , т.е. режим голода- ния по принципу 2 из 3 устаиавливаетсй

только для тестируемых мажоритарных элементов. В регистрах 74 всех резервных каналов задаются нулевые значения разрядов Р2,РЗ, что приводит к формированию сигнала только в канале А (лишь в этом канлле форр ируется равенство кодов схемой 75 сравнения). Следовательно, только в этом канале производится инвертирование ;(ода схемой 69 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ. В результате на один из входов мажоритарных элементов тестируемой схе- мы г.одано ложное значение сигнала. Если аследствие неисправности сигналы на двух входах мажоритарного элемента (элементов) имеют ложное значение, это приводит 1C ложному состоянию вывода соответствую- идего элемента, что фиксируется при анализе считываемой из узла информации. Путем установки других значений разрядов Р2,РЗ в регистре 74 пооиззодится формирование единичных значений сигнала ОШ1 в резервных каналах В и С. Полное тестирование рассматриваемой схемы мажоритарных элементов осуществляется в результате засылки в узлы 13 тестовых воздействий и анализа реакций при единичных значениях сигнала ОШ 1 последовательно во всех резервных ка(алах. Тестирование схемы мз- жоритзрыых .элеме1. тов, связанной с аыходо схемы 69, производится аналоп-ш- г ОприУМОВ 0, .

Значение ГГ1 --- 1 обеспечивает в узле 15 приема прерываний передачу через ком- iviyraTop 51 кода 8К(15-0), т.е. позволяет имитировать сигналы прерывания, устзнав- яивая соответствующие значения разрядов регистра 68 в узле 13. Тестирование схем узлг; 15 (кроме мажоритарных элементов) производится путем записи в регистр 68 тестовых воздействий и анализа реакций, формируемых схемами рассматриваемого узла. При этом сигнал и в каждом резервном канале через схему 53 мажоритарных элементов передается код с выхода регистра 52. Тестирование мажоритарных элементоа производится аналогично тому, как это осуществляется при тестировании узла 13. В данном случае , .

При тестировании таймера с помощью сигнала ВК15, значение которого задается в результате записи информации в соответствующий разряд регистра 68, имитируются сигналы меток времени. Принцип тестирования данного узла аналогичен тестированию узлов 13 и 15. .

9. Восстановление синхронной работы микропроцессоров.

В процессе работы системы еозможны сбои в микропроцессоре одного из-резервных каналов, которые приводят к тому, что

последовательность формируемых на выходах этого микропроцессора сигналов отлична от последовательностей сигналов, формируемых остальными микропроцессорами. В результате имеет место рассогласо- вание сигналов ДЧТ-А, AMT-I, ДЧТ-С. которое приводит в соответствующем ре- зервно м канале к формированию сигналов и ПЗ-0 в узле 18 контроля и переводу микропроцессора в неработоспособное состояние.

Процедура восстановления синхронной работы микропроцессоров производится с определенной периодичностью и начинается сустановки.сигнала 16 путем записи-соответствующего кода в регистр 74. Этот сигнал подается в узел 18 контроля, где по его переднему фронту формируется импульс, обеспечивающий сброс в О соответ- ствующих триггеров и формирование нулевых значений сигналов СПП1 и СПП2. В результате на входы всех микропроцессоров подаются нулевые значения сигналов П1 и 2 и, как следствие, произведена начальная установка схем микропроцессоров. Одновременно начинается отсчет импульсов в счетчике 35. Когда старший разряд счетчика переходит в единичное состояние, происходит изменение состояния одного из триггеров, подсоединенных к выходу счетчика, и установка единичного значения сигналов СПП1 и П1, При переходе старшего разряда счетчика в ноль переключается второй триггер и возвращаются в единичное состояние сигналы СПП2 и П2. Указанные выше изменения сигналов П1, П2 аналогичны их изменениям при процедуре начального пуска. вследствие чего микропроцессоры начинают синхронно работать (см. п.1). К моменту пуска сигналы ПЗ на входах всех микропроцессоров имеют единичное значение.

Режимы начального пуска и восстановления синхронной работы микропроцессоров различаются на программном уровне путем анализа состояния разряда Р1 регистра 74 (при начальном пуске он имеет нулевое значение).

Данная система обладает следующими преимуществами по сравнению с известными системами.

1. Расширены функциональные возможности системы 3 результате введения в ее состав узла приема прерываний и таймера. Без этих узлов невозможно построение эффективных цифровых управляющих систем, работающих в режиме реального времени, поскольку алгоритмы управления объектами, как правило, требуют отсчета заданных временных интервалов и предусматривают возможность реагирования на внешние события, недетерминированные во времени (им соответствуют сигналы прерывания). В предлагаемой системе обеспечена синхронность работы резервных каналов этих узлов резервирования.

2.Повышена надежность системы за счет введения мажоритарных элементов в цепи управляющих сигналов, которые обеспечивают выполнение процедур обмена информацией между микропроцессорами и ячейками памяти, программно-доступными регистрами по магистрали АД; введения исправляющих слоев мажоритарных элементов в узел параллельного ввода-вывода, узел приема прерываний, таймер; резерви- рования логических схем, предназначенных для контроля исправности аппаратуры системы; введения в состав системы аппаратных средств, с помощью которых путем выполнения с определенной пери- одичностью процедуры восстановления синхронной работы микропроцессоров производится восстановление нормального функционирования микропроцессора в отдельном резервном канале после выхода его из синхронизма в результате сбоя.

3.Значительно повышена контролепригодность системы в результате введения в ее состав аппаратных средств, обеспечивающих автоматическое выполнение алгорит- мов самоконтроля системы (автоматическое тестирование) с высокой точностью локализации места неисправности. Действительно, за счет введения в систему схем фиксации рассогласования данных на ма- гистралях АД резервных каналов и схем передачи формируемых ими кодов рассогласования в микропроцессоры,обеспечена возможность обнаружения неисправностей

в отдельных каналах функциональных узлов с точностью до логических цепей, соответствующих отдельным разрядам магистрали АД (в том числе, обнаружение неисправностей в цепях передачи сигналов магистрали АД из одного резервного канала в другие). В системе обеспечен полный самоконтроль постоянного ЗУ, оперативного ЗУ, самоконтролем охвачены все логические схемы узлов параллельного ввода-вывода, приема прерываний, таймера (за исключением входных коммутаторов, которые контролируются частично). Почти полностью контролируются микропроцессоры. Самоконтролем охвачены также аппаратные средства, обеспечивающие проведение тестирования, в том числе схемы фиксации рассогласования в блоке 3 исправления информации.

Наличие в системе эффективных средств самоконтроля позволяет автоматизировать процесс контроля исправмости ,чп- пзрзтуры системы в условиях про11я;50дства и эксплуатации. Высокая точносгь локпли- зации места неисправности сокращает сроки проведения наладочных работ при производстве аппаратуры, ее аосстановле- ния в условиях эксплуатации. Это удешевляет производство и эксплуатацию системы. Формула изобретения 1. Трехканальная резервироианноя микропроцессорная система, содержащая в каждом резервном канале макропроцессор, блок исправления информации, блок памяти и внешнего сопряжения, причем выход микропроцессора соединен с первым входом блока памяти и внешнего сопря кеи 1я, первый выход которого подключен к входу микропроцессора, информационный вход- выход микропроцессора каждого резервного канала соединен с одним sia ВХОДОР первой группы информационных входоа блоков исправления информации всех резервных каналов, ииформац /1ОМ1-1Ый вход- выход блока памяти и внешнего сопряжения подключен к одному i-ix входов второй группы информационных входов блоков исправления информации всех резервных каналов, о т л и ч а io щ а я с я тем, что. с целью расширения функциональных возможностей, повышения надежности и контролепригодности системы, каждый резервный канал содержит первый и второй триггеры, перЕзый и второй элементы И, мажоритарный элемент, причем. упрапляю1Ц1-1й вхо,а бл ока исг1равления шчформацмп соединен с вторым выходом блока si BHCUI- кего сопряжения, второй и третий входы которого подключены к выходам блока исп- раоления информации, входы первого элемента И сое,.т,ииены с входом резерпиого канала,и третьим выходом блока памяти и BHeiiJHero сопряжения, входы второго элемента И подключены к входу резервного канала и-четвертому выходу блока памяти и внешнего сопряжения, выход первого элемента И соединен с информационным входом первого триггера, выход которого соединен с входами мажоритарных элементов всех резервных каналов, выход второго элемента И соединен с входом микропроцессора, выход мажоритарного элемента подключен к информационному входу второго триггера, выход которого соединен с входом микропроцессора, управляющие входы первого и второго триггеров соедике- ны с четвертым входом блока памяти и внешнего сопряжения, входом микрогфо- цессора и входом данного резервного канала, пятый, шестой и седьмой сходы Dnofca памяти и внешнего сопряжения сседпнемы

С входами резервного канала, пятый выход блока памяти и внешнего сопряжения подключен к выходу резервного канала, шестой выход блока памяти и внешнего сопряже- нмл каждого резервного канала связан, с входами блоков памяти и внешнего сопряжения всех резервных каналов, восьмые входы блоков памяти и внешнего сопряжения резервных каналов являются, входами двухразрядиых кодов номеров резервных каналов,

2. Система по п.1, о т л и ч а ю щ а я с я тем, что блок памяти и внешнего сопряжения содержит оперативное запоминающее устройство, постоянное запоминающее устройство, регистр адреса, узел параллельного Ешода-вывода, таймер, узел приема прерываний, узел контроля, узел управле- Hi -iH, узел ключей, причем информационный вход-выход блока соединен с входами-выходами оперативного ЗУ, узла параллельного ввода-выаода, таймера, узла приема преры- ванмй, узла контроля, с информационными выходами постоянного ЗУ и узла ключей, с /(Нфэрмациониым входом регистра адреса, регмстра адоеса подключен к адрес-. ны. « входам оперативного ЗУ, постоянного ЗУ, узла параллельного ввода-вывода, таймера, узла приема прерываний, узла конт- рол9, узла управления, управляющий вход регистра адреса связан с первым выходом узпо угфавления, второй выход которого подключен к управля ощим входам опера- тивмого ЗУ, постоянного ЗУ, узла парал- лвл1зного врода-вь1 шда, тэймера, узла приема г рерываннй и узла контроля, а третий выход - к -управляющему вхо,цу узла к.пючей, выхо,ц узла контроля подключен к входам узла приема прерывания, таймера, узла параллельного ввода-вывода и узла уп- рзвяени55, вход которого соединен с выходами таймера и узла приема прерываний, выходы и входы для мажоритарных связей узла управления, узла параллельного ввода- вывода, таймера, узлэ приема прерываний подключены к шестому выходу и входам блока, второй, третий и восьмой входы которого соединены с входами узла контроля, второй вывод - с выходами узла управления и узла контроля, первый, третий и четвертый выходы - с входами узла управления, а первый и четвертый входы - с входами узлами упревления.

3. Система по п.1, о т л и ч а ю щ а я с я тем, что блок исправления информации со- дерхсит однотипнь е одноразрядные узлы исправления информации, причем к управляющему входу блока подключены соответственно первые-четвертые входы узлов, к первому выходу блока подключены первыетретьи выходы сигналов рассогласования узлов, к второму выходу-четвертые-шестые выходы рассогласования узлов, первая группа информационных входов подключена к первым информационным входам-выходам, первым и вторым информационным входам узлов, а вторая группа мнформаци- .онных входов блока соединена с вторыми информационными входами-выходами,

третьим и четвертым информа1(ионными входами узлов.

4. Система по пп, 1 и 3, о т л и ч а ю щ а- я с я тем, что однозарядный узел исправления информации содержит первый и второй

мажоритарные элементы, первы й и второй ключи, шесть однотипных, .схем фиксации рассогласования и инвертор, схема фиксации рассогласоаа|Чия содержит триггер, элемент ИЛИ и элемент ИСКЛЮЧАЮЩЕЕ

ИЛИ, причем кг.ормационный оходчригге- ра подключен к выходу .элемента И.ПИ, входы которого связаны с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и выходом триггера первые входы элементов ИСКЛЮЧАЮЩЕЕ

ИЛИ первой, второй и тре гьей схем фиксации рассогласования связаны с входами первого мажоритарного элементз, выход которого подключен к информационному входу первого ключа и к вгооым входам

элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, первой, второй и третьей схем фиксации рассогласования, первые управляющие входы триггерогз которых объединены и подключены к первому входу узла, а сыхо,цы связаны

с первым, вторым i/i третьим выходами сигналов рассогласования узла, первые вхо.й.ы злементов ИСКЛЮЧАЮЩЕЕ ИЛИ четвертой, пятой, шестой схем фиксации рассогла- соваимя связаны с входами второго

мажоритарного элемента, выход которого подключв - к информационному входу второго ключа м к вторым входам элементов ИСКЛЮЧАЮЩЕЕ ИЛИ четвертой, пятой и Чиестой схем фиксации рассогласования,

первые управ/ Я10щие вхо,дь триггеров которых соединены с четвертым входом узла, а выходы - с четвертым-шестыг И выходами сигналов рассогласования узла, первый вход первого мажоритарного элемента

объединен с выходом второго ключа и подключен к первому информационному входу-выходу узла, а его второй и третий входы подключены к первому и.второму информационным входам у.зла, первый вход второго

мажоритарного элемента объединен с выходом первого ключа и подклиичен к второму информационному входу-выходу узла, а его второй и третий входы подключены к третьему и четвертому информ.зционнь м входам узла, вторые управляющ1ле входы всехтригrepOB объединены и подключены к третьему входу узла, четвертый вход которого связан с управляющим входом второго ключа и входом инвертора, выход которого подключен к управляющему входу первого ключа.

5. Система по пп.1 и2,отличающа- я с я тем, что узел управления содержит триггеры, мажоритарные элементы, элементы И, ИЛИ, НЕ, элементы ИЛИ-НЕ, схему мажоритарных элементов, регистр, счетчик, причем входы первого, третьего, четвертого, восьмого триггеров, входы первого элемента ИЛИ-НЕ, первый вход второго элемента ИЛИ-НЕ и первый вход четырнадцатого элемента ИЛИ подключены к входу узла, адресный вход которого соединен с входами третьего, четвертого, пятого и шестого элементов И, входы четвертого элемента ИЛИ и регистра подключены к входу узла, выход первого триггера через первый мажоритарный элемент соединен с входом второго триггера, выход которого подключен к входу синхронизации седьмого триггера, выход первого элемента ИЛИ-НЕ через второй мажоритарный элемент связан с вы- ходом узла, входы третьего элемента ИЛИ подключены к выходам третьего и четвертого триггеров, а выход соединен с первым входом второго элемента И, выход которого черезтретий мажоритарный элемент связан с входом пятого триггера, выход пятого триггера подключен к вхо,ду шестого триггера, выход которого связан с входами первого и второго элементов И, выход первого элемента И соединен с первым входом пер- вого элемента ИЛИ, второй вход которого подключен к выходу второго элемента ИЛИ- НЕ, а выход связан с входом седьмого триггера, выход пятого элемента И связан с входом третьего элемента И и подключен к входу первого элемента НЕ, выход которого подключен к входу четвертого элемента И, входы шестого-одиннадцатого элементов И соединены с выходами регистра, первого, третьего, четвертого, пятого и восьмого триггеров, третьего и четвертого элементов И, второго элемента НЕ, третьего э/.емента ИЛИ, а выходы подключены к входам схемы мажоритарных элементов, выходы которой соединены с выходами узла, выход четвер- того элемента ИЛИ подключен к входу девятого триггера, выход которого через четвертый мажоритарный элемент соединен с входом десятого триггера, выход второго триггера объединен с первым входом второго элемента ИЛИ и подключен к первому выходу узла, выход четвертого триггера связан с вторым входом второго элемента ИЛИ, выход которого соединен с выходом узла, выходы пятого, седьмого, десятого и четырнадцатого триггере подключены к выходу узла, входы счнхро -1-за1В1и первого-шестого, восьмого-одчниядцатого и четырнадцатого триггеров, а ,е сметный вход счетчика соедине н с входом узлп, второй вход второго элемента ИЛ1- М-1 : объединен с входом одиннадцатого триггера, первым входом двенадцатого злемеига И и подключен к входу узла, выход одиннадцатого триггера связан с вторым входом двенадцатого элемента И, выход которого соединен с управляющими входами двенадцатого и тринадцатого триггеров, выход второго элемента ИЛИ-НЕ подключен к входам двенадцатого-четырнадцатого триггеров и схемы мажоритарных элементов, выход счетчика связан с входом двенадцатого триггера и через третий элемент НЕ с входом тринадцатого триггера, вход которого объединен с выходом двенадцатого триггера и подключен к выходу узла, а выход объединен с входом счетчика, первым входом четырнадцатого элемента И и подкпкхен к выходу узла, второй и третий входы тринадцатого элемента М через четвертый и пятый инверторы подключены к входам узла, выход четырнадцатого триггера связан с входом четырнадцатого элемента И, выход которого соединен с первым входом пятого элемента ИЛИ, вход четырнадцатого триггера связан с выходом пятого элемента-ИЛИ, второй вход которого подключены с выходу тринадцатого элемента И, входы мажоритарных элементов и схемы мажоритарных элементов подключены к шестому выходу и входам для мажоритарных связей узла.

6. Система по пп,1 и 2, о т л и ч а ю щ а- я с я тем, что узел контроля содержит регистр, схему сравнения, коммутаторы, дешифратор, схему ключей, элементы И, ИЛИ, ИЛИ-НЕ, причем информационные входы первого и второго коммутаторов связаны с входами узла, а их управляющие входы подключены к выходу дешифратора, входы которого соединены с выходами элементов ИЛИ, выходы первого и второго коммутаторов связаны с входами третьего коммутатора, выход которого подключен к информационному входу выходного коммутатора, к адресному входу подсоединены входы первого и второго элемснгов ИЛИ- НЕ, третьего, восьмого, десятого, одиннадцатого, двенадцатого элеменгоЕз И, управляющий вход третьего коммутатор,. входы третьего элемента ИЛИ-НЕ. деаято- го, десятого, двенадцатого и тринадцатого элементов И, схемы сравнения подк.пючены к входу узла, выходы вторе со и rfX irn-K эпе- ментов ИЛИ-НЕ соединены с влпд.-i-.-ii ;осьмого, девятого, одиннадцатого и тринадцатого элементов И, выходы элементов И с восьмого по десятый подключены к входам первого элемента ИЛИ, выходы элементов И с одиннадцатого по тринадцатый связаны с входами второго элемента ИЛИ. вход-выход узла подключен к входу регистра и выходу схемы ключей, информационный вход которого связан с выходом выходного коммутатора, а управляющий вход подключен к выходу первого элемента И. к информационному входу выходного коммутатора подсоединен выход регистра, а управляющий вход связан с выходом третьего элемента И. к управляющему входу узла подключены входы первого и второго элементов И, управляющий вход регистра, выход первого элемента ИЛИ-НЕ объединены с входами первого и второго элементов И, выходы регистра связаны с выходами узла, с входами схемы сравнений, четвертого, пятого и седьмого элементов И, выход четвертого элемента И .объединен с входом шестого элемента И и подключен к выходу узла, выход схемы сравнения связан с входом шее- того элемента И, выход которого подключен

к выходу узла, выходы пятого и седьмого элементов И соединены с выходами узла.

Таблица 1

Таблица 2

| название | год | авторы | номер документа |

|---|---|---|---|

| ТРЕХКАНАЛЬНАЯ РЕЗЕРВИРОВАННАЯ МИКРОПРОЦЕССОРНАЯ СИСТЕМА | 1987 |

|

SU1494761A1 |

| Мажоритарно-резервированный интерфейс памяти | 1990 |

|

SU1751766A1 |

| Устройство индикации состояния ЭВМ | 1989 |

|

SU1667067A1 |

| Мажоритарно-резервированный аналого-цифровой преобразователь | 1987 |

|

SU1444946A1 |

| Многоканальное регистрирующее устройство | 1988 |

|

SU1698899A1 |

| МИКРОПРОЦЕССОР ВВОДА-ВЫВОДА ИНФОРМАЦИИ | 1992 |

|

RU2042182C1 |

| Устройство для контроля и восстановления микропроцессорной системы | 1985 |

|

SU1317441A1 |

| Мультиплексное устройство для обмена информацией | 1983 |

|

SU1157546A1 |

| Резервированная система | 1990 |

|

SU1785087A1 |

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении высоконадежных вычислительных управляющих систем. Цель изобретения - расширение функциональных возможностей системы, повышение ее надежности и контролепригодности. Система содержит резервные каналы 1, содержащие микропроцессор 2, блок 3 исправления информации, блок памяти и внешнего сопряжения, элементы И 5 и 6, триггеры 7 и б, мажоритарный элемент 9. Блок 3 содержит однотипные одноразрядные узлы исправления информации, а блок памяти и внешнего сопряжения включает в себя оперативное запоминающее устройство, постоянное запоминающее устройство, регистр адреса, узел параллельного ввода-вывода, таймер, узел приема прерываний, узел контроля, узел управления и узел ключей. Наличие в системе средств самоконтроля позволяет повысить надежность и контролепригодность, а наличие таймера и узла приема прерываний - применять систему в режиме реального времени. 5 з.п.ф-лы, 12 ил., 3 табл. СП с

Таблица 3

atn н/,4чг, an, прр. acr-n

ФигМ

-о

.S

rj

rji

s

}JЯ84

f

, to

Ш Ш Q7

i-

K.

:эМ,

S

«тэ

43

- c-j C; t

42

v/

Ц

38

fin

1-- /iJ

50

fiBnP2

Фиг.6

Sf

c TM

И

p

45

rw

-

7Л

;(5

45

СИ

44

C;

I

Обо

Фиг. ID

ТИ / Д1а-15)

ОбП

ЗП/1

йзп зп

ЗПВУ

(ОБрг)

5WJ

Прерыбанив

ГЯ

(lff-0) Ш

т

ЦТ

J7/P

рт

(РПР2)

ш-д

| Трехканальная резервированная вычислительная система | 1980 |

|

SU949864A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| ЭЛЕКТРОЛИТ ЛУЖЕНИЯ ЖЕСТИ | 1995 |

|

RU2093614C1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Способ получения фтористых солей | 1914 |

|

SU1980A1 |

Авторы

Даты

1992-11-07—Публикация

1985-09-24—Подача