1

Изобретение относится к измерительной технике.

Известны интеграторы напряжения, предназначенные для исследования физических процессов и основанные на методе двухтактного интегрирования. Они содержат последовательно соединенные интегрирующий усилитель и сравнивающее устройство, ключи, через первый ключ вход интегратора соединен со входом интегрирующего усилителя, вход последнего соединен через второй и третий ключи с источниками эталонных напряжений, схемы совпадения, схему измерения времени, триггер уяравл-ееия, единичный ;выход которого подключен к управляющему входу первого ключа.

Для поддержания таких устройств в состоянии готовности к интегрированию в любой момент времени используются ключи, шунтирующие интегрирующий конденсатор и вход усилителя.

Существенным недостатком таких интеграторов является зависимость выходного результата от величины и стабильности порога срабатывания сравнивающего устройства. Известные методы уменьщения влияния дрейфа и величины порога срабатывания сравнивающего устройства на точность, используе-мые в интегрирующих преобразователях цифровых вольтметров, не позволяют синхронизировать момент начала интегрирования с началом физического процесса.

С целью повышения точности, в предложенном интеграторе вход первой схемы совпадения соединен непосредственно с выходом сравнивающего устройства, вход второй схемы совпадения - через инвертор, разрешающие входы схем совпадения подключены к нулевому выходу триггера, а выходы подключены

к управляющим входам второго и третьего ключей.

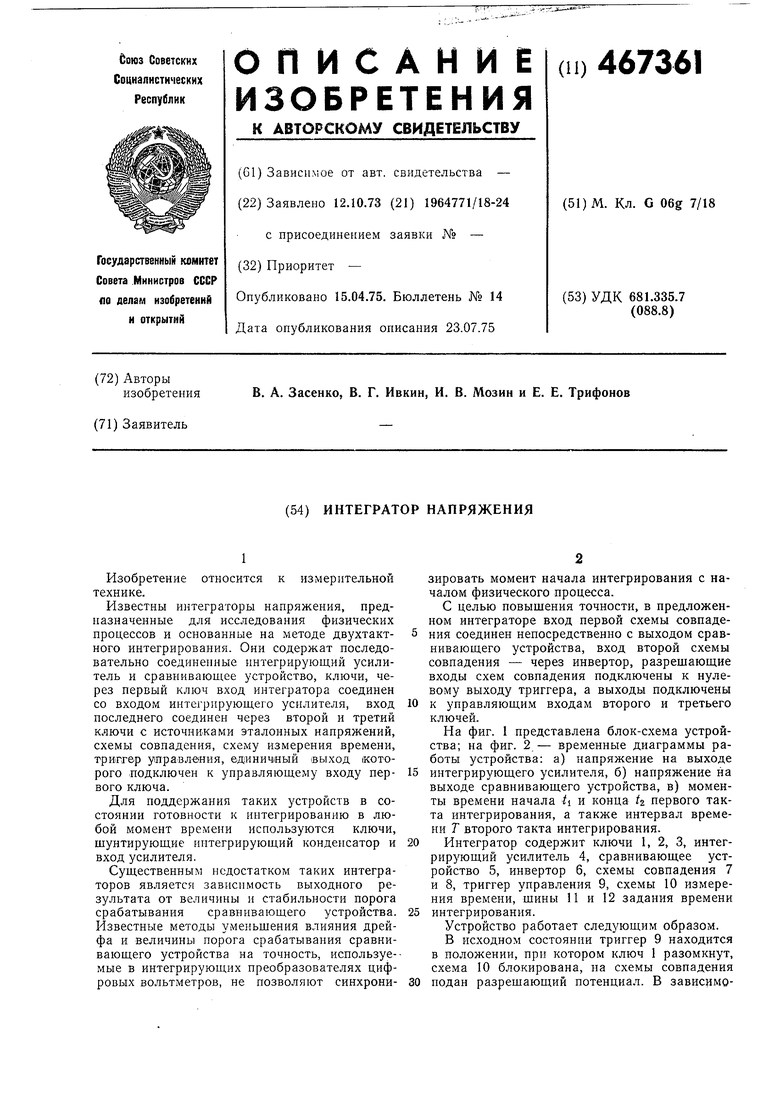

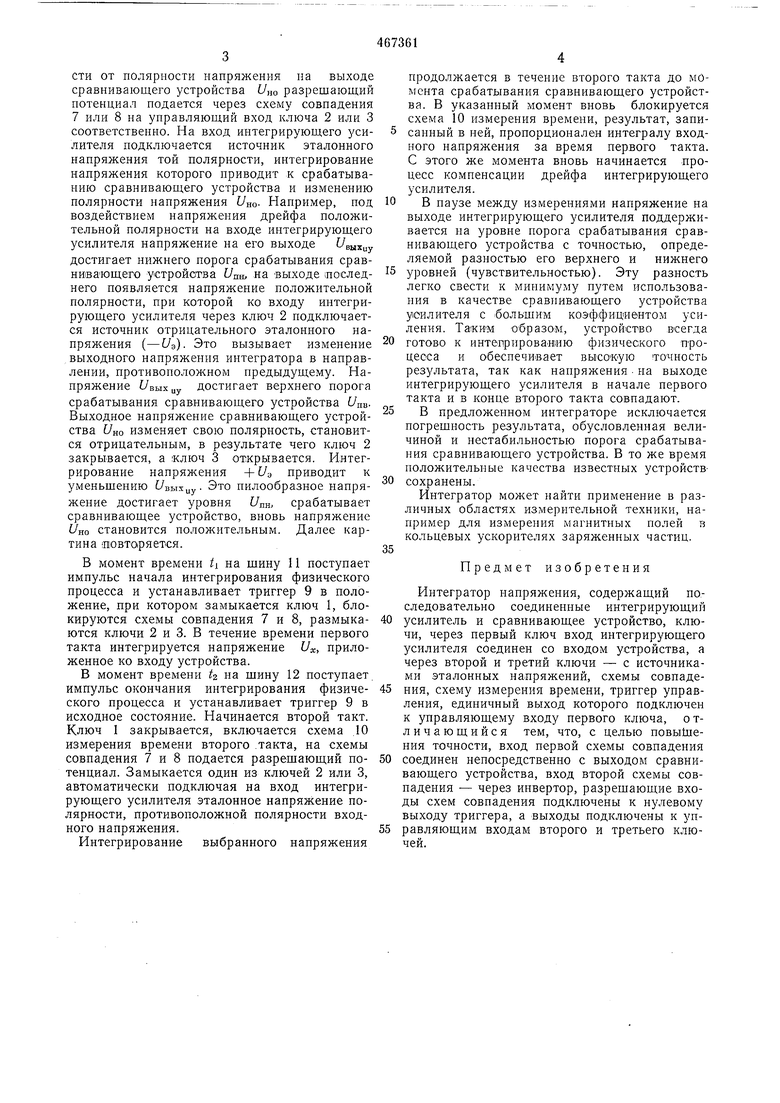

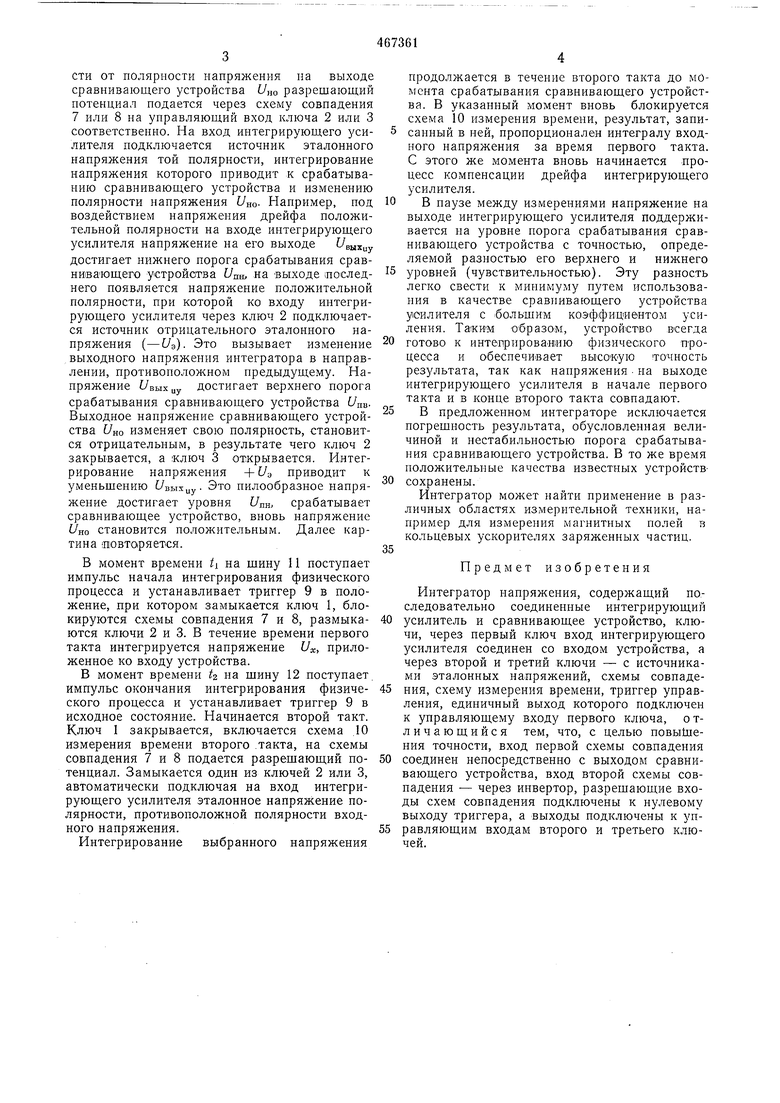

На фиг. 1 представлена блок-схема устройства; на фиг. 2 - временные диаграммы работы устройства: а) напряжение на выходе

интегрирующего усилителя, б) напряжение на выходе сравнивающего устройства, в) моменты времени начала -ti и конца tz первого такта интегрирования, а также интервал времени Т второго такта интегрирования.

Интегратор содержит ключи 1, 2, 3, интегрирующий усилитель 4, сравнивающее устройство 5, инвертор б, схемы совпадения 7 и 8, триггер управления 9, схемы 10 измерения времени, щины 11 и 12 задания времени

интегрирования.

Устройство работает следующим образом. В исходном состоянии триггер 9 находится в положении, при котором ключ 1 разомкнут, схема 10 блокирована, на схемы совпадения

подан разрешающий потенциал. В зависимости от полярности напряжения па выходе сравнивающего устройства t/но разрешающий нотенциал подается через схему совпадения 7 или 8 на управляющий вход ключа 2 или 3 соответственно. На вход интегрирующего усилителя подключается источник эталонного напряжения той полярности, интегрирование напряжения которого приводит к срабатыванию сравнивающего устройства и изменению полярности напряжения t/но. Например, под воздействием напряжения дрейфа положительной полярности на входе интегрирующего усилителя напряжение на его выходе выхцу достигает нижнего порога срабатывания сравнивающего устройства С/пш на выходе последнего появляется напряжение положительной полярности, при которой ко входу интегрирующего усилителя через ключ 2 подключается источник отрицательного эталонного напряжения (). Это вызывает изменение выходного напряжения интегратора в направлении, противоположном предыдущему. Напряжение t/BbiXuy достигает верхнего порога срабатывания сравнивающего устройства (УдвВыходное напряжение сравнивающего устройства УНО изменяет свою полярность, становится отрицательным, в результате чего ключ 2 закрывается, а ключ 3 открывается. Интегрирование напряжения +Uy приводит к уменьщению С/выхцу. Это пилообразное напряжение достигает уровня f/nn, срабатывает сравнивающее устройство, вновь напряжение L/HO становится положительным. Далее картина оовторяется.

В момент времени ti на шину 11 поступает импульс начала интегрирования физического процесса и устанавливает триггер 9 в положение, при котором замыкается ключ 1, блокируются схемы совпадения 7 и 8, размыкаются ключи 2 и 3. В течение времени первого такта интегрируется напряжение Ux, приложенное ко входу устройства.

В момент времени t на шину 12 поступает импульс окончания интегрирования физического процесса и устанавливает триггер 9 в исходное состояние. Начинается второй такт. Ключ 1 закрывается, включается схема 10 измерения времени второго .такта, на схемы совпадения 7 и 8 подается разрешающий потенциал. Замыкается один из ключей 2 или 3, автоматически подключая на вход интегрирующего усилителя эталонное напряжение полярности, противоположной полярности входного напряжения.

Интегрирование выбранного напряжения

продолжается в течение второго такта до момента срабатывания сравнивающего устройства. В указанный момент вновь блокируется схема 10 измерения времени, результат, записанный в ней, пропорционален интегралу входного напряжения за время первого такта. С этого же момента вновь начинается процесс компенсации дрейфа интегрирующего усилителя.

В паузе между измерениями напряжение на выходе интегрирующего усилителя поддерживается на уровне порога срабатывания сравнивающего устройства с точностью, определяемой разностью его верхнего и нижнего

уровней (чувствительностью). Эту разность легко свести к минимуму путем использования в качестве сравнивающего устройства усилителя с большим коэф:фи:циентом усиления. TaiKHM образом, устройство всегда

готово к интегрированию физического процесса и обеспечивает высокую точность результата, так как напряжения на выходе интегрирующего усилителя в начале первого такта и в конце второго такта совпадают.

В предложенном интеграторе исключается погрешность результата, обусловленная величиной и нестабильностью порога срабатывания сравнивающего устройства. В то же время положительные качества известных устройствсохранены.

Интегратор может найти применение в различных областях измерительной техники, например для измерения магнитных полей s кольцевых ускорителях заряженных частиц.

Предмет изобретения

Интегратор напряжения, содержащий последовательно соединенные интегрирующий

усилитель и сравнивающее устройство, ключи, через первый ключ вход интегрирующего усилителя соединен со входом устройства, а через второй и третий ключи - с источниками эталонных напряжений, схемы совпадеимя, схему измерения времени, триггер управления, единичный выход которого подключен к управляющему входу первого ключа, о тли чающийся тем, что, с целью повыШеиия точности, вход первой схемы совпадения

соединен непосредственно с выходом сравнивающего устройства, вход второй схемы совпадения - через инвертор, разрешающие входы схем совпадения подключены к нулевому выходу триггера, а выходы подключены к управляющим входам второго и третьего ключей.

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегратор напряжения | 1980 |

|

SU962993A1 |

| Цифровой термометр | 1986 |

|

SU1404844A1 |

| Цифровой измеритель коэффициента передачи четырехполюсника | 1986 |

|

SU1323985A1 |

| Аналого-цифровой интегратор | 1979 |

|

SU849236A1 |

| ЦИФРОВОЙ ИНТЕГРИРУЮЩИЙ ВОЛЬТАМПЕРМЕТР | 1972 |

|

SU347909A1 |

| Преобразователь ток-частота с импульсной обратной связью | 1987 |

|

SU1552377A1 |

| Источник калиброванных напряжений | 1985 |

|

SU1283726A1 |

| Способ аналого-цифрового преобразования и устройство для его осуществления | 1975 |

|

SU684738A1 |

| СПОСОБ ИЗМЕРЕНИЯ ИЗНОСА РЕЖУЩЕГО ИНСТРУМЕНТА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2007 |

|

RU2354955C1 |

| Датчик отклонения магнитного поля произвольной формы | 1973 |

|

SU474306A1 |

вш

У

oj

nl

Unti

i

UHO

6j

Авторы

Даты

1975-04-15—Публикация

1973-10-12—Подача