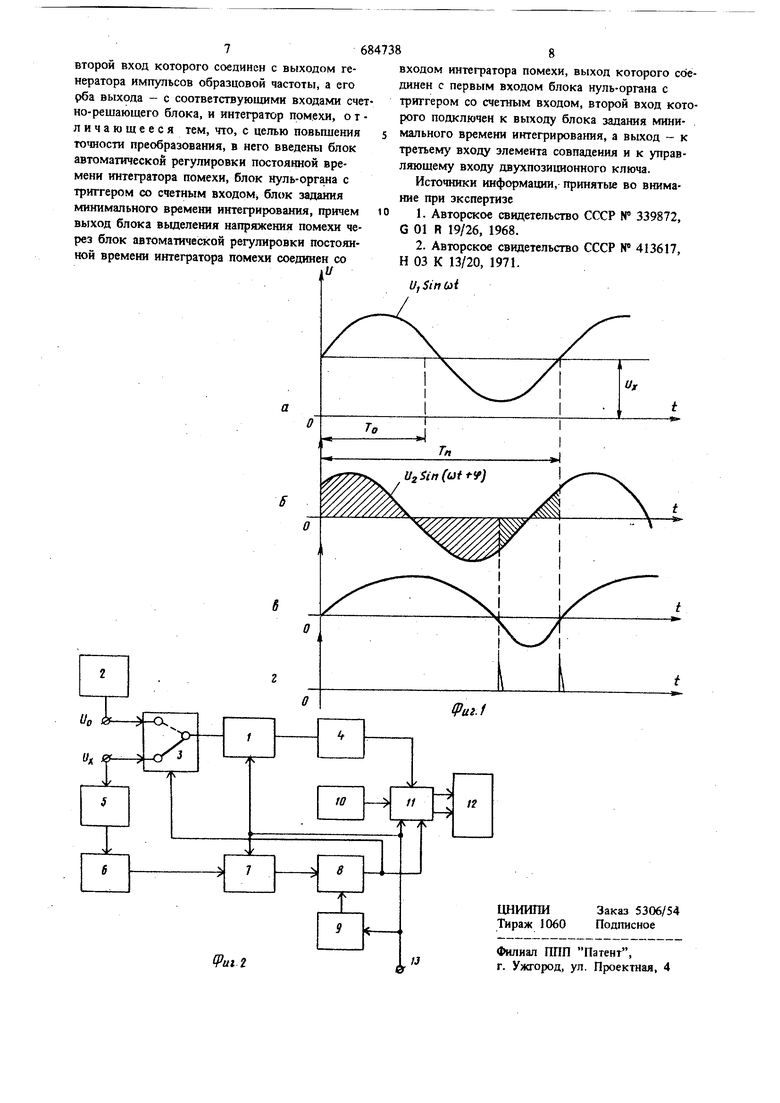

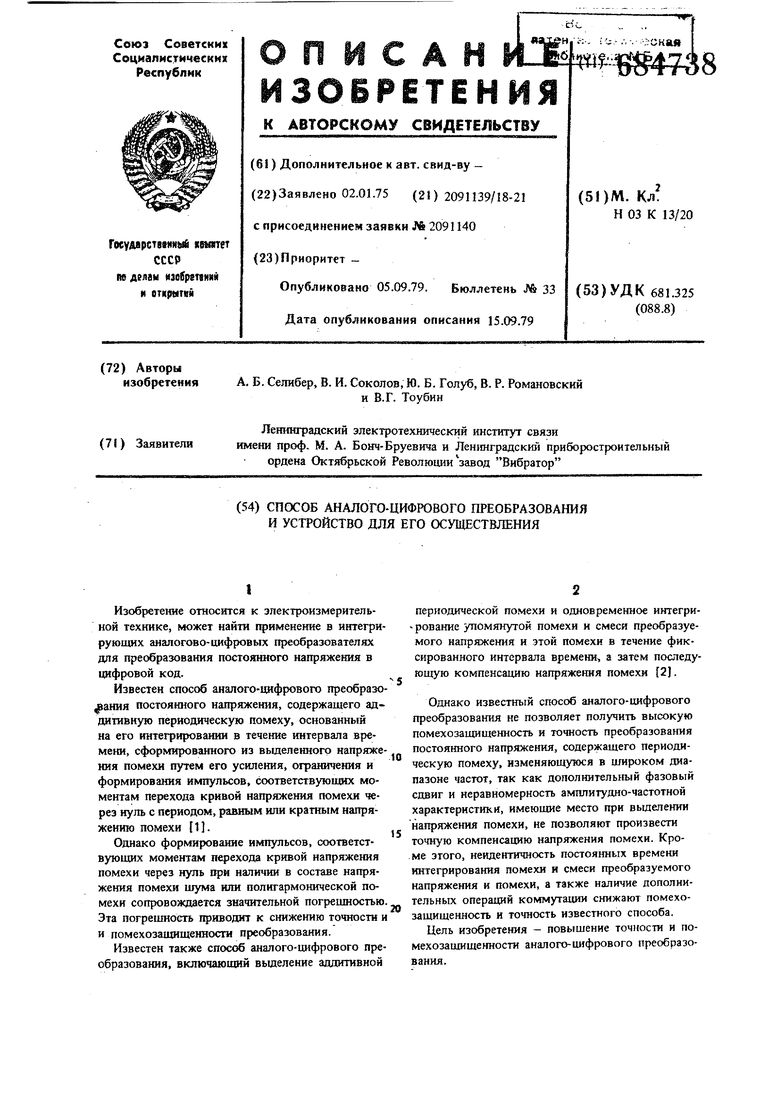

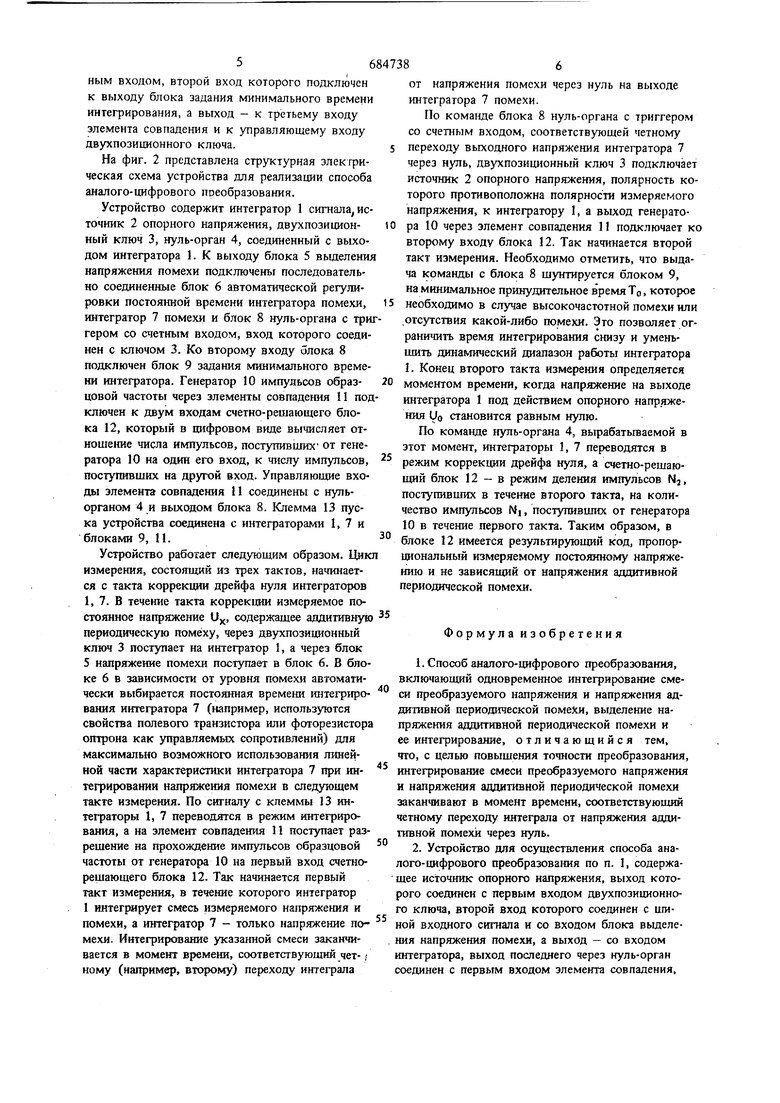

Изобретение относится к электроизмерительной технике, может найти применение в интегри рующих аналогово-цифровых преобразователях для преобразования постоянного напряжения в цифровой код. Известен способ аналого-вдфрового преобразо ания постоянного напряжения, содержащего аддитивную периодическую помеху, основанный на его интегрировании в течение интервала времени, сформированного из вьщеленного напряже ния помехи путем его усиления, ограничения и формирования импульсов, соответствующих моментам перехода кривой напряжения помехи через иуль с периодом, равным или кратным напряжению помехи 1. Однако формирювание импульсов, соответствующих моментам перехода кривой напряжения помехи через нуль при наличии в составе напряжения помехи шума или полигармонической помехи сопровождается значительной погрешностью Эта погрешность приводит к снижению точности и и помехозащищенности преобразования. Известен также способ аналого-цифрового пре образования, включающий вьщеление аддитивной периодической помехи и одновременное интегрирование упомянутой помехи и смеси преобразуемого напряжения и этой помехи в течение фиксированного интервала времени, а затем последующую компенсацию напряжения помехи 2. Однако известный способ аналого-цифрового преобразования не позволяет получить высокую помехозащищенность и точность преобразования постоянного напряжения, содержащего периодическую помеху, изменяющуюся в широком диапазоне частот, так как дополнительный фазовый сдвиг и неравномерность амплитудно-частотной характеристики, имеющие место при вьщелении напряжения помехи, не позволяют произвести точную компенсацию напряжения помехи. Кро,ме зтого, неидентичность постоянных времени интегрирования помехи и смеси преобразуемого напряжения и помехи, а также наличие дополнительных операций коммутации снижают помехозащищенность и точность известного способа. Цель изобретения - повышение точности и помехозащищенности аналого-цифрового преобразования. 368 Посташгенная цель достигается тем, что при аналого-цифровом преобразовании предлагаемым способом включающим одновременное интегрирование смеси преобразуемого напряжения и напряжения аддитивной периодической помехи, а также выделение напряжения аддитивной периодической помехи и ее ин.тегрирование,интегрирование смеси преобразуемого напряжения и напряжения аддитивной периодической помехи заканчивают в момент времени, соответствующий четному переходу интеграла от напряжения аддитивной помехи через нуль, причем постоянную времени интегрирования выбирают в з(ависимости от уровня помехи. Способ состоит в следующем. Из суммы преобразуемого постоянного напряжения и периодической помехи выделяют напряжение помехи и одновременно раздельно интегрируют помеху и указанную сумму. Интегрирование происходит в течение некоторого принудительного времени TO, необходимого при высокочастотной помехе или при отсутствии какой-либо помехи. Заканчивают интегрирование в момент времени TI, соответствующий четному (например, второму) переходу интеграла от напряжения помехи через нуль Система уравнений, соответствующая операциям интегрируемой суммы преобразуемого напряжения помехи, имеет вид: j (UxHJismwt)dt r-Ti -i- г Uzsin (a) Сд о где т 1, г 2 - постоянные времени интегрирования смеси постоянного напряжения и напряжения помехи и отдельного интегрирования напряжения помехи соответственно; Uj( - преобразуемое постоянное напряжение; Uisrncot - напряжение помехи частотой u) (Тд - период помехи) с амлитудой Ui Ujsin(tJt+() - напряжение помехи после вы деления из смеси преобразуемого напряжения и напряжения помехи с амплитудой Uj и дополнительным фазовым сдвигом ip. Рещение первого уравнения системы относи: тельно TI дает значение TI -г- TH, а второе уравнение имеет два корня: TI Тд -| и TI Тд. Общим корнем системы является значение TI Tjj, т. е. период напряжения помехи. Так как второе уравнение- имеет два корня, то останавливая интегрирование смеси преобразуемо го напряжения и помехи по четному (второму) переходу интеграла от напряжения помехи через нуль, получаем время интегрирования, равное периоду помехи независимо от дополнительного фазового с/щига, вносимого при выделении помехи. Таким образом, результат интегрирования указанной смеси не зависит от напряжения по- . мехи. Этот вывод справедлив и для полигармонической помехи, но при линейной фазочастотной характеристике устройства, выделяющего напряжение помехи. Так как точность определения нуля интеграла от напря:«ения помехи зависит от скорости нарастания и спада напряжения помехи, т. е. от производной напряжения помехи по времени, то при постоянных частоте помехи и пороге срабатывания устройства определения нуля интеграла от напряжения помехи она прямо пропорциональна амплитуде напряжения помехи. Поэтому перед интегрированием напряжения помехи автоматически выбирают постоянную времени в зависимости от уровня помехи (например, используя свойства полевого транзистора или фоторезисгора оптрона как управляемых сопротивлений), добиваясь этим максимально возможного использования линейной части характеристики устройства, интегрирующего помеху. На фиг. 1 а, б, в, г приведены временные диаграммы изменения напряжений, поясняющие , причем на фиг. а - аддитивная смесь преобразуемого напряжения и помехи; йа фиг. 16напряжение помехи после вьщеления (штриховыми линиями показаны соответственно одинаковые площади); йа фиг. 1 в - изменение интегрального значения напряжения помехи во времени; на фиг. 1 г - импульсы, соответствующие моментам перехода интеграла от напряжения помехи через нуль. Для аналого-цифрового преобразования может служить устройство, содержащее источник опорного напряжения, вход которого соединен с первым входом двзоспозиционного ключа, второй вход которого соединен с щиной входного сигнала и со входом блока выделения напряжения помехи, а выход - со входом интегратора, выход последнего через нуль-орган соединен с первым входом элемента совпадения, второй вход которого соединен с выходом генератора импульсов образцовой частоты, а его оба выхода - с соответствующи1ъа{ входами счетно-рещающего блока и интегратор помехи. В зто устройство введены блок автоматической регулировки постоянной времени интегратора помехи, блок нуль-органа р триггером со счетным входом, блок задания минимального времени интегрирования, причем вход блока выделения напряжения помехи через блок автома-. тической регулировки постоянной времени интегратора помехи-соедшгн со входом интегратора помехи, выход которого соединен с первым входом блока нуль-органа с триггером со счетным входом, второй вход которого подключен к выходу блока задания лтнимального времени интегрирования, а выход - к третьему входу элемента совпадения и к управляющему входу двухпозиционного ключа. На фиг. 2 представлена структурная элекфическая схема устройства для реализации способа аналого-цифрового поеобразования. Устройство содержит интегратор 1 сигнала, источник 2 опорного напряжения, двухпозиционный ключ 3, нуль-орган 4, соединенный с выходом интегратора 1. К выходу блока 5 вьщеления напряжения помехи подключены последовательно соединенные блок 6 автоматической регулировки постоянной времени интегратора помехи, интегратор 7 помехи и блок 8 нуль-органа с три гером со счетным входом, вход которого соединен с ключом 3. Ко второму входу олока 8 подключен блок 9 задания минимального времени интегратора. Генфатор 10 импульсов образцовой частоты через элементы совпадения 1 i под ключен к двум входам счетно-рептающего блока 12, который в цифровом виде вычисляет отношение числа импульсов, поступивших от генератора 10 на один его вход, к числу импульсов, поступивших на другой вход. Управляющие входы элемента совпадения 1 соединены с нульорганом 4 и выходом блока 8. Клемма 13 пуска устройства соедашена с интеграторами 1, 7 и блоками 9, 11. Устройство работает следующим образом. Цик измерения, состоящий из трех тактов, начинается с такта коррекции дрейфа нуля интеграторов 1, 7. В течение такта коррекции измеряемое постоянное напряжение Uj(, содержащее аддитивную периодическую помеху, через двухпозиционный ключ 3 поступает на интегратор 1, а через блок 5 напряжение помехи поступает в блок 6. В блоке 6 в зависимости от уровня помехи автоматически выбирается постоянная времени интегрирования интегратора 7 (например, используются свойства полевого транзистора или фоторезистора оптроиа как управляемых сопротивлений) для максимально возможного использования линейной части характеристики интегратора 7 при интегрировании напряжения помехи в следующем такте измерения. По сигналу с клеммы 13 интеграторы 1, 7 переводятся в режим интегрирования, а на элемент совпадения 11 поступает разрешение на прохождение импульсов образцовой частоты от генератора 10 на первый вход счетнорешающего блока 12. Так начинается первый такт измерения, в течение которого интегратор 1 интегрирует смесь измеряемого напряжения и помехи, а интегратор 7 - только напряжение помехи. Интегрир вание указанной смеси заканчивается в момент времени, соответствующий чет-; ному (например, второму) переходу интеграла ОТ напряжения помехи через нуль на выходе интегратора 7 помехи. По комаЕще блока 8 нуль-органа с триггером со счетным входом, соответствующей четному переходу выходного напряжения интегратора 7 через нуль, двухпозиционный ключ 3 подключает источник 2 опорного напряжения, полярность которого противоположна полярности измеряемого напряжения, к интегратору 1, а выход генератора 10 через элемент совпадения И подключает ко второму входу блока 12. Так нащшается второй такт измерения. Необходимо отметить, что выдача команды с блока 8 шунтируется блоком 9, на минимальное принудительное время TO , которое необходимо в случае высокочастотной помехи или отсутствия какой-либо томехи. Это позволяет ограничить время интегрирования снизу и уменьшить динамический диапазон работы интегратора I. Конец второго такта измерения определяется моментом времени, когда напряжение на выходе интегратора 1 под действием опорного напряжения УО становится равным нулю. По команде пуль-органа 4, вырабатьгеаемой в этот момент, интеграторы 1, 7 переводятся в режим коррекции дрейфа нуля, а счетно-рещающий блок 12 - в режим деления импульсов N, поступивших в течение второго такта, на количество импульсов NI , поступивших от генератора 10 в течение первого такта. Таким образом, в блоке 12 имеется результирующий код, пропорциональный измеряемому постоянному напряжению и не зависящий от напряжения аддитивной периодической помехи. Формула изобретения 1.Способ аналого-1№фрового преобразования, включающий одновременное интегрирование смеси преобразуемого напряжения и напряже1шя аддитивной периодической помехи, выделение напряжения аддитивной периодической помехи и ее интегрирование, отличающийся тем, что, с целью повышения точности преобразования, нтегрирование смеси преобразуемого напряжения напряжения аддитивной периодической помехи заканчивают в момент времени, соответствующий етному переходу интеграла от напряжения аддиивной помехи через нуль. 2.Устройство для осуществления способа анаого-цифрового преобразования по п. 1, содержаее источник опорного напряжения, выход котоого соединен с первым входом двухпозиционноо ключа, второй вход которого соединен с шиой входаого сигнала и со входом блока вьщелеия напряжения помехи, а выход - со входом нтегратора, выход последнего через нуль-орган оединен с первым входом элемента совпадения,

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ аналого-цифрового преобразования | 1978 |

|

SU723771A1 |

| Интегрирующий аналого-цифровой преобразователь | 1984 |

|

SU1314457A1 |

| Способ аналого-цифрового преоб-РАзОВАНия и уСТРОйСТВО для ЕгООСущЕСТВлЕНия | 1979 |

|

SU839050A1 |

| Способ аналого-цифрового преобразования | 1981 |

|

SU1160920A1 |

| Устройство для измерения температуры | 1984 |

|

SU1268970A1 |

| Режекторный фильтр | 1987 |

|

SU1429293A2 |

| Цифровой измеритель температуры | 1988 |

|

SU1583757A1 |

| Устройство для измерения температуры | 1987 |

|

SU1490504A1 |

| Аналого-цифровой преобразователь | 1989 |

|

SU1697265A1 |

| Аналого-цифровой преобразователь двухтактного интегрирования | 1988 |

|

SU1515367A2 |

Авторы

Даты

1979-09-05—Публикация

1975-01-02—Подача