(54) АНАЛОГО-ЦИФРОВОЙ ЬНТЕГРАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ интегрирующего аналого-цифрового преобразования и устройство для его осуществления | 1985 |

|

SU1381709A1 |

| Интегратор | 1980 |

|

SU922786A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ СОВМЕЩЕННОГО ИНТЕГРИРОВАНИЯ | 1992 |

|

RU2036559C1 |

| Интегрирующий аналого-цифровой преобразователь | 1989 |

|

SU1633493A1 |

| Множительно-делительное устройство | 1977 |

|

SU696444A1 |

| Аналого-дискретное интегрирующее устройство | 1975 |

|

SU556463A1 |

| Аналого-цифровой интегратор | 1978 |

|

SU805345A1 |

| Цифровой измеритель температуры | 1988 |

|

SU1583757A1 |

| Способ преобразования угла поворота вала в код и устройство для его осуществления | 1989 |

|

SU1713103A1 |

| Устройство для измерения и контроля нелинейности амплитудной характеристики квазилинейных систем | 1981 |

|

SU974298A1 |

1

Изобретение относится к гибридной вычислительной технике и может найти применение при построении гибридных вычислительных устройств, информационно-измерительных и вычислительных систем и комплексов.

Известно устройство для интегрирования, содержащее последовательно соединенные аналоговый интегратор, . компаратор, реверсивный счетчик, цифро-аналоговыйпреобразователь, выход которого подключен к первому входу сумматора, источник задания начальных условий и источник управляющего сигнала, блок управления, вход которого соединен с выходом сумматора, а другой - с источником управляквдего сигнала, дополнительный аналоговый интегратор и ключи, причем выход сумматора соединен через первый ключ с входом аналогового интегратора и через второй с входом дополнительного аналогового интегратора, выход которого соединен с вторым входом cSMMaTopa, третий вход сумматора через третий ключ соединен с источником задания начальных условий, источник управляющего сигнала соединен с управляющим входом третьего ключа и входом установки счетчика в нулевое положение, а выходы блока управления соединены с управляющими -входами первого и с второго ключей и управляющим входом аналогового.интегратора

Наиболее близким по технической сущности к изобретению является ин-

4п тегратор напряжения, содержащий

последовательно соединенные интегрирующий усилитель и сравнивающее устройство, ключи, через первый ключ вход интегрируквдего усилителя соединен с входом устройства, а через

15 второй и третий ключи - с источниками эталонных напряжений, схемы совпадения, схему измерения времени, триггер управления, единичный выход которого подключен к управляквдему входу первого ключа, вход первой схемы

20 совпадения соединен непосредственно с выходом сравнивающего устройства и выходом схемы измерения а вход второй схемы совпадения через

25 интегратор и разрешающие входы схем совпадения подключен к нулевому выходу триггера, а выходы - к управляющим входам второго и третьего ключей, вход схеъва измерения времени подсое

30 динен к входу триггера управления 2 .

Недостатками известных интеграторов являются значительная погрешность интегрирования, связанная с несовпадением конца интервала йнтег рирования с концом физическрго процесса,.а также ограниченные функциональные возможности

Цель изобретения - повышение точности интегрирования и расширение функциональных возможностей за счет автоматического определения знака интеграла.

Поставленная цель достигается тем, что интегратор, содержащий интегрирующий усилитель, вход которого через первый ключ соединен с входом аналого-цифрового интегратора, через второй и третий ключи - с источникам эталонных напряжений и через четвертый ключ подключен к выходу интегрирующего усилителя, соединенному с первым входом первого сравнивающего устройства, второй вход которого с шиной нулевого потенциала, а .выход - с первым входом триггера управления, первый и второй элементы и, первые входы которых соединены с выходами триггера управления, а выходы подключены к управляющим входам второго и третьего ключей, содержит триггер знака, формирователи заданного и действительного времени интегрирования, реверсивный счетчик,третий и четвертый элементы И и второе сравнивающее устройство,входы которого подключены соответственно к источнику опорного напряжения и выходу интегрирующего усилителя, а выход соединен с вторым входом триггера управления, выходы которого соединены соответственно с первыми входами третьего и четвертого элементов И, вторые входы всех элементов И и управляющий вход четвертого ключа, подключены к первому выходу формирователя действительного времени интегрирования, первый вход которого соединен с единичным выходом триггера управления, второй вхоД - с первым выходом формирователя заданного времени интегрирования, второй выход которого подключен к управляющему входу первого ключа, а третий выход соединен с тактовыми входами триггера управления, триггера знака и третьими входами третьего и четвертого элементов И, установочные входы триггеров управления и знака реверсивного счетчика и формирователей действительного и заданного времени интегрирования соединены с установочным входом аналого-цифрового интегратора, управляющие входы которого подключены к входам формирователя заданного времени интегрирования, входы реверсивного счетчика подключены к выходам треть,его и четвертого элементов И,первый.и второй выход - к входам состояния триггера

знака, выход которого является знаковым выходом, а другие выходы реверсивного счетчика - информационными выходами аналого-цифрового интегратора,

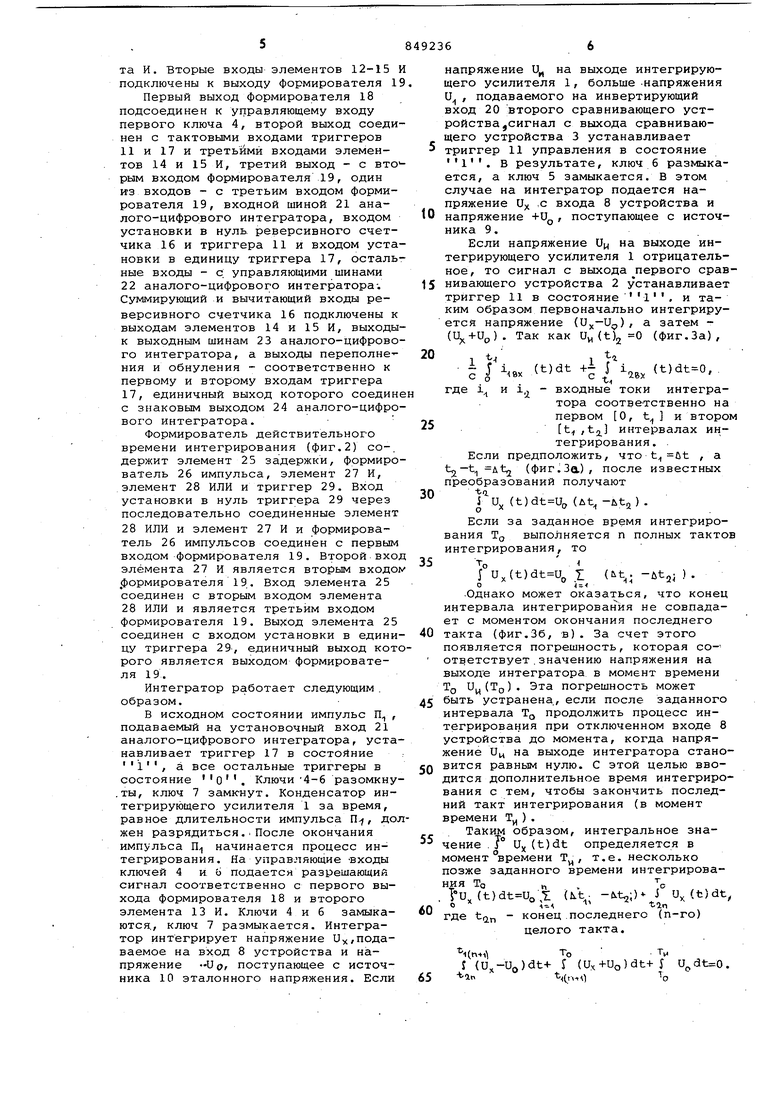

Кроме того, формирователь действительного времени интегрирования содержит элемент задержки, формирователь импульсов, элемент И, элемент ИЛИ и триггер, вход установки в нуль которого через последовательно соединенные элемент ИЛИ, элемент И и .формирователь импульсов соединен с первым входом формирователя действительного времени интегрирования, второй вход элемента И является вторым входом формирователя действительного времени интегрирования, вход элемента задержки соединен с вторым входом элемента ИЛИ и является третьим входом формирователя действительного времени интегрирования, выход элемента задержки соединен с входом установки в единицу триггера, единичный выход которого является выходом формирователя действительного времени интегрирования.

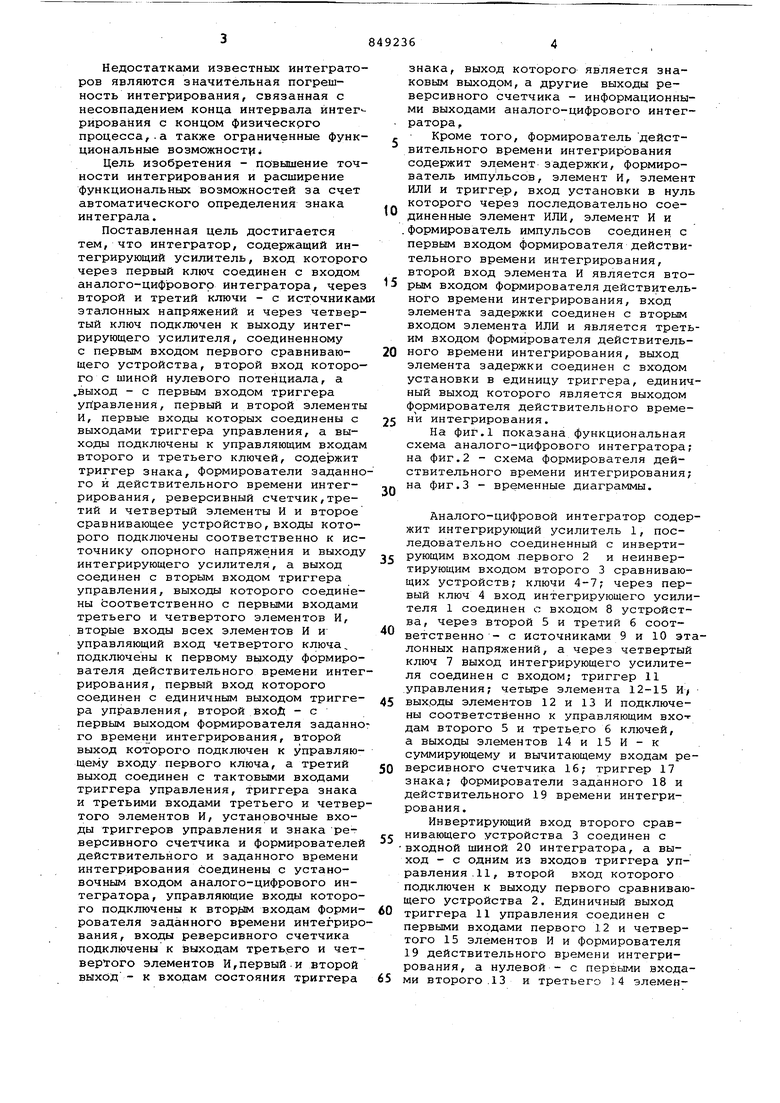

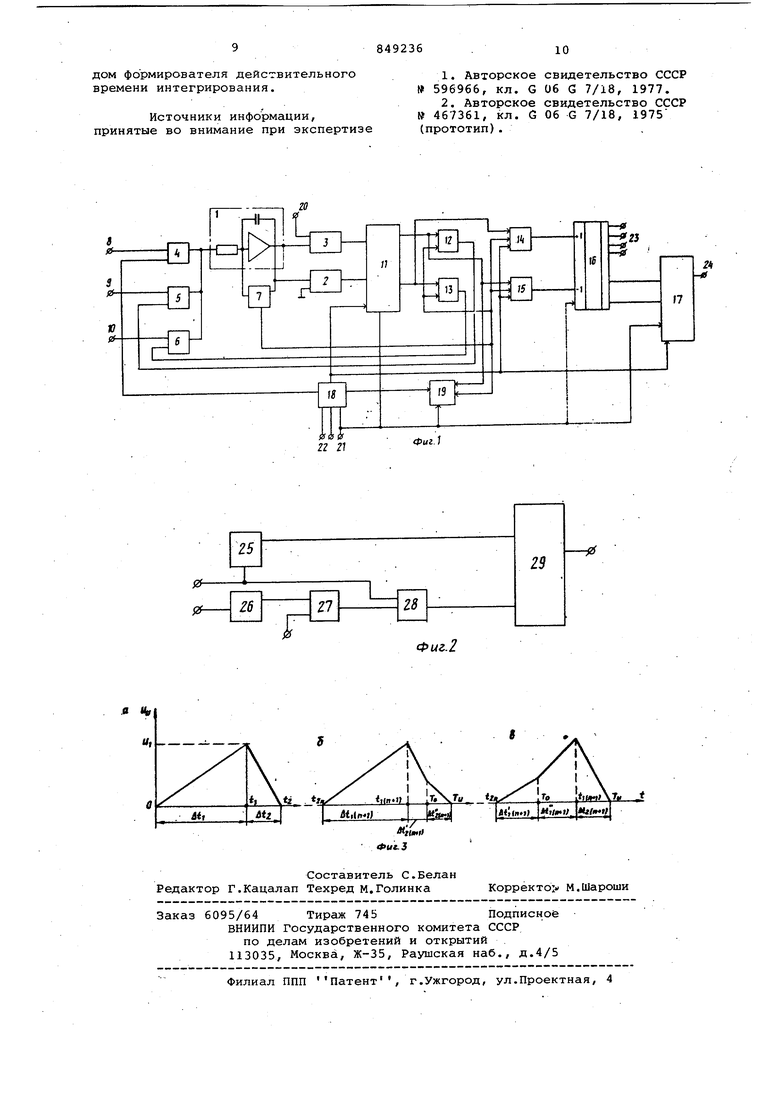

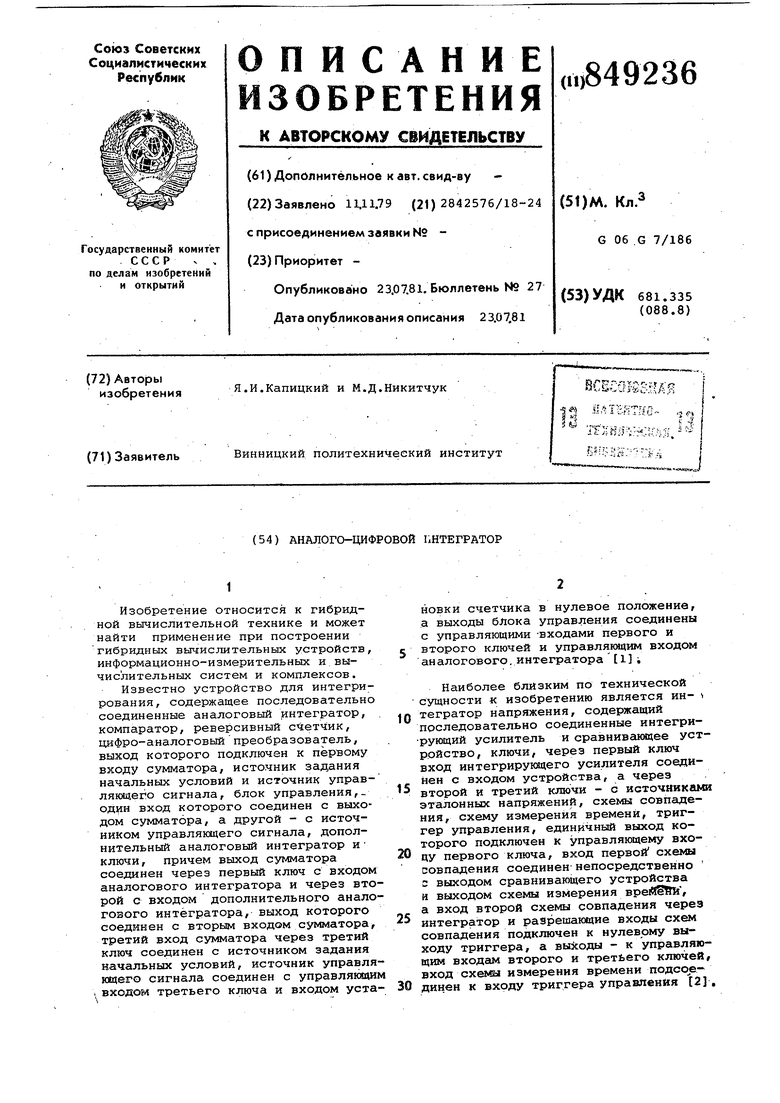

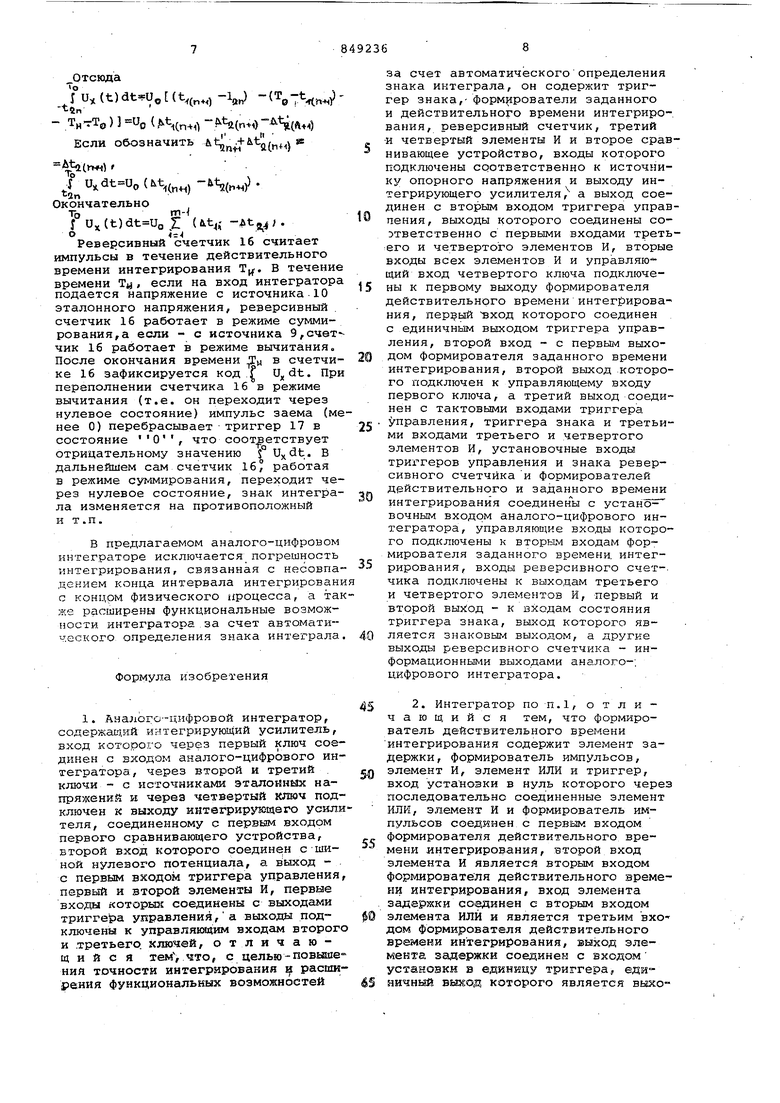

На фиг.1 показана функциональная схема аналого-цифрового интегратора; на фиг.2 - схема формирователя действительного времени интегрирования; на фиг.3 - временные диаграммы.

Аналого-цифровой интегратор содержит интегрирующий усилитель 1, последовательно соединенный с инвертирующим входом первого 2 и неинвертирующим входом второго 3 сравнивающих устройств; ключи 4-7; через первый ключ 4 вход интегрирующего усилителя 1 соединен с входом 8 устройства, через второй 5 и третий б соответственно - с источниками 9 и 10 этлонных напряжений, а через четвертый ключ 7 выход интегрирующего усилителя соединен с входом; триггер 11 управления; четыре элемента 12-15 И/ выходы элементов 12 и 13 И подключены соответственно к управляющим входам второго 5 и третьего б ключей, а выходы элементов 14и15И-к суммирующему и вычитающему входам реверсивного счетчика 16; триггер 17 знака; формирователи заданного 18 и действительного 19 времени интегрирования.

Инвертирующий вход второго сравнивающего устройства 3 соединен с входной шиной 20 интегратора, а выход - с одним из входов триггера управления. 11, второй вход которого подключен к выходу первого сравнивающего устройства 2. Единичный выход триггера 11 управления соединен с первыми входами первого 12 и четвертого 15 элементов И и формирователя 19 действительного времени интегрирования, а нулевой - с первы ли входами второго. 13 и третьего 14 элемента И. Вторые входы элементов 12-15 И подключены к выходу формирователя 19

Первый выход формирователя 18 подсоединен к управляющему входу первого ключа 4, второй выход соединен с тактовыми входами триггеров 11 и 17 и третьими входами элементов 14 и 15 И, третий выход - с вто-рым входом формирователя 19, один КЗ входов - с третьим входом формирователя 19, входной шиной 21 аналого-цифрового интегратора, входом установки в нуль реверсивного счетчика 16 и триггера 11 и входом установки в единицу триггера 17, остальные входы - с; управляющими шинами 22 аналого-цифрового интегратора-. Суммирующий и вычитающий входы реверсивного счетчика 16 подключены к выходам элементов 14 и 15 И, выходык выходным шинам 23 аналого-цифрового интегратора, а выходы переполне ния и обнуления - соответственно к первому и второму входам триггера 17, единичный выход которого соедине с знаковым выходом 24 аналого-цифрового интегратора.

Формирователь действительного времени интегрирования (фиг.2) со-, держит элемент 25 задержки, формирователь 26 импульса, элемент 27 И, элемент 28 ИЛИ и триггер 29. Вход установки в нуль триггера 29 через последовательно соединенные элемент 28 ИЛИ и элемент 27 И и формирователь 26 импульсов соединен с первым входом формирователя 19. Второй вход элемента 27 И является вторым входо. (формирователя 19. Вход элемента 25 соединен с вторым входом элемента 28 ИЛИ и является третьим входом формирователя 19. Выход элемента 25 соединен с входом установки в единицу триггера 29-, единичный выход которого является выходом формирователя 19.

Интегратор работает следующим . образом.

В исходном состоянии импульс П, , подаваемый на установочный вход 21 аналого-цифрового интегратора, устанавливает триггер 17 в состояние , а все остальные триггеры в состояние о. Ключи 4-6 разомкну.ты, ключ 7 замкнут. Конденсатор интегрирующего усилителя 1 за время, равное длительности импульса П-j, должен разрядиться..После окончания импульса П начинается процесс интегрирования. На управляющие -входы ключей 4 и 6 подается разрешающий сигнал соответственно с первого выхода формирователя 18 и второго элемента 13 И. Ключи 4 и 6 замыкаются,, ключ 7 размыкается. Интегратор интегрирует напряжение U,подаваемое на вход 8 устройства и напряжение -и о, поступающее с источника 10 эталонного напряжения. Если

напряжение U на выходе интегрирующего усилителя 1, больше .напряжения и , подаваемого на инвертирующий вход 20 второго сравнивающего устройства сигнал с выхода сравнивающего устройства 3 устанавливает триггер 11 управления в состояние

. В результате, ключ 6 размыкается, а ключ 5 замыкается. В этом случае на интегратор подается напряжение Uy ,с входа 8 устройства и

0 напряжение +0, поступающее с источника 9.

Если напряжение UK на выходе интегрирующего усилителя 1 отрицательное, то сигнал с выхода первого сравнивающего устройства 2 устанавливает

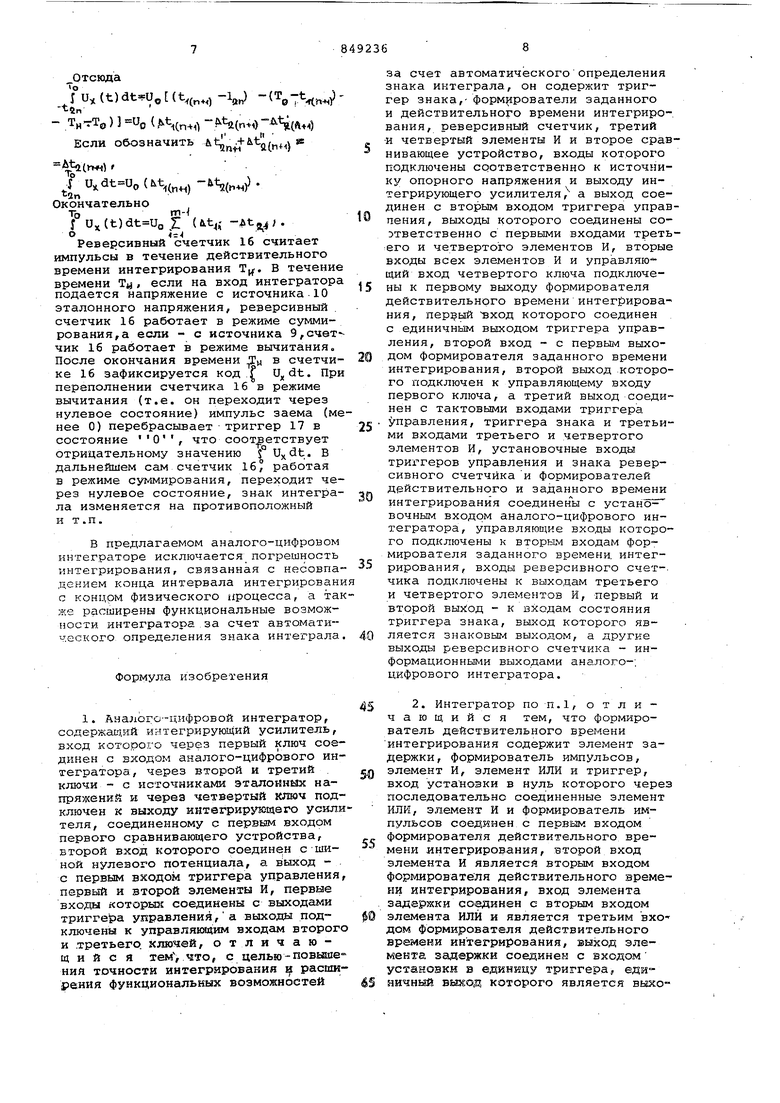

5 триггер 11 в состояние 1. и таким образом первоначально интегрируется напряжение (), а затем (). Так как Uv,(t) (фиг.За),

0

Т.. (t)dt + h,,, (t)dt.o,

где i и i,, - входные токи интегратора соответственно на первом О, t и втором

5 t,t2 интервалах интегрирования.

Если предположить, что , а tj-t At,j (фиг.За), после известных преобразований получают -ьа i и (t) (At., ) .

0

Если за заданное время интегрирования Тг

выполняется п полных тактов

интегрирования, то

;°u,(t) V-,; i.ai

(bt . -uto; ) .

Однако может оказаться, что конец интервала интегрирования не совпадает с моментом окончания последнего такта (фиг.36, в). За счет этого появляется погрешность, которая со-ответствует.значению напряжения на выходе интегратора в момент времени

UU(TC

Эта погрешность может

И

5 быть устранена., если после заданного интервала TQ продолжить процесс интегрирования при отключенном входе 8 устройства до момента, когда напряжение Оц на выходе интегратора становится равным нулю. С этой целью вво0дится дополнительное время интегрирования с тем, чтобы закончить последний такт интегрирования (в момент времени Т ) .

Таким образом, интегральное зна5чение .J° U)((t)dt определяется в момент времени Т , т.е. несколько позже заданного времени интегрирования TO

1и (t) Ut; -bt2;) J u(t)dt

о - tin

ол. л ЬОгч

0

где конец последнего (п-го) целого такта.

l(n-ti|TO.Ту

5 ()dt-(- f (U.x+Uo)dt+J . -it r« lo

5 Отсюда ;°и (t) (t,(,,, -1д -( - TH -гТо) Us, (At,,, - ta(r,-.,} -Ai(ft) Если обозначить ) tl ) -(.) Окончательно y° U (t) l / . о4r Реверсивный счетчик 16 считает импульсы в течение действительного времени интегрирования Т. В течение времени Т, если на вход интегратора подается напряжение с источника 10 эталонного напряжения, реверсивный . счетчик 16 работает в режиме суммирования, а если - с источника 9,счет чик 16 работает в режиме вычитания. После окончания времени счетчи ке 16 зафиксируется код Uj,dt. Пр переполнении счетчика 16 в режиме вычитания (т.е. он переходит через нулевое состояние) импульс заема (м нее 0) перебрасывает триггер 17 в состояние О, что соответствует отрицательному значению S . В дальнейшем сам счетчик 16° работая в режиме суммирования, переходит че рез нулевое состояние, знак интегра ла изменяется на противоположный и т.п. В предлагаемом аналого-цифровом интеграторе исключается погрешность интегрирования, связанная с несовпа .цекием конца интервала интегрирован с концом физического процесса, а та же расширены функциональные возможности интегратора . за счет автоматического определения знака интеграла Формула изобретения

5 2. Интегратор по п.1, о т л и чающийся тем, что формирователь действительного времени интегрирования содержит элемент задержки, формирователь импульсов,

g элемент И, элемент ИЛИ и триггер,

вход установки в нуль которого через последовательно соединенные элемент ИЛИ, элемент И и формирователь импульсов соединен с первым входом формирователя действительного времени интегрирования, второй вход элемента И являетсй вторым входом формирователя действительного времени интегрирования, вход элемента задержки соединен с вторым входом f элемента ИЛИ и является третьим вхо дом формирователя действительного времени интегрирования, выход элемента задержки соединен с входом установки в единицу триггера, единичный выход которого является вьвсоза счет автоматического определения знака интеграла, он содержит триггер знака,- формирователи заданного и действительного времени интегрирования, реверсивный счетчик, третий и четвертый элементы И и второе сравнивающее устройство, входы которого подключены соответственно к источнику опорного напряжения и выходу интегрирующего усилителя, а выход соединен с вторым входом триггера управления, выходы которого соединены соответственно с первыми входами треть:его и четвертого элементов И, вторые входы всех элементов И и управляю щий вход четвертого ключа подключены к первому выходу формирователя действительного времени интегрирования, первый вход которого соединен с единичным выходом триггера управления, второй вход - с первым выходом формирователя заданного времени интегрирования, второй выход которого подключен к управляющему входу первого ключа, а третий выход соединен с тактовыми входами триггера, управления, триггера знака и третьими входами третьего и четвертого элементов И, установочные входы триггеров управления и знака реверсивного счетчика и формирователей действительного и заданного времени интегрирования соединены с устан вочным входом аналого-цифрового интегратора, управляющие входы которого подключены к вторым входам формирователя заданного времени, интегрирования, входы реверсивного счет-, чика подключены к выходам третьего и четвертого элементов И, первый и второй - к входам состояния триггера знака, выход которого является знаковым выходом, а другие выходы реверсивного счетчика - информационными выходами аналого-; цифрового интегратора.

дом формирователя действительного времени интегрирования.

Источники информации, принятые во внимание при экспертизе

свидетельство СССР 06 G 7/18, 1977.

свидетельство СССР 06 G 7/18, 1975

Л

Авторы

Даты

1981-07-23—Публикация

1979-11-11—Подача