1

Изобретение относится к полупроводниковым интегральным микросхемам, в частности к микросхемам с диэлектрической изоляцией компонентов и подложкой из поликристаллического полупроводникового ма териала.

Известны полупроводниковые микросхем межсоединения в которых содержат, по меньшей мере, одно пересечений, представляющее собой легированную примесями область полупроводникового материала. На поверхности этой области размещены два омических контакта, к которым присоединены концы одного межсоединения, а другое межсоединение размещено на диэлектрическом покрытии между омическими контактами. В известных микросхемах с подложкой из поликристаллического кремния и диэлектрической изоляцией компонентов область пересечения размещается в углублении попложки, заполненном монокристаллическим кремнием и изолированном диэлектриком, вследствие чего плотность размещения активных элементов невысока.

Цель изобретения - повыщение плотности расположения элементов интегральной схемы.

Поставленная цель достигается тем, чт пересечения межсоединений размещены непосредственно в подложке из поликристаллического полупроводникового материала, причем область пересечения представляет собой легированную, например, фосфором область поликристаллического кремния подложки.

Удовлетворительные характеристики области пересечения достигаются в случае, если размеры зерен лоликристаллического кремния в этой области не превыщают 2,0 мкм. Высокая воспроизводимость электрофизических характеристик области пересечения достигается при размере зере поликристалличес сого кремния в ней от 10О до 1ОООО А .

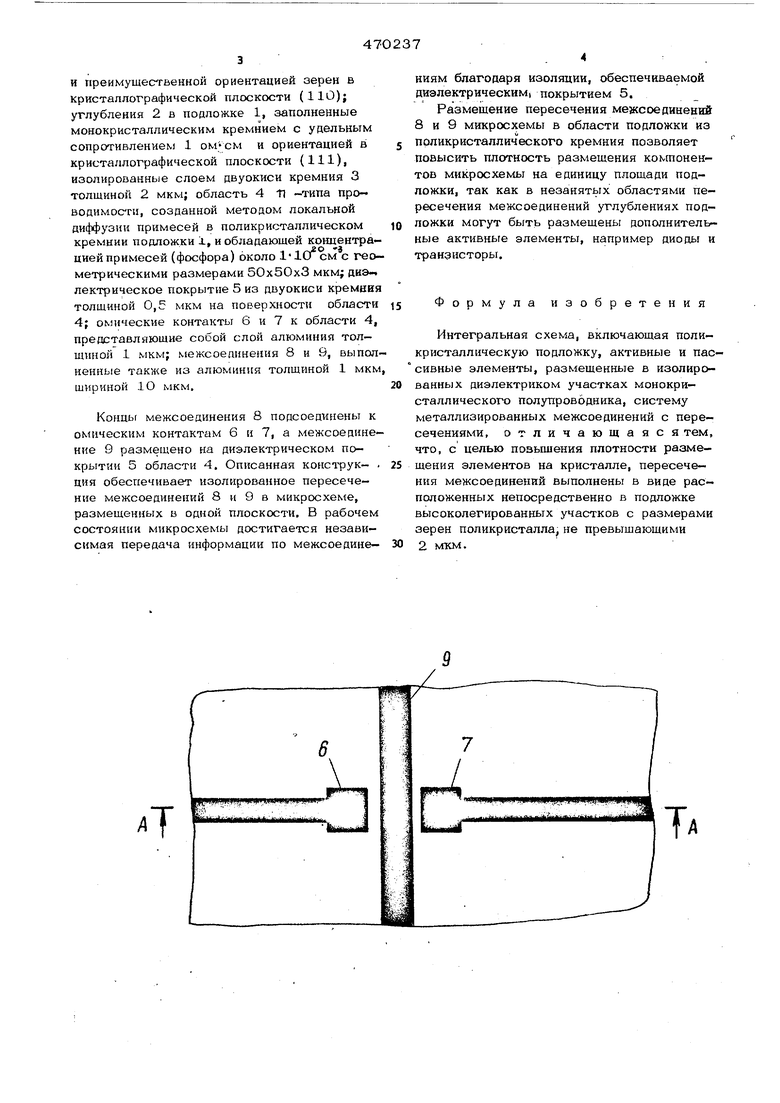

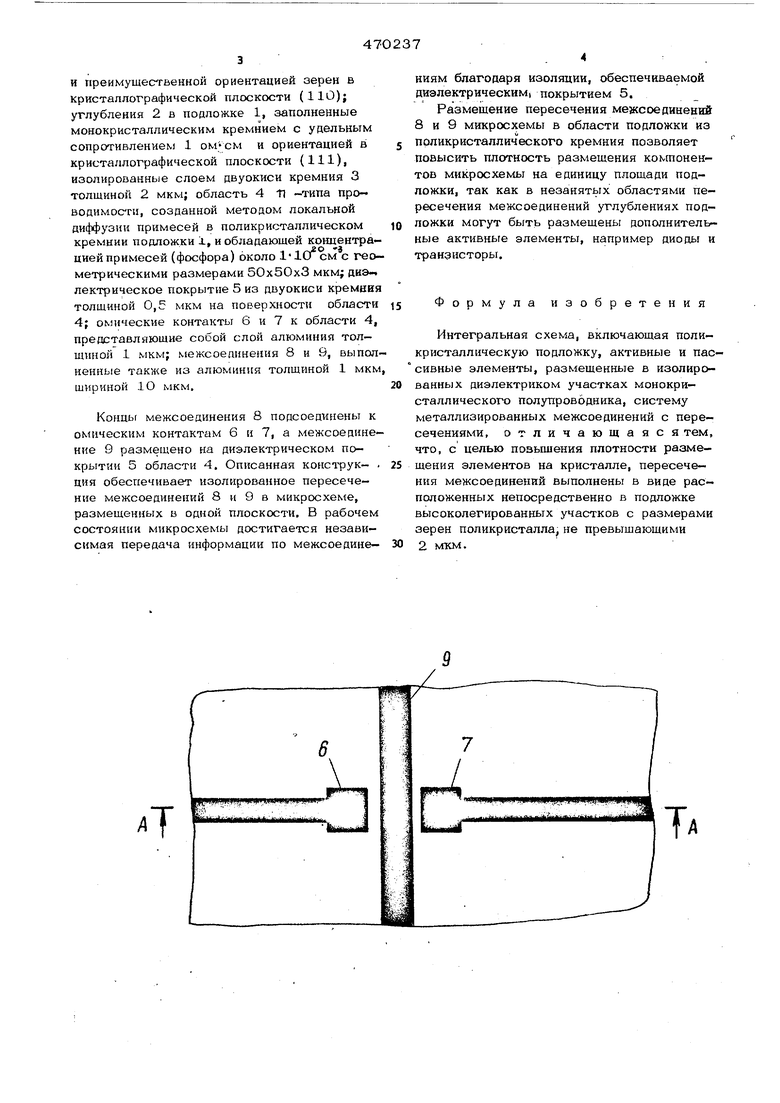

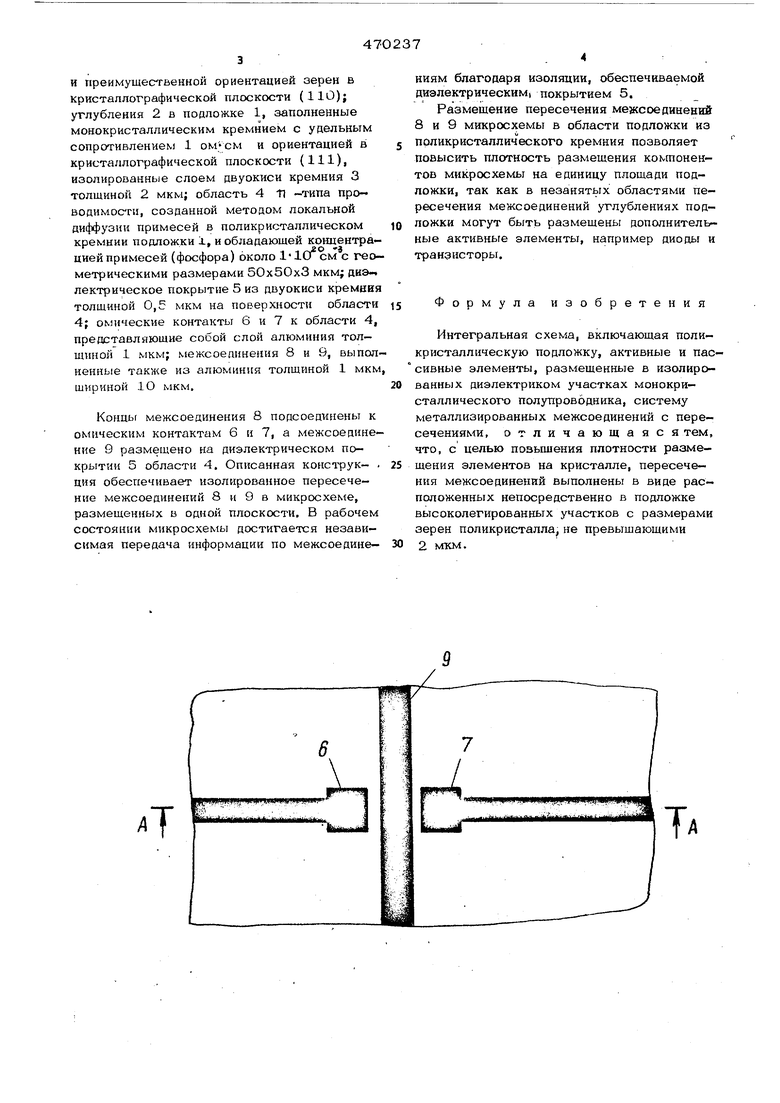

На чертеже показан участок микросхемы с разрезом по Л-А, содержащий подложку 1 из поликрпсталлического кремния с удельным сопротивлением около 2 10 ом-см, размером зерен до 1 мкм

и преимущественной ориентацией зерен в Кристаллографической плоскости (110); углубления 2 в подложке 1, заполненные монокристаллическим кремнием с удельным сопротивлением 1 ом-см и ориентацией в кристаллографической плоскости (111), изолированные слоем двуокиси кремния 3 толщиной 2 мкм; область 4 tl -типа про- водимости, созданной методом локальной диффузии примесей в поликристаллическом кремнии подложки 1, и обладающей концентрацией примесей (фосфора) около 1СГ см с геометрическими размерами 50х5ОхЗ мкм; диэ- лектрическое покрытие 5 из двуокиси кремния толщиной 0,5 мкм на поверхности области 4; омические контакты 6 и 7 к области 4, представляющие собой слой алюминия толщиной 1 мкм; ежсоединения 8 и 9, выполненные также из алюминия толщиной 1 мкм щцриной 1О мкм.

Концы межсоединения 8 подсоединены к омическим контактам 6 и 7, а межсоединение 9 размещено на диэлектрическом покрытии 5 области 4. Описанная консарук- . ция обеспечивает изолированное пересечение межсоединений 8 и 9 в микросхеме, размещенных в одной плоскости, В рабочем состоянии микросхемы достигается независимая передача информации по межсоедине-

ниям благодаря изоляции, обеспечиваемой диэлектрическим, покрытием 5.

Размещение пересечения мегксоединений 8 и 9 микросхемы в области подложки из прликристаллич еского кремния позволяет повысить плотность размещения компонентов микросхемы на единицу площади подложзси, так как в незанятых областями пересечения межсоединений углублениях подложки могут быть размещены дополнительные активные элементы, например диоды и транзисторы.

Формула изобретения

Интегральная схема, включающая поликристаллическую подложку, активные и пассивные элементы, размещенные в изолированных диэлектриком участках монокри- сталлического полупроводника, систему металлизированных межсоединений с пересечениями, отличающаяся тем, что, с целью повьпиения плотности размещения элементов на кристалле, пересечения межсоединений выполнены в виде расположенных непосредственно в подложке высоколегированных участков с размерами зерен поликристалла, не превыщающими 2 мкм.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ИЗГОТОВЛЕНИЯ СТРУКТУР ИС С ДИЭЛЕКТРИЧЕСКОЙ ИЗОЛЯЦИЕЙ | 1989 |

|

SU1690512A1 |

| БОЛЬШАЯ ИНТЕГРАЛЬНАЯ СХЕМА | 1990 |

|

RU2068602C1 |

| ЭЛЕМЕНТ ПАМЯТИ | 1992 |

|

RU2018994C1 |

| СТРУКТУРА - КРЕМНИЙ НА ИЗОЛЯТОРЕ ДЛЯ СБИС (ВАРИАНТЫ) | 1998 |

|

RU2149482C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МИКРОСХЕМ С ДИЭЛЕКТРИЧЕСКОЙ ИЗОЛЯЦИЕЙ ЭЛЕМЕНТОВ | 1990 |

|

SU1686982A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ПОЛУПРОВОДНИКОВЫХ ИНТЕГРАЛЬНЫХ СХЕМ | 1979 |

|

SU760837A1 |

| ИНТЕГРАЛЬНАЯ СХЕМА | 1996 |

|

RU2133067C1 |

| БИПОЛЯРНЫЙ ТРАНЗИСТОР СВЧ | 2012 |

|

RU2517788C1 |

| ГЕТЕРОСТРУКТУРНЫЙ МОДУЛИРОВАНО-ЛЕГИРОВАННЫЙ ПОЛЕВОЙ ТРАНЗИСТОР | 2013 |

|

RU2534437C1 |

| СПОСОБ СОЗДАНИЯ СТРУКТУРЫ - КРЕМНИЙ НА ИЗОЛЯТОРЕ ДЛЯ СБИС (ВАРИАНТЫ) | 1998 |

|

RU2149481C1 |

дТ 8 с 5 a 7 8. л 4iA

Авторы

Даты

1977-07-05—Публикация

1973-08-24—Подача