Изобретение относится к микроэлектронике, в частности к технологии изготовления полупроводниковых приборов и интегральных микросхем.

Известен способ изготовления кремниевых структур для микросхем с высоковольтными транзисторами и диэлектрической изоляцией, включающий формирование защитного покрытия, фотолитографию разделительных канавок, травление разделительных канавок, удаление защитного покрытия, окисление рельефа, фотолитографию окисла в местах нахождения низковольтных транзисторов, отравливание кремния в полученных окнах на необходимую глубину, удаление окисла с рельефа, формирование на полученном рельефе сильнолегированного n-слоя, изолирующего окисление рельефа, эпитаксиальное наращивание поликремниевой подложки, удаление монокристаллической подложки до дна разделительных канавок.

Недостатком этого способа является двукратное локальное травление кремния для разделительных канавок и для утонения "карманов" низковольтных транзисторов, что снижает производительность труда и вносит дополнительные дефекты в рельеф.

Кроме того, так как разделительные канавки изготавливают в начале процесса на глубину, достаточную для формирования высоковольтных транзисторов, разрешающая способность в получении более низковольтных, а значит более мелких участков структуры определяется разрешающей способностью процесса травления глубоких канавок, что приводит к уменьшению плотности упаковки элементов микросхем.

Указанные недостатки частично устранены в способе изготовления микросхем с высоковольтными транзисторами и диэлектрической изоляцией, включающем формирование первого защитного покрытия на кремниевой монокристаллической пластине, фотолитографию разделительных канавок по защитному покрытию, травление разделительных канавок дял высоковольтных транзисторов, удаление защитного покрытия, формирование на полученном рельефе сильнолегированного n-слоя, окисление рельефа, удаление окисла с помощью второй фотолитографии в местах высоковольтных транзисторов, эпитаксиальное наращивание на рельеф кремниевой подложки и удаление монокристаллической подложки до разделительных канавок.

Высоковольтные транзисторы в создаваемых микросхемах частично изолированы от подложки не слоем диэлектрика, а p-n-периодом, что ограничивает сферу применения способа.

Кроме того, глубина травления разделительных канавок в этом способе определяется высоковольтным транзистором и достаточно велика (обычно более 40 мкм), что увеличивает сложность изготовления структур за счет увеличения времени травления и уменьшение плотности упаковки низковольтных транзисторов микросхем.

Цель изобретения - повышение плотности упаковки элементов и упрощение способа за счет уменьшения глубины изолирующих канавок, а также улучшение электрических характеристик микросхем за счет полной диэлектрической изоляции высоковольтных транзисторов.

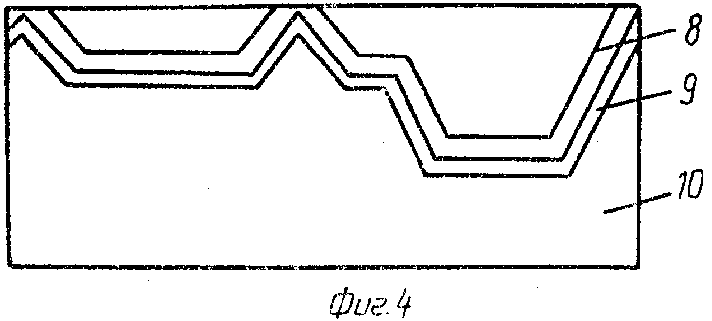

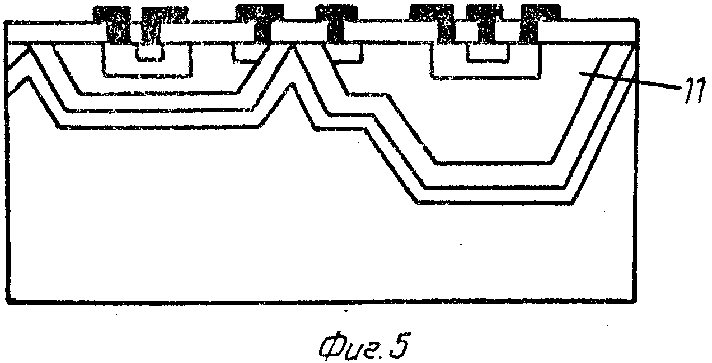

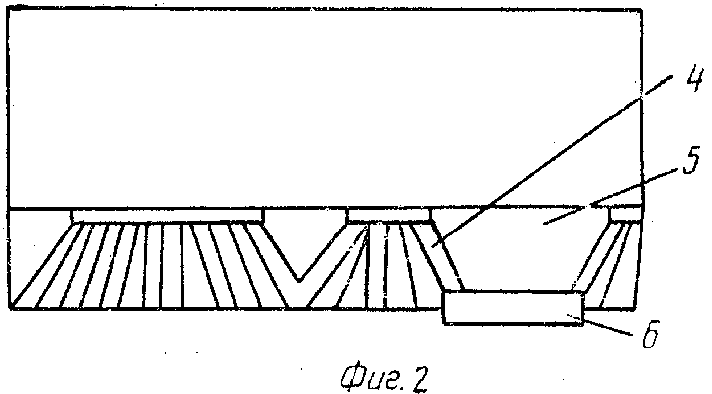

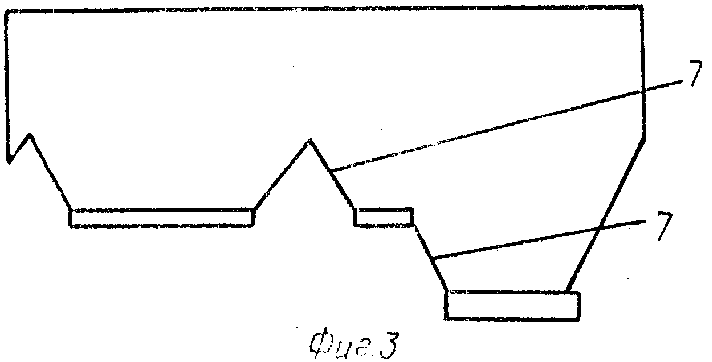

На фиг. 1 показана пластина монокристаллического кремния со сформированной основной защитной планкой; на фиг. 2 - структура после первого этапа эпитаксиального наращивания с локальной маской над участками подложки под высоковольтные транзисторы; на фиг. 3 - структура после травления рельефа; на фиг. 4 - структура после формирования сильнолегированного n+-слоя, окисления, эпитаксии и удаления монокристаллической подложки до дна разделительных канавок; на фиг. 5 - структура с полной диэлектрической изоляцией, содержащая два типа "карманов" с высоковольтными и низковольтными транзисторами.

На фиг. 1-5 приняты следующие обозначения: 1 - пластина монокристаллического кремния; 2 - основная защитная пленка; 3 - место расположения высоковольтного транзистора; 4 - область эпитаксиального поликристаллического кремния под защитным покрытием; 5 - область эпитаксиального монокристаллического кремния под высоковольтным транзистором; 6 - дополнительная защитная пленка; 7 - рельеф; 8 - сильнолегированный n-слой; 9 - термический окисел; 10 - поликристаллический опорный слой; 11 - карман высоковольтного транзистора; 12 - карман низковольтного транзистора.

П р и м е р. На пластину монокристаллического кремния 1 ориентации (100) осаждают слой нитрида кремния 2 толщиной 0,25-0,3 мкм из газовой смеси аммиака и моносилана при 880 ± 20оС и фотолитографией формируют маску, удаляя этот слой в месте расположения высоковольтного транзистора 3 и областях травления рельефа (см. фиг. 1).

Далее проводят первое эпитаксиальное наращивание кремния толщиной 30-40 мкм из газовой смеси SiCl4-H2 при 1200оС. При этом в областях над Si3N4 нарастает поликристаллический кремний (область 4), а под высоковольтным транзистором - монокристаллический кремний (область 5). Проводят наращивание термического окисла толщиной 0,8-1,0 мкм при 1150оС и удаление его методом фотолитографии со всей поверхности кроме областей под высоковольтным транзистором (см. фиг. 2).

Затем проводят анизотропное травление кремния в щелочи с формированием рельефа 7. При этом глубина рельефа в исходной монокристаллической пластине 15-20 мкм, а в областях высоковольтного транзистора на 30-40 мкм больше (см. фиг. 3).

После удаления нитрида кремния и окиси кремния проводят диффузию мышьяка в вакууме при 1150оС с формированием n+-слоя 8 с сопротивлением 6-8 Ом/□. Рельеф заращивают слоем 9 оксида кремния толщиной 1-1,5 мкм, проводят второй этап эпитаксиального наращивания подложки (слой 10).

В качестве основной защитной пленки целесообразно использовать покрытие на основе нитрида кремния, так как такое покрытие не повреждается газовой средой при первом эпитаксиальном наращивании. После формирования первого эпитаксиального слоя монокристалла в местах высоковольтных транзисторов на 0,3-0,8 мкм ниже поликремния на остальной части подложки и резко контрастен в светлом и темном полях микроскопа относительно поликристалла по цвету, что существенно облегчает совмещение областей.

Применение предлагаемого способа по сравнению с прототипом позволяет реализовать полную диэлектрическую изоляцию высоковольтных транзисторов, уменьшить площадь кристалла на примере 32-разрядного высоковольтного коммутатора, состоящего из 32 высоковольтных выходных буферных каскадов и двух низковольтных 32-разрядных триггеров со схемой управления с 8х8 до 7х7 мм2, т. е. на 29% . (56) Патент США N 3412296, кл. 317-234, 1968.

Патент США N 4286230, кл. H 01 L 27/04, 1981.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ИЗГОТОВЛЕНИЯ ВЫСОКОВОЛЬТНЫХ ИНТЕГРАЛЬНЫХ СХЕМ С ДИЭЛЕКТРИЧЕСКОЙ ИЗОЛЯЦИЕЙ | 1990 |

|

SU1739805A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МИКРОСХЕМ С ДИЭЛЕКТРИЧЕСКОЙ ИЗОЛЯЦИЕЙ | 1991 |

|

RU2024108C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ПОЛУПРОВОДНИКОВЫХ ПРИБОРОВ | 1989 |

|

SU1702825A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ КРЕМНИЕВЫХ СТРУКТУР С ДИЭЛЕКТРИЧЕСКОЙ ИЗОЛЯЦИЕЙ КОМПОНЕНТОВ ИНТЕГРАЛЬНЫХ СХЕМ | 1987 |

|

SU1471901A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ИЗОЛЯЦИИ ЭЛЕМЕНТОВ ИНТЕГРАЛЬНЫХ СХЕМ | 1982 |

|

SU1111634A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ КРЕМНИЕВЫХ ТРАНЗИСТОРНЫХ СТРУКТУР С ДИЭЛЕКТРИЧЕСКОЙ ИЗОЛЯЦИЕЙ | 1983 |

|

SU1108966A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ИЗОЛЯЦИИ ЭЛЕМЕНТОВ ИНТЕГРАЛЬНЫХ СХЕМ | 1986 |

|

SU1340500A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ИС НА БИПОЛЯРНЫХ ТРАНЗИСТОРАХ | 1988 |

|

SU1538830A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ТРАНЗИСТОРНЫХ СТРУКТУР С ДИЭЛЕКТРИЧЕСКОЙ ИЗОЛЯЦИЕЙ | 1989 |

|

SU1702826A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МИКРОСХЕМ | 1989 |

|

SU1591750A1 |

Изобретение относится к микроэлектронике, в частности к технологии изготовления полупроводниковых приборов и интегральных микросхем. Цель - повышение плотности упаковки элементов и упрощение способа за счет уменьшения глубины изолирующих канавок, а также улучшение электрических характеристик микросхем за счет полной диэлектрической изоляции высоковольтных транзисторов. Для этого при изготовлении микросхем на поверхности подложки формируют защитную пленку с окнами под области боковой изоляции и области высоковольтных транзисторов. Затем проводят эпитаксиальное наращивание кремния. Поверхность структуры над участками под высоковольтные транзисторы маскируют защитной пленкой. В структуре вытравливают открытые участки кремния с формированием канавок. Поверхность структуры легируют донорной примесью для создания диффузионной области под "скрытый слой", проводят окисление, наращивание поликремния, удаление материала кремниевой подложки до вскрытия дна изолирующих канавок. В монокристаллических карманах создают низковольтные и высоковольтные транзисторы. 5 ил.

СПОСОБ ИЗГОТОВЛЕНИЯ МИКРОСХЕМ С ДИЭЛЕКТРИЧЕСКОЙ ИЗОЛЯЦИЕЙ ЭЛЕМЕНТОВ, включающий формирование на поверхности кремниевой подложки основной защитной пленки, вскрытие в ней окон под области боковой изоляции, вытравливание в окнах изолирующих канавок, удаление основной защитной пленки, формирование на вскрытой поверхности подложки высоколегированного n+-слоя, выращивание пленки оксида кремния путем окисления подложки, вскрытие окон к кремниевой подложке над участками под высоковольтные транзисторы, осаждение поликристаллического кремния, удаление материала кремниевой подложки до вскрытия дна изолирующих канавок и формирование во вскрытых областях кремния низковольтных и высоковольтных транзисторов, отличающийся тем, что, с целью повышения плотности упаковки элементов и упрощения способа за счет уменьшения глубины изолирующих канавок, а также улучшения электрических характеристик микросхем за счет полной диэлектрической изоляции высоковольтных транзисторов, вскрытие окон к кремниевой подложке над участками под высоковольтные транзисторы осуществляют в защитной пленке при вскрытии окон под области боковой изоляции, а перед вытравливанием изолирующих канавок проводят наращивание эпитаксиального слоя над участками под высоковольтные транзисторы и формируют на его поверхности дополнительную защитную пленку, которую удаляют вместе с основной после вытравливания изолирующих канавок.

Авторы

Даты

1994-02-15—Публикация

1990-02-12—Подача