(54)ЦИФРОВОЕ УСТРОЙСТВО ДЛЯ ОПТИМАЛЬНОГО

ИЗМЕРЕНИЯ ЧАСТОТЫ СИГНАЛА

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровое устройство для измерения частоты сигнала | 1980 |

|

SU875292A1 |

| Цифровое устройство для измерения фазы сигнала | 1973 |

|

SU490039A1 |

| Анализатор спектра кардиосигналов | 1975 |

|

SU596888A1 |

| Устройство для измерения центральнойчАСТОТы СпЕКТРА СигНАлА | 1979 |

|

SU813290A1 |

| Цифровой фазометр | 1980 |

|

SU883790A1 |

| Автосчислитель | 1979 |

|

SU836525A1 |

| ЦИФРОВОЕ УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ КОЭФФИЦИЕНТА ГАРМОНИКИ НАПРЯЖЕНИЯ | 1990 |

|

RU2030753C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ СДВИГА ФАЗ СИГНАЛОВ С ИЗВЕСТНЫМ ОТНОШЕНИЕМ ИХ АМПЛИТУД | 1993 |

|

RU2039362C1 |

| УСТРОЙСТЭО ДЛЯ ЦИФРОВОЙ ОБРАБОТКИ РАДИОСИГНАЛОВ | 1970 |

|

SU278228A1 |

| Цифровой измеритель показателей качества электрической энергии трехфазной сети | 1988 |

|

SU1633368A1 |

1

Изобретение относится к области ра- диоизмерительной техники и может быть использовано в радиолокации (радионавигации, радиоуправлении и т. д.) и других областях техники, где необходимо изме- 5 рение частоты электрических сигналов на фоне шумов.

Известно устройство оптимального из мерения частоты, которое выполняет операции свертки принимаемого сигнала сю ожидаемым сигналом, детектирования и вычисления рассогласования между принятым и ожидаемым сигналами.

При аналоговом исполнении известное устройство обладает рядом недостатков, |5 затрудняющих использование этих устройств при точньк измерениях частоты. Например,, с помощью аналоговой аппаратуры практи-. чески невозможно сформировать опорный сигнал со строго заданными параметрами, 20 либо построить фильтр, импульсная реакция которого точно соответствовала бы временному представлению сигнала, кроме ого, параметры аналоговых устройств юдвержены изменениям под влиянием ок- 26

|ружающей среды. Существенным недостатком является также невозможность использования указанных устройств при работе с сигналами различной формы. Переход от одного вида, сигнала к другому требует существенной аппаратурной переработки.

Цель изобретения - повышение точности и расширение функциональных возможнотей устройства.

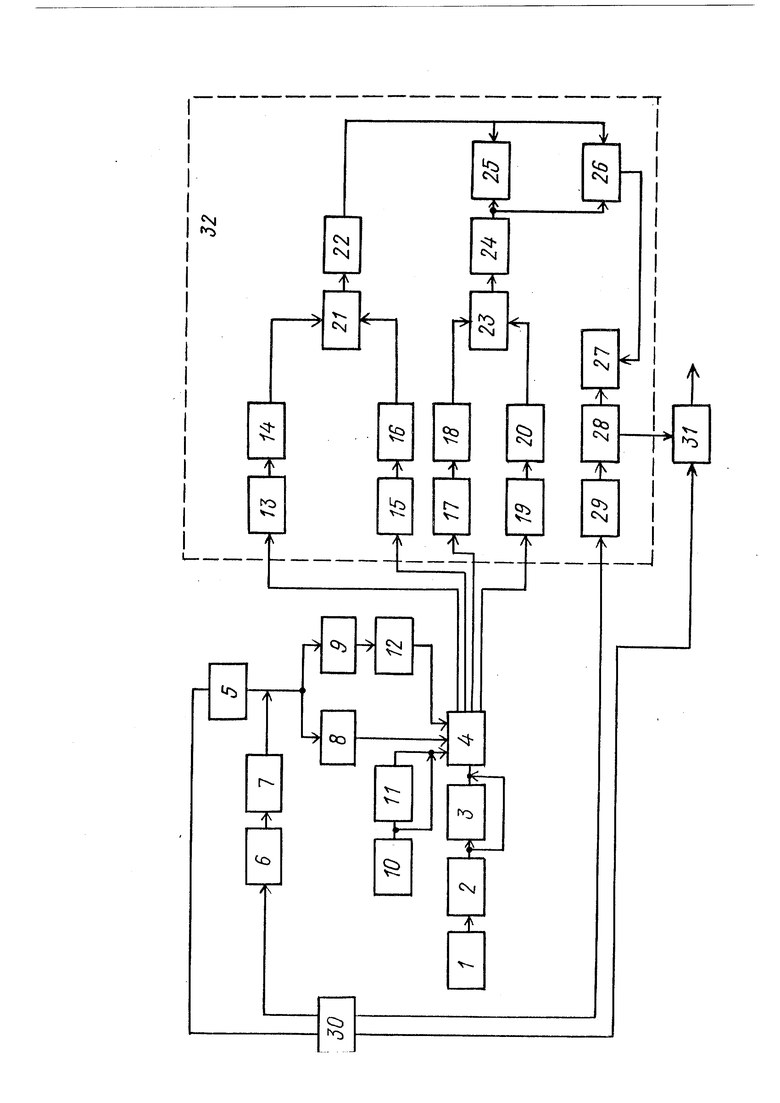

Эта цель достигается тем, что предлагаемое устройство снабжено двумя генераторами аргументов, генератором амплитуд, четырьмя регистрами, тригонометрическими преобразователями функций синус и косинус и сумматором, причем вход блока умножения соединен с выходом преобразователя аналог-код непосредственно и через первый регистр, второй вход умножителя подключен к генератору амплитуд непосредственно и через второй регистр, третий Вход умножителя через последовательно соединенные тригонометрический преобразователь функции синус и первый генератор аргументов соединен с первь1М выходом блока управления, четвертый вход блока умножения через последовательно со диненные третий регистр и тригонометрический преобразователь функции косинус подключен к выходу первого генератора аргументов, который через последователь но соединенные четвертый регистр и второй генератор аргументов под;;лючен ji: к второму вьгкоду блока у1травленЖя7 при этом выходы блока умножения соединены с входами решающего устройства, вькод которого подключен к одному из входов сумматора, а второй вход сумматора соединен с третьим вькодом блока управле- ния, четвертый выход которого подключен к одному из входов решающего устройст- ва. Для реализации операций амплитудночастотного дискриминатора рещающее ycT ройство снабжено четьфьмя накопителями четырьмя квадраторами, тремя сумматорами Двумя блоками извлечения квадрат ного корня, блоком вычитаниЯа блоком вычисления отношения, блоком умножения и формирователем коэффициентов, причем выходы первого и второго накопителей через первый и второй квадратор подключены к входам первого сумматора а вьосоды третьего и четвертого накопи- 1телей через третий и четвертый квадраторы соединены с входами второго сумм тора, выход которого через блок извлечения квадратного корня подключен к вхо ду третьего сумматора и входу блока вы читания, второй вход которого соединен со вторым входом третьего сумматора и через второй блок извлечения квадратного корня с выходом первого сумматора, при этом выход третьего ьумматора через блок вычисления отношения подклю чен к входу блока умножения, второй вхо которого соединен с выходом формирователя коэффициентов, а вь1ход блока вььчитания соединен со входом блока вььI числения отношения. На чертеже изображена блок-схема предлагаемого устройства. Устройство содержит полосовой фильтр 1, преобразователь аналог-код 2, регист 3, множительное устройство 4, генераторы аргументов 5 и 6, регистр 7, тригонометрические преобразователи 8 и 9, генератор амплитуд 10, регистры 11 и 12, накопитель 13, квадратор 14, наконитель 15, квадратор 16, наконителЬ 17 квадратор 18, наксиоггепь 19, Iceaflpa TOp 20, суммато)) 21, блок извлечения квадратного корня 22, сумматор 23, блок j извлечения квадратного корня 24, вычитающее устройство 25, сук-тматор 26, блок вычисления отношенщ 27, множительное устройство 28, формирователь коэффициентов 29, управляющее устройство 30, сумматор 31 и решающее устройства 32. Цифровое устройство для оптимального измерения частоты сигнала работает следующим образомВходной сигнал U(t)-U(t)cos(2f/i д , где f подлежащая измерению частоты сигнала, .после прохождения полосового фильтра 1 кодируется в преобразователе 2 вI дискретные моменты времени « Интервал дискретизации Д1 , из условия дискретизации узкополосных сигналов равен ui Тдр F - полоса пропускания полосового фильтра 1. Синхронно с временным квантованием входного сигнала в генераторах аргументов 5 и 6 в моменты времени Ut формируются аргументы If 21 fo + Д f ) ku tи 45.-2lI(fo-4f)kat, где f ожидаемое значение частоты сигнала, Suf - ширина частотного дискриминатора. Формирование аргументовf и |1„осушеств|ляется по программе, задаваемой управляющим устройством 30. В тригонометрических преобразователях 8 и 9 формируются функции .Ti(f0-t-4f )kat:i и ( ) kA t J. которые последовательно BO времени (функции COS f запоминается в регистре 12) поступают на множительное устройство 4, где перемножаются со значением кода k - ОИ выборки сигнала NLk и с ожидаемой амплитудой сигнала , формируемой в генераторе амплитуд 10. С выхода множительного устройства величины e k N klu k sinLaf()kAtl i ALk N k u klcos a1T(fotuf)kAt поступают в накопители 13 и 15. Затем в множительном устройстве 4 вычисляются- величины 8,k N klulklsm 2li (fo-4f )kAt ; Ai k -Ntklulk cos 2ir(fo-Af)kAt посредством умножения запомненных в регистрах 3 и 11 изначений NLk и и К на функции COS и 51П аргумента „ , запомне1П{ого в регистре 7. Вььчисленные значения A,I.k U поступают в накопители 17 и 19. Время вь1числения величин Alk , , е, превышает интервала дискретизации входного сигнала Д t .

Авторы

Даты

1975-07-25—Публикация

1972-10-06—Подача