(21)4442088/24

(22)15.06.88

(46) 07.03.91. Бкш. № 9

(71)Запорожский машиностроительный институт им. В.Я. Чубаря

(72)В.Я. Майер (SU), Зения (MG) и Л.Л. Петровская (SU)

(53)681.325 (088.8)

(56)Авторское свидетельство СССР № 1307396, кл. G 01 R 29/16, 1985.

Авторское свидетельство СССР № 951192, кл. G 01 R 29/16. 1980.

(54)ЦИФРОВОЙ ИЗМЕРИТЕЛЬ ПОКАЗАТЕЛЕЙ КАЧЕСТВА ЭЛЕКТРИЧЕСКОЙ ЭНЕРГИИ ТРЕХФАЗНОЙ СЕТИ

(57)Изобретение относится к области контроля качества электроэнергии систем электроснабжения. Измеритель, позволяет измерять симметричные составляющие коэффициенты несинусоидальности, нулевой и обратной последовательностей и отклонение напряжений. Этот измеритель также может служить

в качестве анализатора гармоник в промышленной сети. Измеритель состо2

ит из масштабного преобразователя, преобразователем аналог - кол,, блоков памяти, коммутаторов фаз, счетчиков, постоянных запоминающих устройств, умножителей, блоков реализации функции синуса, блоков льщеле- ния кодов двух крайних значений ординат, блоков сумматоров накопителей, сумматоров, кяадраторов, блоков управления, блоков деления кодов, определителя знака, блоков выделения постоянных оставляюисих, блока выделения первой гармоники, блоков извлечения квадратного корня, источника опорного напряжения и блока регистрт- ции. Работа измерителя состоит и трех этапов, на первом из которых производится дискретное преобразога- ние входных сигналов, на втором - вычисление амплитуд и фаз гармоник этих сигналов, в результате чего на третьем этапе вычисляются симметричные составляющие и показатели качества электроэнергии трехфазной сети , 1 ил

«

(/

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЕ УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ КОЭФФИЦИЕНТА ГАРМОНИКИ НАПРЯЖЕНИЯ | 1990 |

|

RU2030753C1 |

| Цифровой измеритель симметричных составляющих напряжений в трехфазной промышленной цепи | 1980 |

|

SU951192A1 |

| Ифровое устройство для оптимального измерения частоты сигнала | 1972 |

|

SU478261A1 |

| Устройство для моделирования удара твердых тел | 1988 |

|

SU1567889A2 |

| Синусно-косинусный преобразователь | 1986 |

|

SU1327095A1 |

| Синусно-косинусный преобразователь | 1981 |

|

SU1005040A1 |

| Устройство для решения уравнения Кеплера | 1989 |

|

SU1615737A1 |

| Синусно-косинусный преобразователь | 1986 |

|

SU1330628A1 |

| Устройство для вычисления функций синуса и косинуса | 1987 |

|

SU1494002A2 |

| Цифровой вычислитель функций | 1986 |

|

SU1354187A1 |

Изобретение относится к автоматике и вычислительной технике и может быть и использовано для контроля качества электроэнергии систем электроснабжения .

Цель изобретения - повышение точности измерений и расширение области применения измерителя.

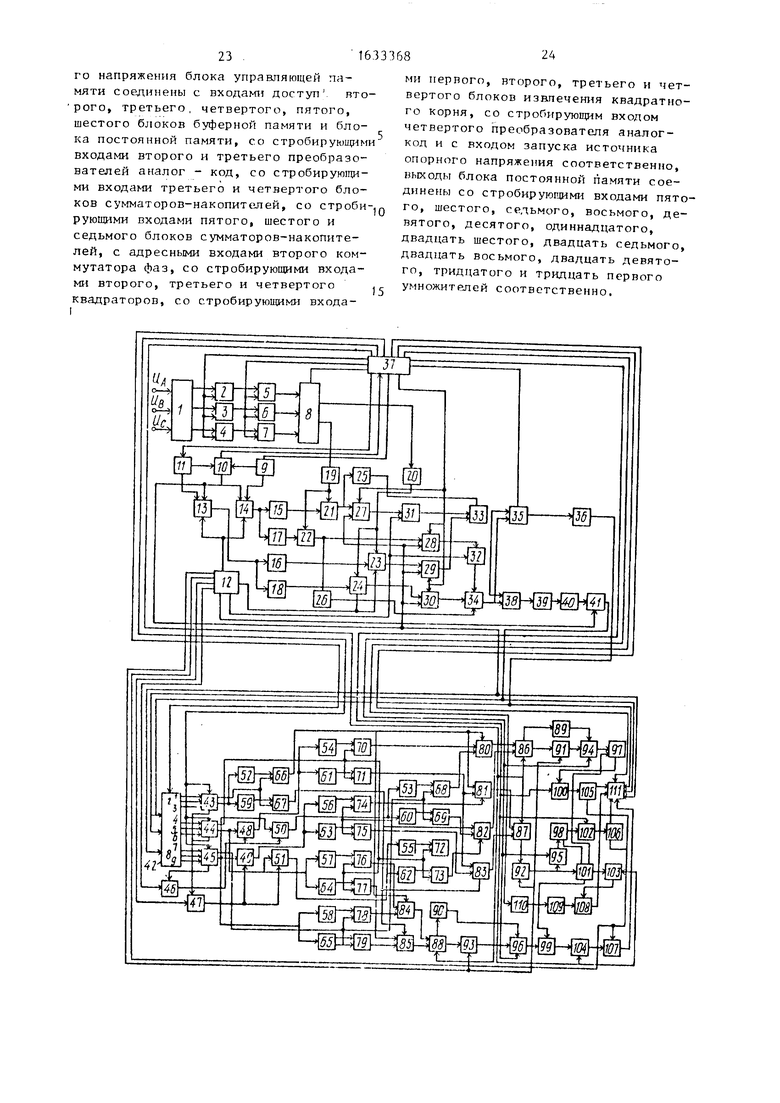

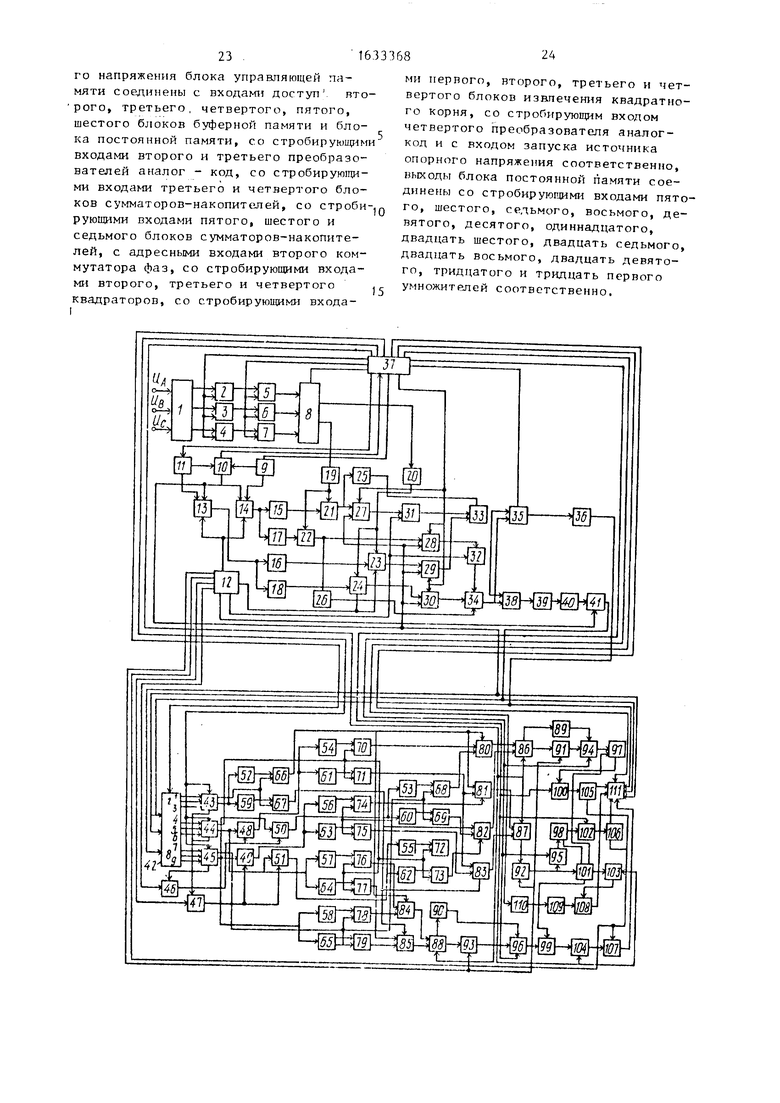

На чертеже изображена структурная схема предлагаемого измерителя.

Цифровой измеритель показателей качества электрической энергии трехфазной сети содержит масштабный преобразователь 1, с пег БОГ о Пс- третий преобразователи 2-4 аналог-код, с первого по третий блоки 5-7 буферной памяти, первый коммутатор 8 фаз, с первого по третий счетчики q-11, блок 12 постоянной памяти, вторе и 13 и пор- вый 14 умножители, первый 15 и вго- рой 16 задатчики функции коси iyca, первый 17 и второй 18 задатчики функции синуса, четвертый 19 и пятый 20 счетчику, с третьего по шестой умножители 21оэсо со со

О5

оо

24, первый и второй дешифраторы 25 и 26 кодов, с первого по четвертый блоки 27-30 сумматоров-накопителей, седьмой 31 и восьмой 32 умножители, первый 33 и второй 34 сумматоры, первый квадратор 35, девятый умножитель 36, блок 37 управляющей памяти, первый делитель 38, датчик 39 функции арктангенса, дешифратор 40 знака третий сумматор 41, второй коммутатор 42 фаз, с четвертого по шестой блоки 43-45 памяти, десятый и одиннадцатый умножители 46 и 47, с четвертого по седьмой сумматоры 48-51, третьего по девятый задатчики 52-58 функции косинуса, с третьего по девятый задатчики 59-65 функции синуса с двенадцатого по двадцать пятый умножители 66-79, с восьмого по тринадцатый сумматоры 80-85, с второго по четвертый квадраторы 86-88, первый 89 и второй 90 фильтры постоянно составляющей, с двадцать шестого по двадцать восьмой умножители 91-93 с пятого по седьмой блоки 94-96 сумматоров-накопителей, с второго по четвертый делители 97-99, фильтр 100 первой гармоники, с первого по четвертый блоки 101-104 извлечения квадратного корня, с двадцать девятого по тридцать первой умножители 105 107, четырнадцатый сумматор 108, четвертый преобразователь 109 аналог-код, источник 110 опорного нэп-1 ряжения и блок 111 регистрации.

Исследуемое фазное напряжение можно представить в виде

N Utt)

umKsin (kwt + ), (1)

где U L) амплитуда и начальные

фазы составляющих спектра сети;

,N - номера гармоник. I

С помощью ПАК входное напряжение U(t) представляется в М равностоящих точках. Дискретное преобразование Фурье такого сигнала имеет вид /у и-{яПтк

00

т-о

U)e

(2)

или в тригонометрической форме с применением метода Симпсона

Н

(и

(о) Vlcos2 k) .sin2nk + 4

М/2.

wi o

(U(2m-.)cos

2ri(2m-1)k

m

-.

. 2n(2m-1)k, . V („ -jU(em.l)Sin)+ 2 |l(U(

т

4imk

ц cos jU, sin

т(2 ml

. Alimkri 1П ..)J

Ак - JBK .

(3)

Модуль и фаза спектральной плотности (3) Определяется следующим образом

+ в i

V rctgfj

(4) (5)

где St и

Фь модуль и фаза спектральной плотности соответственно.

Тогда амплитудное значение k-й гармоники определяется из выражения

Umk М 5И

(6)

с ю15

30

35

40

45

50

k

55

а начальная фаза k-й гармоники может быть представлена в виде

7

Таким образом, блоки 43-45 памяти заполняются значениями амплитуд, начальных фаз напряжений и номерами гармонического спектра для фаз А, В, С следующих зависимостей соответственно

UA,X +ifftk ; иб. uBAA.ksin(kwt );

ис.к UCMiK sin(k(0t +CfpK).

Известно, что любую несимметричную систему трех токов напряжений, мощностей и потоков одинаковой частоты можно однозначно представить в виде трех систем: прямой, обратной и нулевой последовательностей, которые определяются по методу симметричных составляющих (5), т.е.

ипрк (UAl + а1Чк + а2исл);

1j

иобр, к .к + а ив.к + аисл )J

.к

+ и

В. К

ис,

При этом следует различать следующие режимы.

Напряжения фаз равны 11д. U & Uc

UAB UBc

исЛ. Четные гармоники в данном режиме отсутствуют. Первая, 7-я, 13-я, 19-я и так далее гармоники во всех фазах сдвинуты так же, как составляющие прямой последовательности. Пятая, 11-я, 17-я, 23-я и так далее гармоники образуют систему обратной последовательности. Все высшие гармоники, кратные трем, имеют во всех фазах данного режима в любой момент тождественные значения как составляющие нулевой последовательности. Данному режиму соответствуют фазные соотношения векторов внешних гармоник трехфазного генератора, мгновенные зн чения ЭДС k-й гармоники для каждой фазы которого можно представить следующим образом:

A,k

Е

/И.К

sin kcot;

EMksin k(Git-120 ); Едд.к. sin k(COt 240° )

г2.f.nAkH I

4UAKsin(bK + UBKsin(eK+ - + (K+

Амплитудное значение напряжения обратной последовательности для данU

otp к

1

ЗЛ

t4kii2k 1г

UAKCOS(AK + UBkcos(lfeit+ г-) + UCKcos(q C( + -Г)

Л,О-7VTT 1

UAK sinljft|(+ Uetsin((fek+ -5-) + UCksin( -51)J .

Соответственно, для напряжения нулевой последовательности имеем

%.k Л| (и4ксоз к+иВксо бк+искс°Чк)2+ u/usin4 +

(10)

Следовательно, действующие зжтче- ния напряжений обратной и нулевом последовательности имеют вид соответственно

Ml) (12)

Напряжения фаз не равны либо по модулю, либо по фазе, в данном режиме достаточно отличия хотя бы одного

Up UC

5

0

5

напряжения, Например, U У или Uftft Ufto / UCA. В таком режиме работают практически все системы электроснабжения и энергосистемы. При этом режиме могут присутствовать как четные, так и нечетные гармоники, Каждая гармоника в данном режиме содержит прямую, обратную и нулевую составляющие, причем независимо от того, имеется ли данная гармоника во всех трех фазах или только в двух или в одной фазе.

Согласно принципу наложения мгновенный ток любой ветви схемы равен сумме мгновенных токов отдельных гармоник. Аналогично мгновенное значение напряжения на любом участке схемы равно сумме мгновенных значений напряжений отдельных гармоник на этом участке. Расчет производится для каждой

из гармоник в отдельности с помощью

следующих примеров.

Амплитудное значение напряжения прямой последовательности k-й гармоники определяется по выражению

30

ной гармоники вычисляется по формуле

(9)

45

5

Таким образом, определив действующие значения напряжений обратной и нулевой последовательностей, можно найти следующие значения ПКЭ:

коэстфициент обратной последовательности, который определяется как отношение действующего значения напряжений обратной последовательности к действующему значению напряжения основной частоты прямой последователькоэффициент нулевой последовательности как отношение действующего значения напряжения нулевой последова- тельности к действующему значению напряжения основной частоты прямой последовательности (%)

еи - юо

И

U,

тГ + «Ј- UoHyfl +

Шпр

;(14)

коэффициент искажения кривых несимметричных напряжений трехфазной сети, который определяется отношением действующего значения высших гармоник напряжения UnpKK действующему значению напряжения основной частоты

прямой последовательности

(%)

кнс юо

N „ «г илрк

S - --

. L

ЦЛСР

(15)

отклонение напряжений в трехфазной сети определяется по формуле

U4np UHOM

кВ.

(16)

Измеритель работает в три этапа .

Первый этап. Фазные напряжения Uft(t), UB(t), Uc(t) сети через мае- штабный преобразователь 1 одновременно поступают на преобразователи 2-4 аналог - код соответственно. В пре- образователях 2-4 аналог - код происходит преобразование этих аналоге- вых величин в цифровые коды, которые затем записываются в блоки памяти 5-7 соответственно. Работой преобра зователей 2-4 и блоков 5-7 памяти управляет блок 37 управляющей памяти.

Второй этап. После заполнения блоков 5-7 памяти данными измеритель переходит в режим обработки. Тактовые импульсы из блока 37 поступают на счетчик 9 текущей выборки четного номера т-х импульсов и на счетчик 11 текущей выборки нечетного номера т-х импульсов выходы которых соединены с входом блока 37 через счетчик 10 номера R-й гармоники (3). Счетчик 10 переходит в следующее состояние по сигналу переноса счетчиков

Q

5

0

5

30

35

40 45

50

55

9 и 11, т.е. после окончания вычислений текущей гармоники . Выходные ко- ды счетчиков 9 и 10, начиная с нулевых значений, поступают на умножитель 14, куда заведен выход блока 12 числа 2/М, а выходные коды счетчиков 10 и 11, начиная с первых значений - на умножитель 13, куда заведен выход ПЗУ также числа 2/М, и на выходах умножителей 13 и 14 формируются значения текугдех аргументов функции косинуса и синуса, равные

2fi(2ro -1)k 4шк

i- и соответственно

ММ

(3).

Сигнал с выхода умножителя 13 поступает на входы задатчика 16 функции косинуса и задатчика 18 функции. синуса, на выходе которых образуют

2ff(2m - 1)k величины cos и

. 2fr(2m - 1)k

sin-, которые поступают

М

на умножители 23 и 24 соответственно. Сигнал с выхода умножителя 14 аналогичным образом поступает на выходы задатчика 15 функции косинуса и задатчика 17 функции синуса, на 1 выходе которых образуются величины

4Vmk. 4 nmk

cos --- и sin ---, которые затем ММ

поступают на умножители 21 и 22 соответственно. На другие входы умножителей 21 и 22 прикладывается текущее значение выборки четного номера т-х кодов ординат, поступающих из блоков 5-7 памяти через коммутатор 8 фаз, который под воздействием блока 37 поочередно подключает их к входу счетчика 19 текущей выборки четного номера га-х кодов ординат, причем выход счетчика 19 соединен с входами умножителей 21 и 22. Аналогичным образом на другие входы умножителей 23 и 24 прикладывается текущее значение вы- борки нечетного номера т-х кодов ординат через счетчик 20. Так как здесь же в умножителях 23 и 24 происходит

умножение значений U,rt .cos ------(iHl-l)М.

. 2n(2m - 1)k

и U,4m sinсоответственно на коэффициент 4, поступающий из блока 12, то на их выходах формируют2(2m-1)k . и

ся значения 4U,

iCOS

J(2m-.)c .... 2(2п, -1)k

(2b-i| м которые затем

поступают на сумматор-накопитель 29

и и сумматор-накопитель 30 соответственно На выходах умножителей 21

т „ ,,,4II mk

и II формируются значения 1,„ .сов---

( го)М

4 link

1Г,Я ,sin

2m)м

соответственно, причем с выходов умножителей 21 и 22 значения, соответствуют крайним ординатам, поступают на дешифраторы 25 и 26 кодов двух крайних рдинат, а остальные - на сумматопы-нпкопите ли 27 и 28 соответственно.

В блоках сумматоров-накопителей 27 и 28 формируются коды суммы VI2-.,..,«К-V k

чг-„

Ь, . cos --- и 21 U ,„ .sin ---, - (m)М (ямМ

которые затем поступают на умножители 31 и 32, куда заведен mix од Слона 12 числа 2 и Нс выход - умножителей 31 и 32 формируются значения

4 mk cos ---

«IМ

mlz

VU2-1

2Z1

m

На выходах дешифраторе

дон двух крайних значении формируются значения (1(0 и Ujjgisin / iik соответствен (, выходов дешиЛрл р.1

Х -Ы

m i .

cos

4ч mk

м- и

К cos

соответ i r

крайних значении ординат, 31 и блока сумматора-, IK чения (Ufo1 - l (M) cos ) М 2 iЛл-,.

2(2m-)k

M

пают на сумматор 33, с п рзтора 26 кг.дов двух ьр. ,тцй орлинат, умножит.M 30 сумматора-накопителя

#|2L ,u. sin 2tk; 2 T U, lM)

2(2, 1 )r

vU2

4 U ,ып I2m-0M

венно - на сутматор 34.

Таким образом, Р и 34 после зачерпения njn счетчикол 9 и 11 ния действительной и -чмс вы)ажения (3 г . г. . : сумматорс в 33 и 34 пг п-П дам квадратора 35, чен для возведения

котирr KB

ргвания и изнлечрчи нч из суммы крч/фа г тора 35, на t тор г.

ЧР..ИС

ЧК«

coe,iii i-j.j

0

0

теля 36. Здесь происходит умножение абсолютного значения S на коэффициент, который поступает из блока 12. Выходная величина умножителя 36 является амплитудным значением k-й гармоники и поступает на блок 11I регистрации. Для определения начальной фазы k-й гармоники выходные сигналы сумматоров 33 и 34 поступают на делитель 38, где происходит вычисление

fr величины г, которая поступает на задатчик 39 функции арктангенса, выходной сигнал которого прикладывается к дешифратору 40 знака.

В зависимости от определенного знака фазы спектральной плотности в сумматоре 41 происходит или сложе-ние величины

V

л. II

величиной г

пос.л.

4nmk 1-Г

Г1

о25

т

.

t ч ч на 30

35

-цф с

40

тст45

3

ты Ч О Oli4,l PXOл-а-ми

50

i /г -

5

тупающей из блока 12, или вычитание в соответствии с формулой (7). Выходная информация сумматора 41 представляет собой фазу k-й гармоники и поступает на блок 111 регистрации.

Выходные информации счетчика 10, множитепя 36 и сумматора 4 также писг,,з игск в блоках 43-45 памяти через коммутатор 42 фаз, :ij-ticr. паботы

ЬО.Ор jl С СИИХрОННО С ЦИКЛОМ рйьОТЫ

HOMN1, . i op.i 8 ф,1 з осуществляется , юком 3/ 10 номера гармоники iibirui t на б.|м к 111 регистрации номер анализируемо 1 гармонию и на .t : pni c i no гпряр ения сигнал об окончании анализа данной реализации С1:гнлла, чапиеаннпй в каждом из бло- коп -7 , и таюке сбрасывает в нулепе - состояние выходной код сумм торов-накопчтапгй 27-30 после анализа очередной гармоники. После этого устройство управления переходит к следующему этапу.

Трет и,i этап. После заполнения блоков 43-45 памяти данными измепи- ечь заново переходит ь режим обра- Сотки Гигнал с выхода блока 43 па- мя i и поступает п- входы задатчика 52 фуькщм косинуса и задатчика 59 функ- uui гиьус i, на выходе которых обра)УЮТГЯ НГЛПЧИНЫ co( )

i-гторне затем поступают на умножитель 66 и 6/ соответстиенно, На другие г.п,,„ умножшелей 66 и 67 приюта-г дыпае с екушее значение амп- яит , k-ii гармоники флзп Л, поступа- H)L e(i и 1рка 43 памяти, а на вы

ходах умножителей 66 и 67 формируются значения U cosCf H UA/WI ksinfpfl причем с выхода умножителя 66 значение UA ,yx cos Lfa K поступает на суммато- ры 80, 81 и 84, ас выхода умножителя 67 значение UAM()( sin(pflK - на сумматоры 82, 83 и 85.

Сигнал с выхода блока 44 памяти поступает на вход сумматора 48, на

2fk

другой вход которого поступает --

J

из умножителя 46, куда заведен вы2ffход блока 12 числа - , и значение

К, поступающее из блоков 43-45 памяти. На выходе сумматора 48 образует, ,.2fTk..

ся значение (If Bt/+ которое

затем поступает на входы задатчика 54 функции косинуса и задатчика 61 функции синуса, на выходе которых

2ftk формируются величины cos(Cfe.+ )

,.2/ii k ч

и sin (.( + --- )t которые затем

поступают на умножители 70 и 71 соответственно.

На другие входы умножителей 70 и 71 прикладывается текущее ние UBM кодов амплитуды к-й гармоники фазы В, поступающее из блока 44 памяти, и на выходах умножителей

70 и 71 образуются значения

2fik

cos((|Bk+ ---) и U

ем,к

in(q

sin

+ 2Јh)

en з ;

40

причем с выхода умножителя 70 значе2u kние U K cos(( + -о-) поступает на

сумматор 81, ас выхода умножителя 71

f2/iik4

значение U0(V,iK sin(qi + на сумматор 83. Сигнал с выхода блока 44 памяти также поступает на вход сумматора 51, на другой вход которого

4ftk

поступает значение -г- из умножителя 47, где производится умножение ко4ftэффициента г- на величину k, поступа- 50

ющую из блоков 43-45 памяти. На выходе сумматора 51 формируется значеi „ k, ние (.1Р.+ -z) которое затем посту™ DKJ

чение --- из умножителя 47. На выхо де сумматора 49 формируется -яначение

, . ,

СЦ. ---) , которое затем поступает

на входы задатчиков функции косинуса 56 и функции синуса 63, на выходе к

45 торых образуются значения cos(lfCK +

.. ,,

+ о) и Бш(Ц ск + которые за тем поступают на умножители 74 и 75 соответственно. На другие входы умно жителей 74 и 75 прикладывается текущее значение кодов амплитуды k-й гармоники фазы С, поступающее из бл ка 45 памяти, и на выходах умножителей 74 и 75 получаются значения Afkv

,55 UCM к cos( -г-) и U.w k sin(( +

пает на входы задатчиков функции ко-лтм,

синуса 55 и функции синуса 62, на

4nk,

+ ) причем с выхода умножителя

4nk..

выходе которых образуются cos(tPBR+ --- ) 74 значение UOM cosCCf + т пос10

15

)k 5

20

25

4 и sih((fB)(+ -г-), которые затем посту-г

пают на умножители 72 и 73 соответственно. На другие входы умножителей 72 и 73 прикладывается значение U... ,, из

ВМ, К

блока 44 памяти, а на выходах умножителей 72 и 73 образуются значения / 1

u&M,cos(cUk + и U6M,sin(LbK +

4lfk + -т-), причем с выхода умножителя 72

значение Ug cos(Cfg|c+ Ч поступает на сумматор 80, а с выхода умножителя 73 значение l)- sin( -тг-) на сумматор 82„ Сигнал с выхода блока 44 памяти также поступает на входы задатчика 57 функции косинуса и задатчика 64 функции синуса, на выходе которых получаются значения созсрвк и sinlpgK, которые затем поступают на умножители 76 и 77 соответственно.

На другие входы умножителей 76 и 77 прикладывается значение U из

ем,к

30

40

1

блока 44 памяти, а на выходах умножителей 76 и 77 формируются значения

ие,к cos М вк и UBM,ksinM)B. ПР этом с вьгхода умножителя 76 значение

вм ксозЦ ъ поступает на сумматор 84, с выхода умножителя 77 значение

вм на суммат0 5.

Сигнал с выхода блока 45 памяти 35 поступает на вход сумматора 49, на другой вход которого поступает знаA k

чение --- из умножителя 47. На выходе сумматора 49 формируется -яначение

, . ,

СЦ. ---) , которое затем поступает

на входы задатчиков функции косинуса 56 и функции синуса 63, на выходе которых образуются значения cos(lfCK +

.. ,,

+ о) и Бш(Ц ск + которые затем поступают на умножители 74 и 75 соответственно. На другие входы умножителей 74 и 75 прикладывается текущее значение кодов амплитуды k-й гармоники фазы С, поступающее из блока 45 памяти, и на выходах умножителей 74 и 75 получаются значения Afkv

UCM к cos( -г-) и U.w k sin(( +

55 UCM к cos( -г-) и U.w k sin(( +

о-лтм,

4nk,

+ ) причем с выхода умножителя

4nk..

--- ) 74 значение UOM cosCCf + т пос

ok

131

тупает на сумматор 81, а с выхода умножителя 75 значение Uru „sin(

4ftk, К

+ на сумматор 83.

Сигнал с выхода блока 45 памяти поступает на вход сумматора 50, на другой вход которого поступает зна2fic

чение --- из умножителя 46. На выходе сумматора 50 образуется значени

f, .

т ОН 1 которое затем поступает

на входы эадатчиков функции косинуса

Uoe ., соединен с умножителем 91.

53 и функции синуса 60, на выходе ко-15 Здесь проводится умножение абсолютcos (lf(

ск

торых получаются значения

2lTk4. ,,.

+ ---) и sin (If fK+ ---), которые

поступают на умножители 68 и 69 соответственно. На другие входы умножителей 68 и 69 прикладывается значение UcW из блока 45 памяти, а на выходах умножителей 68 и 69 формируются значения

исм,к51п(сЬк + да

UCM.KCOs((f Ok

3 ;

27k.

68

на

умножителя

2Јk, + -т-) поступает

с выхода умножителя 2 111 ч

з

причем с выхо- значение U,,.. ..cos ((.p

С/ИЛ сумматор 80,

69 значение - на

f

Ь СМ)|С sin(lf ск + ---) - на сум ггор

Сигнал с вьгхода блока 45 памя и прикладывается на входы задатми ков функции косинуса 58 и функции синуса 65, на выходе которых фгпмирумт- ся значения cos Lpc)l и sinc Ck (кот о- рые затем поступают на умножит, и 78 и 79, на другие входы которых прикладывается значение ис(И k из блока 45 памяти. На выходах умножителе 78 и 79 образуются значения UCM ,,cosipf и UfM K sin(fK, причем с ntc ода умножителя 78 значение l cw к со1 CfCK посту пает на сумматор 84, а с выхода умножителя 79 значение UCMi к s in Ц С1(- на с умма т ор 85.

Таким образом, на выходе с умнатора 80 получается значение деистнит1л ной составляющей k-й гармоники напряжения обратной послеловл ГЕ-чьногти, а на выходе сумматора S2 - тн чение ее мнимой составляющей (9). На выход сумматора 81 формируется значение действительной части k-и гармоники напряжения прямой последовательности а на сумматоре 83 - значение- ее мнимой части (8,). Аналогично на вкходе

14

10

сумматора 84 образуется действительная часть k-й гармоники напряжения нулевой последовательности, а на выходе сумматора 85 - значение ее мнимой части (10).

Выходы сумматоров 80 и 8 подкпюче ны к входу квадратора 86, который предназначен для возведения в квадрат и суммирования квадратов. Выход квадратора 36, где формируется значение квадрата амплитуды k-й гармоники напряжения обратной последовательности

Uoe ., соединен с умножителем 91.

15 Здесь проводится умножение абсолют

20

25

30

35

40

45

-

ного значения U., кна коэффициент 1/2, который поступает из блока 12.

На выходе умножителя 91 получается квадрат действующего значения U0sp м, которое поступает на вход блока 94 сумматора-накопителя, на другой вход которого поступает значение U0 оериз фильтра 89 постоянной состаапяющей напряжения обратной последовательности, вход которого соединен с другим выходом квадратора 86. В блоке 94 сумматора-накопителя фор-1- мируются коды суммы (11).

Выходы с умматорор 3 1 и 83 подключены к BXOAV квадратора 87, на выходе которого образуется зна цонме 1 прц- Выход квадратора 7 с i-елинеи с умножителем, куда заведен выход ПЗУ 12 числа 7. На виходе умноли- теля 92 формируется значение } первач гарконнка которого поступает на плод фичьтгк 1 ПО льщеленит первой гармонши, А пысшие гармоники - на ьход 6qi i а 95 гора-на онителя . Кл выходе рлгта 95 су матора-накопи- т образуются коды кшдратов

М , г - nЈ.k

И :

Выходные юды сумматоров Г4 и 85 подключены к входу квадратора 88. На выхоле квчдря.тора 88 получается значение UHu/i,i, 1 отгрое поступает на вход умножителя чЗ. Здесь производится умножение значения Ицул к на oэффициeнт 1/2, котории поступает- Из ПЗУ 12, С выхода умножителя 93

2

квадрат действующего значения L Hufli|c/2 поступает на вход блока 96 сумматора-накопителя, на другой вход которого поступает значение из кягдратора 88 через фильтр 90 постоянной составляющей напряжения нуле/ ой последовательности. На выходе блока 96 сумма-.

15

тора-накопителя формируются коды суммы (12).

Для определения коэффициента несимметрии напряжений выходные сигналы сумматора-накопителя 94 и фильтра 100 первой гармоники поступают на делитель 97, где производится вычисление подкоренного значения формулы (13), которое затем с выхода делителя 97 поступает на вход блока 101 извлечения квадратного корня, с выхода которого - на умножитель 105. Здесь производится умножение абсолютного значения Ји„ на коэффициент 100, который поступает из блока 12. С выхода умножителя 105 коэффициент симметрии поступает па блок регистрации.

Для определения коэффициента не- ypai-новошенности напрялешш ш тходные сигналы сумматора-накопителя 96 и фильтра 100 первой гармоники поступают на делитель 99, на выходе которого получается подкоренное значение формулы (14), которое затем поступает па блок 10 извлечения квадратного корпя, а на выходе блока 104 истечения квадратного корня формн- абсолютное - начение коэффициента неуравновешенности, которое поступает на вход умножителя 107 куда заведен выход блока 12 числа 100. Выходная величина множителя 107 является коэффициентом неуравно- в-зпенности Ји (%) и поступает на блок 11 регистрации.

Отклонение напряжения в трехфазной сети определяется путем пычитапи, на сумматоре 108 аналоговой опор-до - партии, что полностью отражает нанон стабильно г:о амплитуда величины in псточнмкл 110 опорного напряжения преобразуемой преобразователем 109 в цифровую из выходной величины фильтра 100 шиелгния первой гармоники, р,ьпшсляемой и блоке 103 извлечения гвлдратноге корня в соответствии с формулой (16). На выходе сумматора 108 получается значение отклонения напряжений, которое поступает на блок 111 регистрации.

Для вычисления коэффициента искажения кривых несимметричных напряжений выходные сигналы сумматора-накопителя 95 и фильтра 100 первой гармоники поступают на делитель 98, на выходе которого образуются коды отношения в соответствии с формулой (15). Код с выхода делителя 98 посту

3336816

паст на вход блока 102

10

15

20

25

30

35

извлечения квадратного корня, с выхода которого код поступает на вход умножителя 106, где производится умножение этого сигнала на коэффициент 100, поступающий из ПЗУ 12. С выхода умножителя 106 получается коэффициент несинусоидальности (%), который поступает на блок 111 регистрации. Блок 37 управляющей памяти синхронизирует работу всех узлов измерителя.

Положительным эффектом изобретения является то, что в отличие от известного измерителя, который не позволяет измерять симметричные составляюсье напряжений промышленной сети, и в отлитие от базовых объектов (измеритель пссимметрии цифровой 43204 и анализатор гармоник электрической сети цифровой 43250), первый из которых не позволяет достоверно оценивать несимметрию в нелинейных сетях, а второй - несинусоидальность несимметричных режимов, предлагаемый цифровой измеритель обеспечивает повышенную точность и расширение функциональных возможностей, так как он позволяет ичг-прлть, кроме несимметрии (коэф- (JniijieiiTOB обратной и нулевой последовательностей) , и несинусоидальность (коэффициент искажения кривых несимметричных напряжении), и отклонение напряжений в трехфазных электрических общего назначения как в линей- mrx, i и и нелинейных на основе псиного учета их взаимосвязи, а также совместного и одновременного их возденет пня на работу приемников электро

рушенш- функциональных свойств электрической энергии и реальные фи- зш еские. процессы в действующих сетях

Формула изобретения

Цифровой измеритель показателей качества электрической энергии трехфазной сети, содержащий масштабный преобразователь, входы которого являются информационными входами измерите

первый преобразователь ана

лог - код, первый блок буферной памяти, первый коммутатор фаз, первый и второй счетчики, блок регистрации с первого по четвертый умножители, пррпый задагчик функции синуса и первый задатчик функции косинуса, пер

171

вый и второй ьлоки сумматоров- накопителей, первый делитель, первый сумматор, первый квадратор, дешифратор знака, задатчик функции арктангенса, блок постоянной памяти, информационный выход которого подключен к счетному входу первого счетчика, первым кодовым выходом подключенного к счетному входу второго счетчика, первыми кодовыми выходами соединенного с адресным входом блока управляющей памяти, вторые кодовые выходы первого счетчика соединены с входами первого сомножителя первого умножителя, вход второго сомножителя, входы первых слагаемых первого и второго блоков сумматоров- накопителей и первый информационный вход блока регистрации соединены с вторым кодовым выходом второго счетчика, выход первого умножителя соединен с входами первого задатчика функции косинуса и первого задатчика функции синуса, выход.: которых соединены с иходами первых сомножителей второго и третьего умножителей соответственно, выходы которих соединены с входами вторых сомножителей первого и второго блоке; с умматорол накопителей соответственно, выход квадратора через четвертый умножител соединен с вторым входом регистратор к третьему входу котпрого подключен выход первого делителя череч та ы ш функции арктангенса, дешифратор эт- ка и первый сумматор, ацрс-сш-н. ы,- ходы, первый выход управления дгс-ту- пом к памяти, с первого по четвертый стробирующие выходы Глока управляющей памяти соединены сооткетп с адресными входами первого коммутатора фаз, входом чтение-запись первого блока буферной памяти, со стро- бирующими входами первого преобразователя аналог - код, с объединенными стробирующими входами первого, второго блоков сумматоров-нзкопитс1- лей, со стробирую чим входом nepnoj о квадратора и со стробирующим входом блока регистрации, выхолы блока постоянной памяти соединены г входом третьего сомножителя первого умножителя, с входом второго сомножителя четвертого умножителя и г входом второго слагаемого первого сумматора, первый выход масштабного преобразователя соединен с информант1 мним входом первого преобразователя ана

0

5

3368

18

лог - код, выход которого подключен к информационному входу первого блока буферной памяти, выходом подсое- диненного к первому информационному входу первого коммутатора фаз, о т - л и ч а ющи и с я тем, что, с целью повышения точности измерений и расширения области применения иэQ мерителя, в него введены с второго по четвертый преобразователи аналог- код, с второго по шестой блоки буферной памяти, с третьего по пятый счётчики, с пятого по тридцать первый

5 умножители, первый и второй дешифраторы кодов, с второго по четырнадцатый сумматоры, с третьего по седьмой блоки сумматоров-накопителей, второй коммутатор фаз, с второго по девятый задатчнки функции косинуса, с второго по девятый задатчикн функции синуса, с второго по четвертый квадраторы, первый и второй фильтры постоянной составляющей, с второго по четвертый делители, фильтр первой гармоники, с первого по четвертый блоки извлечения квадратного корня н источник опорного напряжения, второй п третий выходы масштабного npeofipaзолят тля соьдиненн с информационными входами ятороге п третьего преобразователей амало - ко; соответственно, выходы которых подключены к иПФОРМ.Лционш. м входам второго и третьего блоков буферной памяти, BF-КОДЫ которых соединены с соответ- ст рук чими ннформ.i цимиными входами i.tjpBoro коммутатора фаз, первый выход первого коммутатора фаз соединен со счйтГ Ым вход I M ч е-т ье.ртог о счетчн- ка m, г: од ключ (.иного к входам вторых сомножителей второго и третьего умножителей, а втором выход первого коммутатора фаз соединен со счетным входом пятого счетчика, выходами соединенного с входами первых сомножителей шестого и седьмого умножителей, синхровм/.оя блока управляющей памяти подключен к счетному входу третьего счетчика, в; код ом перемещения соединенного со счетным входом второго счетчика, вторые кодовые выходы которого соединены с входом первого сомножителя пятого умножителя, с входами первых сомножителей третьего и четвертого блоков сумматоров-накопителей, с первым информационным входом второго коммутатора фаз, кодовые выходы третьего счетчи0

5

0

5

0

5

ка соединены с входом второго сомножителя пятого умножителя, выход которого подключен к входам второго задат чика функции косинуса и второго за- датчика функции синуса, выходы которых соответственно подключены к входам вторых сомножителей шестого и седьмого умножителей, выходами соответственно соединенных с входами второго сомножителя третьего и четвертого блоков сумматоров-накопителей, выход третьего блока сумматоров-накопителей подключен к входу первого слагаемого второго сумматора, а выход четвертого блока сумматоров-накопителей - к входу первого слагаемого третьего сумматора, выход второго умножителя соединен через первый де - шифратор кодов с входом стробирова- ния второго сумматора, а выход третьего умножителя через второй дешифратор кодов - с входом стробирования третьего сумматора, выходы первого и второго блоков сумматоров-накопителей соответственно соединены с входами первых сомножителей восьмого и девятого умножителей, выходами соответственно подключенных к входам второго слагаемого второго и третьего сумматоров, выходы которых параллельно подключены к соответствующим входам первого делителя и входами операндов первого квадратора, выход четвертого умножителя соединен с вторым информационным входом второго коммутатора фаз, третий информационный вход которого соединен с выходом первого сумматора, первая труп па выходов второго коммутатора фаз соединена с входами данных четвертого блока буферной памяти, соединенного первым выходом с входами первых сомножителей двенадцатого и тринадцатого умножителей, входы вторых сомножителей которых соединены с выходами третьего задатчика функции косинуса и третьего задатчнка функции Јинуса, соответственно, входы третьего задатчика функции косинуса и третьего задатчика функции синуса подключены к второму выходу четвертого бло- ка буферной памяти, вторая и третья группы выходов второго коммутатора фаз подключены к входам данных пятого и шестого блоков буферной памяти, третьи выходы четвертого, пятого и шестого блоков буферной памяти соединены с входами первых сомножителей

5

0

5

0

5

0

5

0

5

десятого и одиннадцатого умножителей выход десятого умножителя соединен с входами первых слагаемых четвертого и шестого сумматоров, а выход одиннадцатого умножителя - с входами первых слагаемых пятого и седьмого сум-1 маторов, первый выход пятого блока буферной памяти подключен к входам первых сомножителей шестнадцатого и семнадцатого умножителей, входы вторых сомножителей которых подключены к выходам пятого задатчика функции синуса и пятого задатчика функции синуса соответственно, соединенных входами с выходом четвертого сумматора, входы вторых слагаемых четвертого и седь-ю- го сумматоров соединены с вторым выходом пятого блока буферной плгтти и с входами восьмого чадатчнка фун -- ции косинуса и восьмого задт функции синуса, выход спдьмгмо сумматора через шестой задлтчик функции косинуса и через шестой задлтчик функции синуса соединен с входам первых сомножителей восемнадцатого и девятнадцатого умножителей соответственно, входы вторых слагаем-к пятого и шестого сумматоров подключены к первому выходу шестого блпкл буферной памяти, второй виход которого соединен с входами первых сомножителей четырнадцатого, пятнадцатого, двадцатого, двадцать псрчого, двадцать четвертого и двадцать пятого умножителей, входы вторых сомможите- 1ей четырнадцатого и пятнадцатого умножителей соответственно подключены к выходам четвертого задатчикл функции косинуса и четвертого задатчика функции синуса, входами соединенных с выходом шестого сумматорл, входы вторых сомножителей двадцатого и двадцать первого умножителей соответственно подключены к выходам седьмого задатчика функции косинуса и седьмого задатчика функции синуса, входами соединенных с выходом пятого сумматора, входы вторых сомножителей двадцать четвертого и двадцать пятого умножителей соединены г выходами девятого задатчика функции косинуса и девятого задатчика функ- ции синуса соответственно, вхиды которых соединены с первым выходом шестого блока буферной памяти, входы первых сомножителей двадцать второго и двадцать третьего умножителей и входы вторых сомножителей восемнодцатого и девятнадцатого умножителей подключены к первому выходу пятого блока буферной памяти, а входы вторых сомножителей - с выходами восьмого задатчика функции косинуса и восьмого задатчика функции синуса соответственно, входы которых соединены с первым выходом пятого блока буферной памяти, входы первых слагаемых восьмого, девятого и двенадцатого сумматоров соединены с выходом двенадцатого умножителя, входы первых слагаемых десятого, одиннадцатого и тринадцатого сумматоров соединены с выходом тринадцатого умножителя, входы второго и третьего слагаемых восьмого сумматора соединены с выходами четырнадцатого и восемнадцатого умножителей соответственно, входы делителя и делимого второго делителя соответственно подключены к первому выходу фильтра первой гармоники и выходу пятого блока суммато- ров-накопителей, входом подключенно- хго к выходу двадцать шестого умножителя, входом первого сомножителя подключенного к выходу второго квадратора, входами операндов СООТРГ-ГО сменно соединенного с выходом восьмого сумматора и выходом десятого сумматора, входы второго и третьего слагаемых которого соответстпенно соединены с выходами пятнадцатого и девятнадцатого умножителей, выход второго делителя соединен с входом первого блока извлечения квадратного корня, выходом подключенного к входу двадцать девятого умножителя, выход которого подключен к четвертому нходу блока регистрации, выходы девятого и одиннадцатого сумматоров соединены с соответствующими входами операндов третьего квадратора, выходом соединенного с входом первого сомножителя двадцать седьмого умножителя, выход которого подключен к входу шестого блока сумматора-накопителя и входу данных фильтра первой гармоники, выходы которых подключены к входам делимого и делителя соответственно третьего делителя, входы второго и третьего слагаемых девятого сумматора соответственно соединены с выходами шестнадцатого и двадцатого умножителей, а входы второго и третьего слагаемых одиннадцатого сумматора - с выходами семнадцатого и двадцать первого умножителей соответственно, выход треть0

0

5

0

5

0

5

0

5

его делителя соединен с входом данных второго блока извлечения квадратного корня, выходом подключенного к входу первого сомножителя тридцатого умножителя, выход которого соединен с пятым входом блока регистрации, вход первого сомножителя четвертого делителя соединен с выходом седьмого блока сумматоров-накопителей, а вход второго сомножителя - с третьим выходом фильтра первой гармоники, четвертый выход которого подключен к первому входу третьего блока извлечения квадратного корня, подключенного выходом к входу первого слагаемого четырнадцатого сумматора, вход первого слагаемого седьмого блока сумматоров-накопителей подключен к выходу двадцать восьмого умножителя, входом первого сомножителя соединенного с первым в гходом четвертого квадратора, соединенного входами операндов с выходами двенадцатого и тринадцатого сумматоров соответственно, входы второго и третьего слагаемых двенадцатого сумматора соответственно соединены с выходами двадцать второго и двадцать четвертого умножителей, а входы второго и третьего слагаемых тринадцатого сукмат ра - с иыхидами двадцать третьего и гнад- цать пятого умножителей соответственно, входы вторых слагаемых пятого и седьмого блоков сумматоров-накопителей через первый и второй фильтры постоянней составляющей соединены с вторыми выходами второго и четвертого квадраторов соответственно, выход четвертого делителя соединен с входом четвертого блока извлечения квадратного корня, вькодом соединенного с входом первого сомножителя тридцать первого умножителя, выход которого соединен с шестым гходом блока регистрации, седьмой вход которого соединен с выходом четырнадцатого сумматора, входом второго слагаемого подключенного к выходу четвертого преобразователя аналог- - код, входом соединенного с выходом источника опорного напряжения, первый, второй и третий выходы доступа к памяти, первый стробирующий выход, второй стро- бирующий выхсх;, пятый строОирующий выход, второй адресный выход, шестой стробируюиий выход, седьмой стробиру- ювдш выход, восьмой стробирующий выход и выход запуска источника опоиного напряжения блока управляющей памяти соединены с входами доступ второго, третьего, четвертого, пятого, шестого блоков буферной памяти и блока постоянной памяти, со стробирующими входами второго и третьего преобразователей аналог - код, со стробирующими входами третьего и четвертого блоков сумматоров-накопителей, со строби- рующими входами пятого, шестого и седьмого блоков сумматоров-накопителей, с адресными входами второго коммутатора фаз, со стробирующими входами второго, третьего и четвертого квадраторов, со стробирующими входа

5

ми первого, второго, третьего и четвертого блоков извлечения квадратного корня, со стробирующим входом четвертого преобразователя аналог- код и с входом запуска источника опорного напряжения соответственно, выходы блока постоянной памяти соединены со стробирующими входами пятого, шестого, седьмого, восьмого, девятого, десятого, одиннадцатого, двадцать шестого, двадцать седьмого, двадцать восьмого, двадцать девятого, тридцатого и тридцать первого умножителей соответственно.

Авторы

Даты

1991-03-07—Публикация

1988-06-15—Подача