1 ; - - .

Изобретение отнЬсит.ся к. радиоизмерительной технике,

Иэвестн.о Ц1 фровое устройство для оптимального изме рения частоты сигнала, содержащее последовательно соединенные полосовой фильтр и аналогоцифровой гфеобразователь, а также регистры, умножители, генераторы аргументов, тригонометрические преобразователи, генератор амплитуд, накопители, квадраторы, сумматоры, блоки извлечения квадратного корня, клчитатель, блок вычисления отношения, формирователь коэффициентов, управляющее и решающее устройство. В этом устройстве производится фильтрация закодированных сигналов двумя цифровыми фильтрами, детектирование и вычисление кодового значения рассогласования между истинным и измеренным значениями частоты и формирование кодового значения измеренной частоты сигнала 1.

Наиболее близким по технической сущности к предлагаемому устройству является цифровой панорамный измеритель частрты, в котором первые входы двух синхронных детекторов соединены с источником измеряемой частоты, их вторые входы подключены

к выходам квадратурного генератора, а выход каждого смесителя через последовательно соединенные фильтр нижних частот, дискретизатор и аналогоцифровой преобразователь соединен с соответствующим входом блока вычисления, дискретного преобразования Фурье, выход которого через квадратор соединен со входом блока грубой

0 оценки, выход блока грубой оценки частоты соединен со входом интерполятора, другой вход которого-соединен с соответствующим выходом квадратора, причем вторые входы д искретизатора, .

5 соединены с выходами задающего генератора сигналов дискретизации. В этом устройстве путем перебора отсчетов энергетического спектра сигнала, формируемых в устройстве, нахожде0ния максимальных значений.и последующей интерполяции формируется точная оценка частоты 12.

Недостатками данных устройств являются большое количество оборудования и низкое быстродействие.

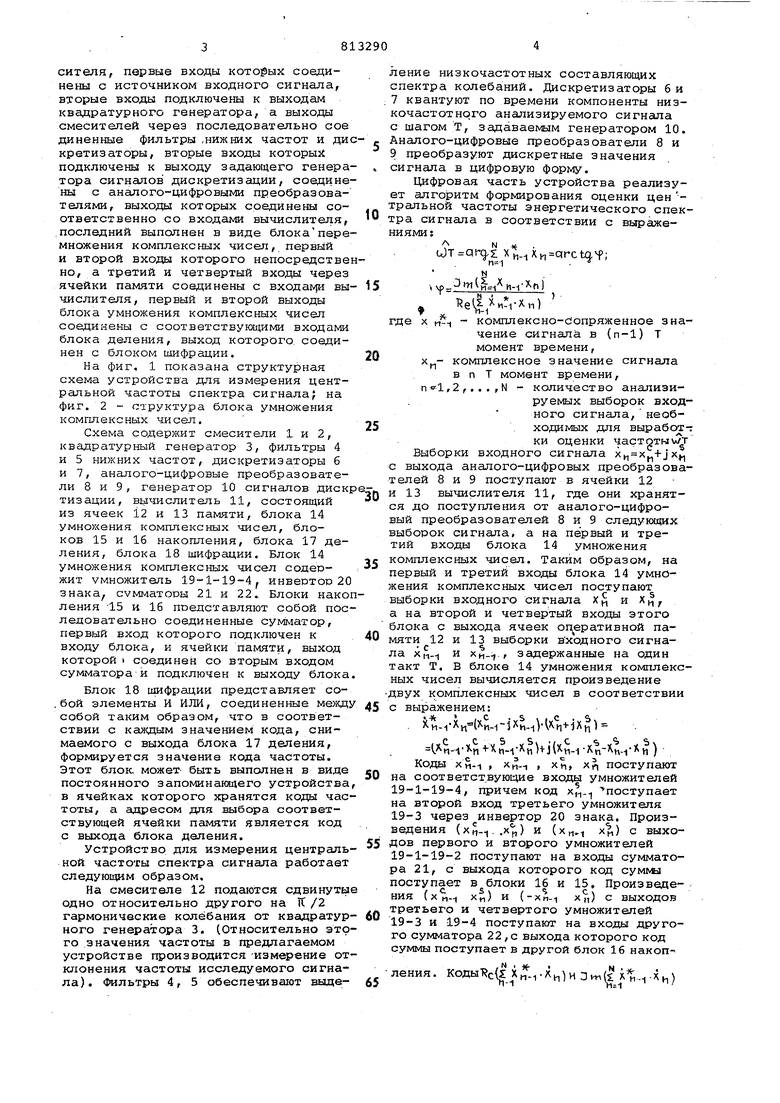

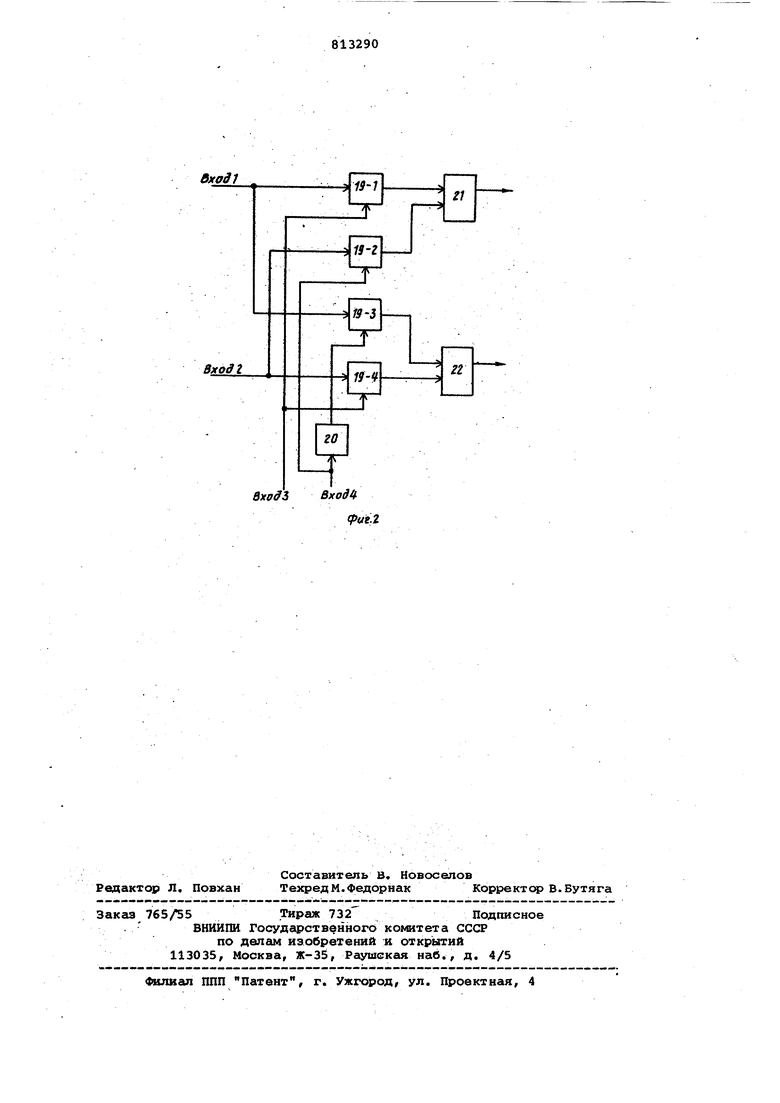

Цель изобретения - сокращение оборудования и повышение быстродействия. Поставленная цель достигается тем, 0 что в устройстве, содержащем два смесителя, первые входы которых соединены с источником входного сигнала, вторые входы подключены к выходам квадратурного генератора, а выходы смесителей через последовательно сое диненные фильтры ,нижних частот и дис крет и заторы, вторые входы которыз4 подключены к выходу задающего генератора сигналов дискретизации, соединены с аналого-цифровыми преобразователями, выходы которых соединены соответственно со входами вычислителя, .последний выполнен в виде блокаперемножения комплексных чисел, первый и второй входы которого непосредстве но, а третий и четвертый входы через ячейки памяти соединены с входаг вычислителя, первый и второй выходы блока умножения комплексных чисел соединены с соответствующими входами блока деления, выход которого, соединен с блоком шифрации. На фиг. 1 показана структурная схема устройства для измерения центральной частоты спектра сигнала; на фиг. 2 - структура блока умножения комплексных чисел. Схема содержит смесители 1 и 2, квадратурный генератор 3, фильтры 4 и 5 нижних частот, дискретизаторы 6 и 7, аналого-цифровые преобразователи 8 и 9 , генератор 10 сигналов дискр тизации, вычислитель 11, состоящий из ячеек 12 и 13 памяти, блока 14 умножения комплексных чисел, блоков 15 и 16 накопления, блока 17 деления, блока 18 шифрации. Блок 14 умножения комплексных чисел содеожит умножитель 19-1-19-4 инвестор 20 знака, сумматооы 21 и 22.. Блоки нако ления 15 и 16 представляют собой пос ледовательно соединенные сумматор, первый вход которого подключен к входу блока, и ячейки памяти, выход которой I соединен со вторым входом сумматора и подключен к выходу блока Блок 18 шифрации представляет со.бой элементы И ИЛИ, соединенные межд собой таким образом, что в соответствии с каждым значением кода, снимаемого с выхода блока 17 деления, формируется значение кода частоты. Этот блок может быть выполнен в виде постоянного запоминанадего устройства в ячейках которого хранятся коды час тоты, а адресом для выбора соответствующей ячейки памяти является код с выхода блока деления. Устройство для измерения централь ной частоты спектра сигнала работает следующим образом. На смесителе 12 подаются сдвинуты одно относительно другого на ТС /2 гармонические колебания от квадратур кого генератора 3. (Относительно это го значения частоты в предлагаемом устройстве производится -изм уение от клонения частоты исследуемого сигнала). Фильтры 4, 5 обеспечивают выделение низкочастотных составляющих спектра колебаний. Дискретизаторы 6 и 7 квантуют по времени компоненты низкочастотного анализируемого сигнала с шагом Т, задаваемым генератором 10. Аналого-цифровые преобразователи 8 и 9 преобразуют дискретные значения сигнала в цифровую форму. Цифровая часть устройства реализует алгоритм формирования оценки цен тральной частоты энергетического спектра сигнала в соответствии с выражениями : u)T а rg, X . X q г с М; N V 1 1 е1| 1 иГ1-Хп) где X , - комплексно-Сопряженное значение сигнала в (п-1) Т момент времени, комплексное значение сигнала в п Т момент времени, nsl,2,...,N - количество анализируемых выборок входного сигнала, необxoдиIv ыx для выработки оценки 4acTQTHWT Выборки входного сигнала X( с выхода аналого-цифровых преобразователей 8 и 9 поступают в ячейки 12 и 13 вычислителя 11, где они хранятся до поступления от аналого-цифровый преобразователей 8 и 9 следующих выборок сигнала, а на первый и третий входы блока 14 умножения комплексных чисел. Таким образом, на первый и третий входы блока 14 умножения комплексных чисел поступают выборки входного сигнала х и Х|, а на второй и четвертый входы этого блока с выхода ячеек оп еративной памяти 12 и 13 выборки входного сигнала XM- и х., задержанные на один такт Т. В блоке 14 умножения комплексных чисел вычисляется произведение двух комплексных чисел в соответствии с выражением: . J- -i- H «-i-iXh-i)-UVi)h M-i iiHj(XM-i)n h-i h ) Коды хм-1 Хи-1 , , поступают на соответствующие входы умножителей 19-1-19-4, причем код поступаат на второй вход третьего умножителя 19-3 через инвертор 20 знака. Произведения (..xj) и ( х,) с выходов первого и второго умножителей 19-1-19-2 поступают на входы сумматора 21, с выхода которого код суммы поступает в блоки 16 и 15, Произведения (X и--, х„) и (-хп-1 хп) с выходов третьего и четвертого умножителей 19-3 И 19-4 поступают на входы другого сумматора 22,с выхода которого код суммы поступает в другой блок 16 накопления. КодыТ с(| X и) и J пл (1 х .. ) н,) с выходов блоков 15 и 16 накопления поступают в блок 17 деления, в кото ром производится деление кодаЗт( хи)г на код Re(f xn-i х и). Полученный в результате деления код Н с выхода блока 17 деления поступает в блок 18 шифрации, в котором по этому коду формируется значение оценки частоты tg . Полученна оценка является оценкой максимального правдоподобия частоты узкополосного комплексного случайного процесса, В известном устройстве объем операций для вычисления одной оценки ,частоты по N отсчетам энергетического спектра сигнала (на выходах N циф ровых фильтров N-ой кратности) в N раз больше, чем в предлагаемом, поскольку в последнем реализован один коррелятор. Следоватальйо, быстродей ствие предлагаемого изобретения в N раз выше, чем известного. Объем аппаратуры в известном цифровом панорамном измерителе примерно в 1,5 раза больше, чем в предлагаемом изобретении из-за большой памяти в блоке вычисления дискретного пре.образования Фурье и из-за сложного и терполятора , при примерно одинаковом объеме всех остальных узлов. Формула изобретения Устройство для измерения централи ной частоты спектра сигнала, содержа щее два смесителя, первые входы которых соединены с источником входного сигнала, их вторые входы подключены к выходам квадратурного генератора, а выходы смесителей через последовательно соединенные фильтры нижних частот и дискретизаторы, вторые входы которых подключены к выходу генератора сигналов дискретизации, соединены с аналого-цифровыми преобразователями, выходы которых соединены соответственно со входами вычислителя, отличающееся тем, что, с целью сокращения оборудования и повышения быстродействия, вычислитель выполнен в виде блока переключения комплексных чисел, первый и второй входы которого непосредственно, а третий и четвертый входы через ячейки памяти соединены со входами вычислителя, первый и второй входа блока умножения комплексных чисел через блоки накопления соединены с соответствующими входами блока деления, выход которого соединен с блоком шифрации. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 478261, кл. G 01 R 23/00. 2.Авторское свидетельство СССР № 569961, кл. G 01 R 23/00.

Вход4

.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для цифровой обработки сигналов | 1977 |

|

SU746537A1 |

| Устройство для цифровой фильтрации на основе дискретного преобразования Фурье | 1990 |

|

SU1795475A1 |

| Цифровой панорамный измеритель частоты | 1985 |

|

SU1296955A1 |

| Устройство для цифровой фильтрации на основе дискретного преобразования Фурье | 1988 |

|

SU1640710A1 |

| Устройство для выделения признаков при распознавании случайных сигналов | 1990 |

|

SU1797134A1 |

| Цифровой панорамный измеритель частоты | 1979 |

|

SU838601A1 |

| Устройство для цифровой фильтрацииНА OCHOBE диСКРЕТНОгО пРЕОбРАзОВА-Ния фуРьЕ | 1979 |

|

SU840922A1 |

| Устройство для измерения центральной частоты спектра узкополосного сигнала | 1990 |

|

SU1795378A1 |

| СПОСОБ ПЕЛЕНГАЦИИ РАДИОСИГНАЛОВ И ПЕЛЕНГАТОР ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2008 |

|

RU2383897C1 |

| Цифровой фазометр | 1980 |

|

SU883790A1 |

Авторы

Даты

1981-03-15—Публикация

1979-03-19—Подача