(54) КОММУТИРУЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Ячейка коммутирующей среды | 1971 |

|

SU441565A1 |

| Ячейка волновой коммутационной системы | 1985 |

|

SU1256011A2 |

| Коммутирующая сеть | 1986 |

|

SU1411766A1 |

| Устройство для сопряжения вычислительной машины с магистралью обмена | 1986 |

|

SU1381519A1 |

| Ячейка волновой коммутационной системы | 1980 |

|

SU934467A1 |

| Ячейка каскадной коммутирующей среды | 1977 |

|

SU712822A1 |

| ТРЕХКАСКАДНАЯ КОММУТАЦИОННАЯ СИСТЕМА | 2007 |

|

RU2359313C2 |

| Асооциативная однородная среда | 1978 |

|

SU798803A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| В П Т Б ЧП r^f'n'^f'nTrii т bnOiiiiPiyi | 1973 |

|

SU408303A1 |

1

Изобретение ..относится к вычислительной технике и может быть использовано при построении вычислительных структур.

Известны коммутирующие устройства, содержащие решетчатое коммутирующее поле, выполненное из ячеек, входы и выходы которых соединены с соответствующими выходами и входами смежных ячеек, управл5пощий блок с выходами установки в исходное состояние, сброса в нуль входов, автоконтроля, записи прадерева каналов и восстановления проводимости «гаеек, соединенными с соответствующими щинами всех ячеек, и запоминающий блок с входами и выходами, соединенными с управляющим блоком и входами периферийных ячеек коммутирующего поля.

Однако известное устройство характеризуется блокируемостью каналов связи и недостаточной надежностью.

Делью изобретения является повыщение надежности и коммутационных возможностей устройства.

Для этого в узлах коммутирующего поля введены макроячейки, обрвоованные

группами ячеек, в которых входы и выходы каждой ячейки соединены с соответствующими выходами и входами всех ячеек данной макроячейки и одной из ячеек смежной макроячейки, щина для записи прадерева каналов соединена с выходом элемента ИЛИ формирования сигнала записи, входы которой соединены с выходом первого элемента И блокировки и выходом

сигнала записи формирователя команд, соединенного также со счетным входом триггера, задающего шаг настройки, нулевой выход которого соединен с щинами для выделения вспомогательных макроячеек, выходные щины которых соединены через элемент ИЛИ с входом первого элемента И блокировки, другой вход которого соединен с нулевым выходом триггера, задающего щаг настройки, который соединен также с входами элементов И для считывания адресов макроячеек источников и приемников, другие входы которых соединены соответственно с выходами сигналов признаков источника и приемника формирователя команд, а выходы с входами запоминающего блока, единичный выход триггера, задающего шаг настройки, соединен с, входом элемента И признака распределенного источника, второй вход которого соединен с выходом сигнала признака источника формирователя команд, а выход - с соответствующей шиной макроячеек коммутирующего поля и через инвертор с входами выходных элементов И, другие входы которых соединены с единичными выходами триггеров регистра адресов макроячеек приемников и шиной для разрешения настройки, соединенной также с входом второго элемента И блокировки, второй вход которого соединен с шиной тактовых импульсов, а выход - с взсодом формирователя команд.

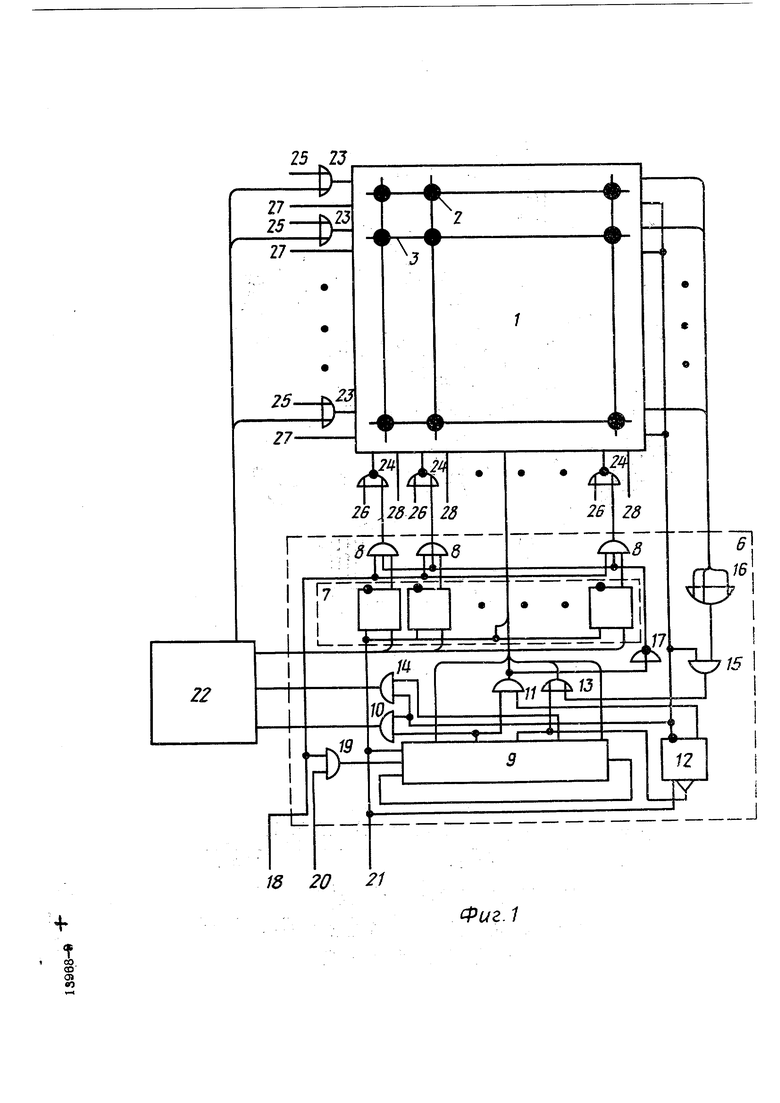

Изобретение пояснено чертежами.

На фиг. 1 приведена структурная электрическая схема; устройства; на фиг. 2 - схема макроячейки.

Коммутирующее устройство содержит коммутирующее поле 1, образованное макроячейками 2, соединенными звеньями внешней коммутации 3 в прямоугольную решетку.

Макроячейка 2 (см. фиг. 2) состоит из четырех ячеек 4, соединенных между собой звеньями внутренней .коммутации 5. В состав звеньев 3 и 5-входят входная и выходная шины потенциала поиска, шины ввода и вывода потенциала выделения, ввода и вывода состояний управляющих триггеров блоков ввода - вывода смежных ячеек..

Кроме того, устройство содержит управляющий, блок 6, в состав. которого входят регистр 7 адресов макроячеек приемников, выходы которого соединены с входами выходных элементов И 8, формирователь команд 9, в качестве которого используется циклический регистр, с выходами контролиру1О,щих сигналов, признака источника, записи прадерева каналов, признака приемника и восстановления проводимости ячеек, соединенными . соответственно с шиной для перевода входов в нулевое состояние и контроля ячeeK входами элементов К 10 для считывания адреса макроячеек - источников И 11 для формирования сигнала признака ра,спределенного источника, счетным входом триггера 12, задающего шаг настройки, и входами элемента ИЛИ 13, формирукь щего сигнал записи прадерева каналов, входом элемента И 14 для считывания

адресов макроячеек - приемников, шиной восстановлени:я проводимости ячеек.

Нулевой выход триггера 12, задающего шаг настройки, соединен с входами

элементов И 10 и 14 для считывания адресов коммутируемых макроячеек, входом первого элемента И 15 блокировки и шинами ввода потенциала выделения; вспомогательных вершин, в качестве которых используются периферийные макроячейкистороны коммутирующего поля, противоположной макроячейкам - источникам. Выходы потенциала поиска последних соединены с входами элемента ИЛИ 16, выход

которого соединен с входом первого элемента И 15 блокировки. Выход последнего соединен с входом элемента ИЛИ 13,: форн мирующего сигнал записи прадерева каналов, выход которого соединен с соответствующими шинами ячеек 4.

Выход элемента И 11 соединен с шиной задания распределенного признака источника ячеек 4 и через инвертор 17. с входами выходных элементов И 8, соединенными

также с шиной 18 разрешения настройки. Последняя соединена также с входами вто- рого элемента И 19 блокировки, другой вход которого соединен с шиной 20 тактовых импульсов. Выход элемента И 19 соединен с входом сдвига формирователя команд .9. Шина 21 для установки в исходное состояние соединена с нулевыми входами триггера 12, регистра -7, с формирователем команд 9 и шиной установки макроячеек

в исходное состояние.

Входы запоминающего блока 22 соединены с выходами элементов. И 10 и 14 для считывания адресов коммутируемых макроячеек..

Выходы адресов макроячеек - приемников и источников последнего соединены соответственно с единичными входами триггеров регистра 7 и входами элёментов ИЛИ 23, выходы которцх соединены с входами потенциала поиска макроячеек - источников, в качестве которых используются периферийные ячейки одной из сторон коммутирующего поля 1.

Выходы выходных элементов И 8 соединены с входами элементов, ИЛИ-НЕ 24, выходы которых соединены с щинами для ввода потенциала выделения .макроячеекприемников, в качестве которых используются периферийные ячейки стороны коммутирующего поля 1, прилежащей, к макроячейкам - источникам.

Выходы коммутируемых автоматов подключаются к шинам 25 и 26, соединенным с входами элементов. ИЛИ 23 и ИЛИНЕ 24. Входы коммутируемых автоматов подключаются к шинам 27 и 28, соединенным с шинами для вывода потенциала вьщеления макроячеек - источников и выходам потенциала поиска макроячеек приемников соответственно.

Коммутируюшее устройство работает следуюшим образом.

Установка устройства в исходное состояние осуществляется подачей.нулевого потенциала по шине- 21, по которой ячейки 4 коммутирующего поля 1 устанавливаются в проводящее состо5ш:ие,. пе эеводятся в нулевое состояние регистр 7, триггер 12, и в первый разр5Щ формирователя команд 9 заносится единица. Сигналом этого разряда переводятся в нулевое состояние, входы ячеек 4 и включается их автоконтроль, что обеспечивает блокировку среды от источников ложного потенциала поиска.

С нулевого плеча трщггера 12 выдает. ся разрешение элементам И 1О и 14. на считывание адресов коммутируемых макроячеек и элементу И 15 на прохождение потенциала поиска. Элемент И 11. имеет неразрешение со стороны единичного плеча .того же триггера.

.При подаче единичного потенциала.по шине 18 разрешения настройки получают разрешения триггеры регистра 7 на ввод адресов макроячеек - приемников и открывается второй элемент И 19 блокировки. В течение всего BpeivieHH настройки еди- ница, записанная в регистр 7, цикличес-. ; ки возбуждает все сигналы настройки ячеек.

Установка каждого канала связи осуществляется в два шага.

При первом щаге устанавливается кра-гчайший канал между макроячейкой - источником и -вспомогательными макро$гчейками. При втором шаге устанавливается кратчайший канал между макроячейкой - приемником и ячейками у становленного канала.

В присутствии единицы во втором, разряде формирователя команд 9-возбужда-. ётся сигнал признака источника. При пер. вом шаГе настройки он через элемент И 10 возбуждает вход макроячейки источника с адресом, хранящимся в блоке 22. Ячейки 4 обеспечивают распростра. нение в коммутирующем поле 1 круговой волны потенциала поиска.

Достигнув вспомогательных макроячеек по кратчайшему пути, он через элемент ИЛИ 16, элемент И 15 и элемент ИЛИ 13, поступая на шину записи ячеек 4, 5 записывает построенное прадерево каналов. Дальнейшее распространение волны потенциала поиска прекращается. В построенном прадереве лишь кратчайшая ветвь соединена с вспомогательными 10 макроячейками.

На втором такте возбуждается сигнал -записи, который по счетному входу уста навливает триггер 12 в единичное состояние и повторяет запись прадерева. Нуле- 15 вой потенциал, снимаемый с нулевого плеча этого триггера, запирает элементы И 10, 14, 15 и поступает на шины для ввода потенциала вьщеления всех вспомогательных макроячеек, что обеспечивает 0 неразрешение ячейкам- 4 установленного канала изменения состояний.

На третьем такте возбуждается сигнал, считы аюший адреса макроячеек - приемников, но он не достигает блока 22 в 5 связи с тем, что элемент И 14 заперт.

На четвертом такте возбуждается сигнал, восстанавливающий проводимость ячеек. Поступая на шину восстановления проводимости, он устанавливает все ячейки 0 4, не принадлежащие каналу, в проводящее состояние.

На.пятом такте вновь возбуждается сигнал, переводящий в нулевое состояние и контролирующий входы ячеек. 5 На этом заканчивается первый шаг настрюйки.

При втором щаге .сигналы следуют в то .же последовательности.

На щестом такте сигнал признака источника через элемент И 11 поступает на щину задания распределенного признака источника. Одновременно через инвертор .17 снимаются потенциалы выделения с .макро5иеек приемников ранее установлен5 ных каналов. Это обеспечивает возбухаде- ние в коммутирующем поле 1 линейной волны потенциала поиска. Вывод его из вспомогательных верщин заблокирован элементом И 15, в результате чего волна достигает макроячеек приемников, соединяя их кратчайшими ветвями с вспомогате11ьным каналом.

На седьмом такте сигнал записи через элемент ИЛИ 13 записывает построенное прадерево в память ячеек 4 и по счетному входу устанавливает триггер 12 в нулевое состояние.

На восьмом такте считывающий сигнал через элемент И 14 считывает с блока 22 адреса мароячеек - приемников, значащими разрящами которых устанавливаются триггеры регистра 7 в единичное состояние.

Совпадение единиц на входах выходных .элементов И 8 порождают на выходах элементов ИЛИ-НЕ 24 нулевые потенциала выделения, прикладываемые ,к соответ ствуюшим щинам ввода макроячеек приемников. Регистр 7 обеспечивает память их адресов на время настройки, что необходимо для сохранения ранее установленных каналов.

На девятом такте сигналом восстановления проводимости формирователя команд 9 восстанавливается проводимость ячеек 4, не принадлежащих каналам.

Поскольку потенциалы выделения с вспомогательных макроячеек сняты, отрезок вспомогательного канала, не использованного в дереве основного канала, также разрушается.

На десятом такте вновь сигналом конт роля осушествляется перевод входов ячеек в нулевое состояние и контроль их исправности, что 8Шляётся подготовительной операцией для построения новых каналов связи.

Предмет изобретения

Коммутирующее устройство, содеряса- щее рещетчатое коммутирующее поле, в узлах которого расположены ячейки, входы и выходы которых соединены с соответ ствуюшими выходами и входами смежных ячеек, блок памяти, выходы которого соединены с входами периферийных ячеек коммутирующего поля через элементы ИЛИ-НЕ, к другим входам которых подключены горизонтальные входные информационные щины, управляющий блок, выходы которого соединены с входами периферийных ячеек у коммутирующего поля через другие элементы ИЛИ-НЕ, R другим входам которых подключены вертикальные входные информационные шины, другие выходы блока, управления для установки в исходное состояние, для перевода входов в нулевое состояние обнуления, для автоконтроля, для записи прадерева кана8

эв и восстановления проводимости ячеекссединены с соответствующими управляю щими щинами всех ячеек, инфор ационнь-е выходы периферийных ячеек коммутируюшего поля соединены с информационными горизонтальными и вертикальными щинами, отличаю а1ееся тем, что, с целью повышения надежности и коммутационных возможностей в узлах коммутирующего

поля введены макроячейки, образованные группами ячеек, в которых входы и выходы каждой ячейки соединены с соответствующими выходами и входами всех ячеек данной макроячейки и одной из ячеек смежной t/акроячейки, щина для записи праде- рева каналов соединена с выходом элеме та ИЛИ, формирующего сигнал записи, входы которого соединены с выходом первого элемента И блокировки и выходом

сигнала записи формирователя команд, соединенного также со счетным входом триггера, задающего щаг настройки, нулевой выход которого соединен с щинами для выделения вспомогательных макроячеек,

выходные щины которых соединены. через элемент ИЛИ с входом первого элемента И блокировки, другой вход которого содинен с нулевым выходом триггера, задающего шаг настройки, который соединен

также с входами элементов И для считывания адресов макроячеек - источников и приемников, другие входы которых соединены соответственно с выходами сигналов признаков источника и приемника формчрователя команд, а выходы - с входами запоминающего блока, единичный выход триггера, задающего щаг настройки, содинен с входом элемента И признака распределенного источника, второй вход

которого соединен с выходом сигнала признака источника формирователя команд, а выход - с соответотвзтощей шиной макроячеек коммутирующего поля и через инвертор с входами выходных элементов

И, ругие входы которых соединены с единичными выходами триггеров регистра адресов макроячеек - приемников и щиной для разрещения настройки, соединенной также с входом второго элемента И блокировки, второй вход которого соединен с щиной тактовых импульсов, а выход - с входом формирователя команд.

Фиг.2

Авторы

Даты

1975-07-25—Публикация

1973-10-30—Подача