Изобретение относится к техническим средствам обучения и может использоваться для макетирования цифровых устройств при обучении вычислительной технике.

Цель изобретения - расширение дидактических возможностей устройства.

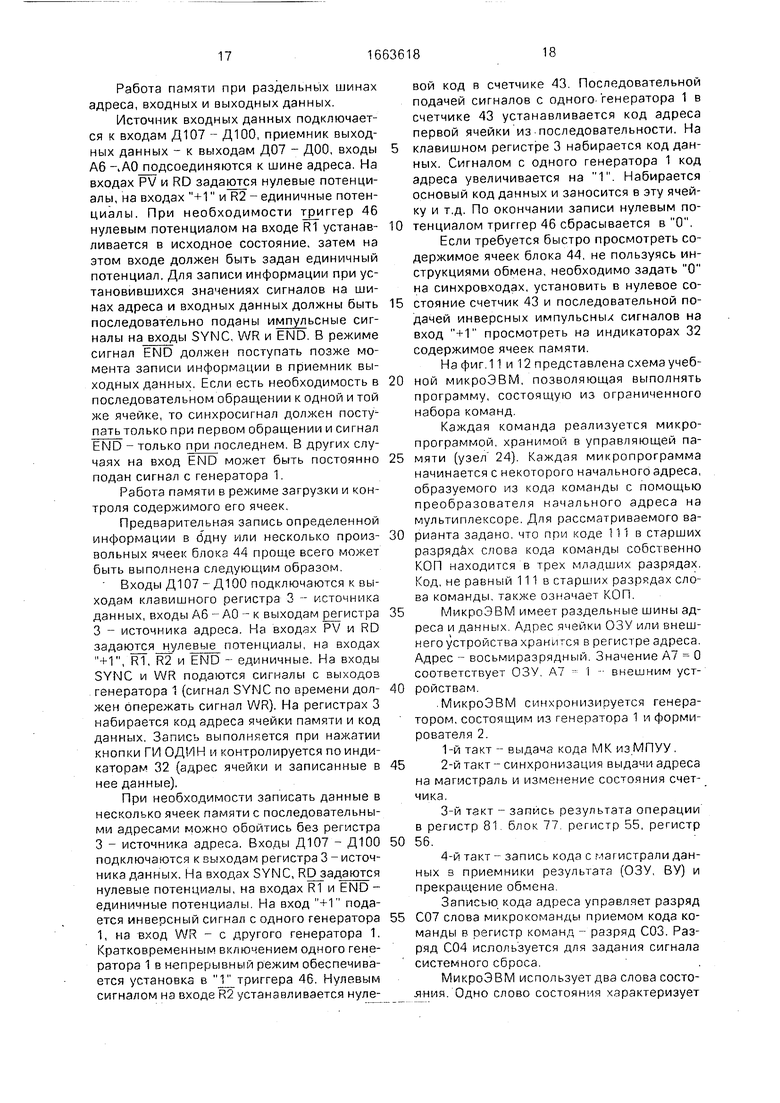

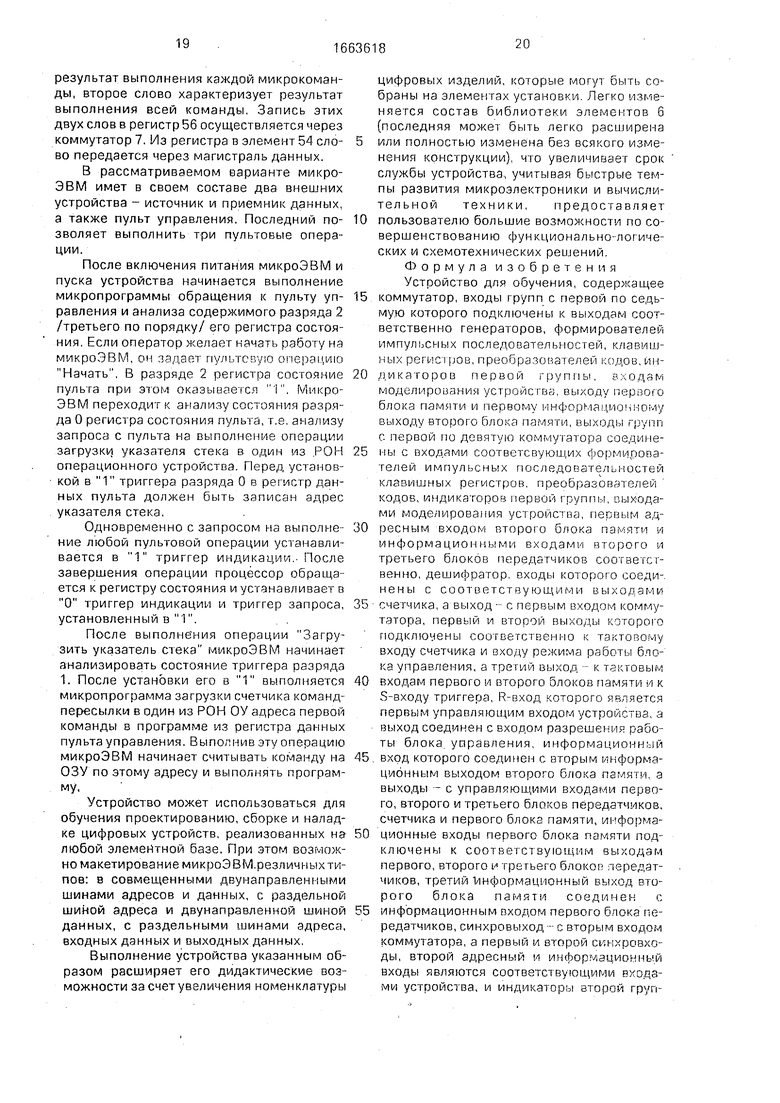

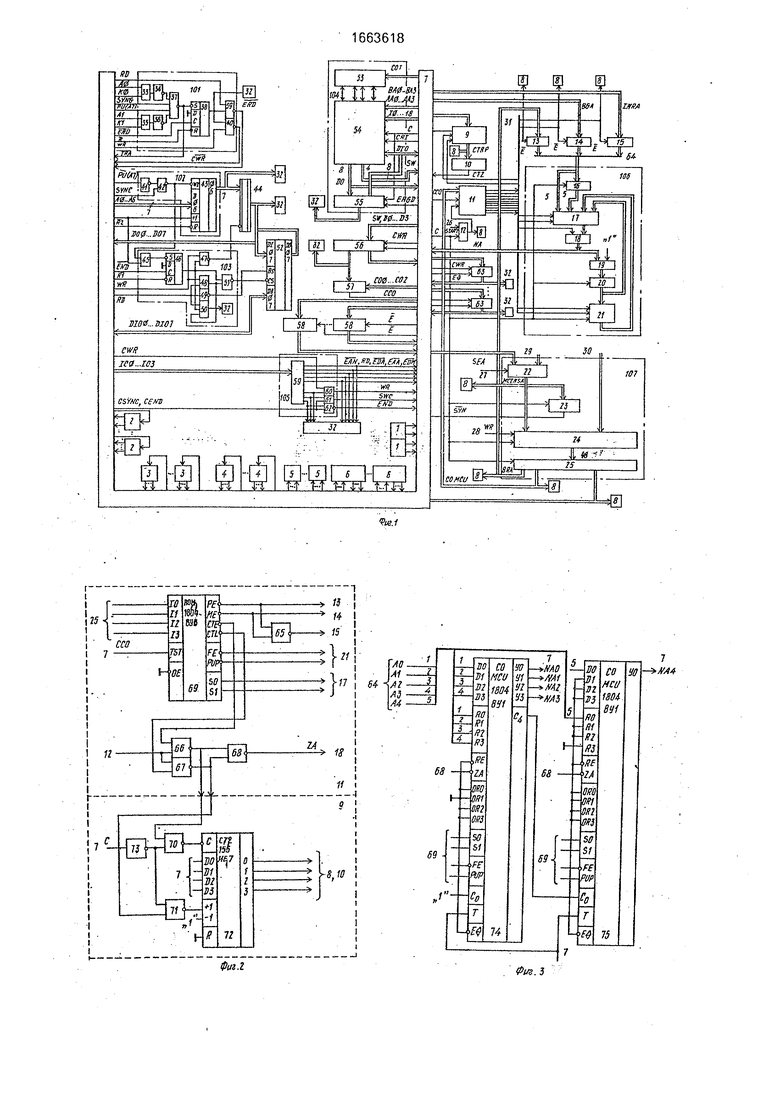

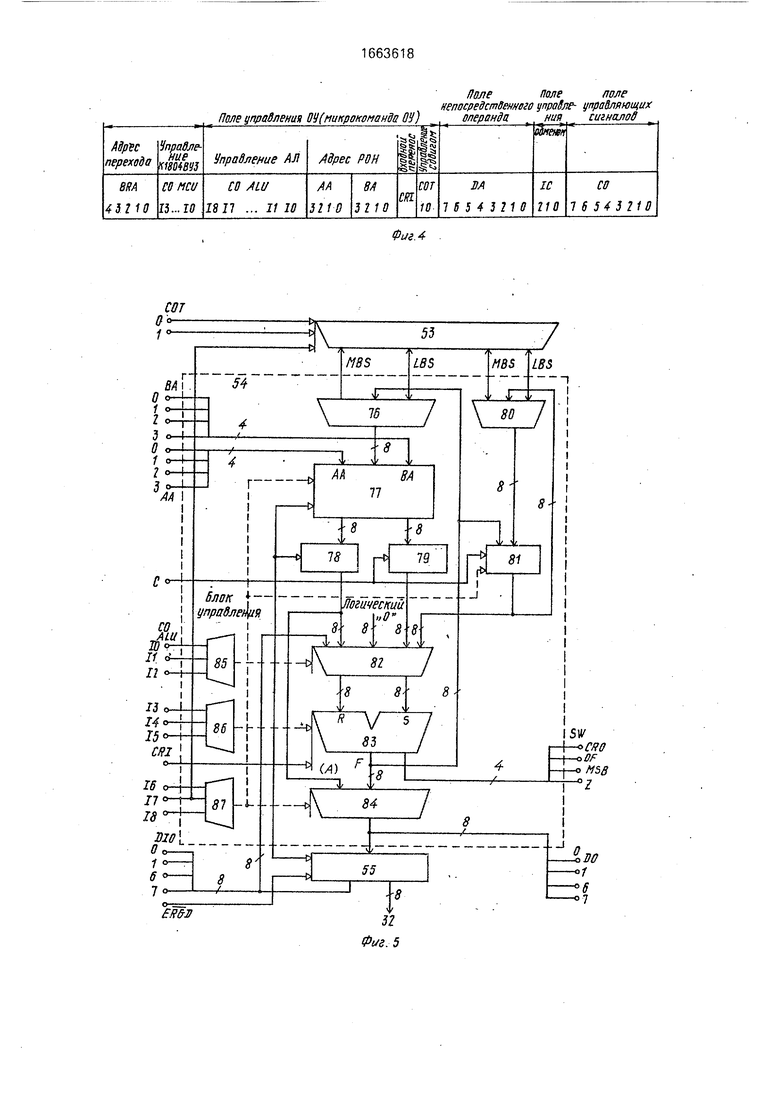

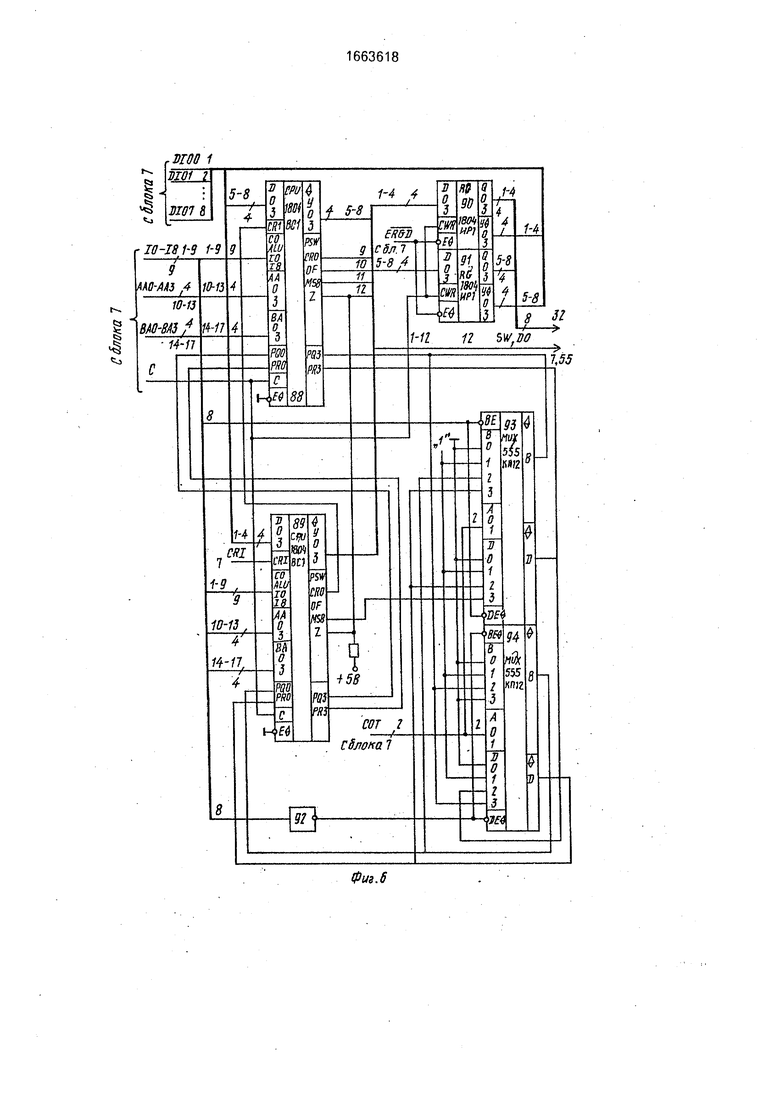

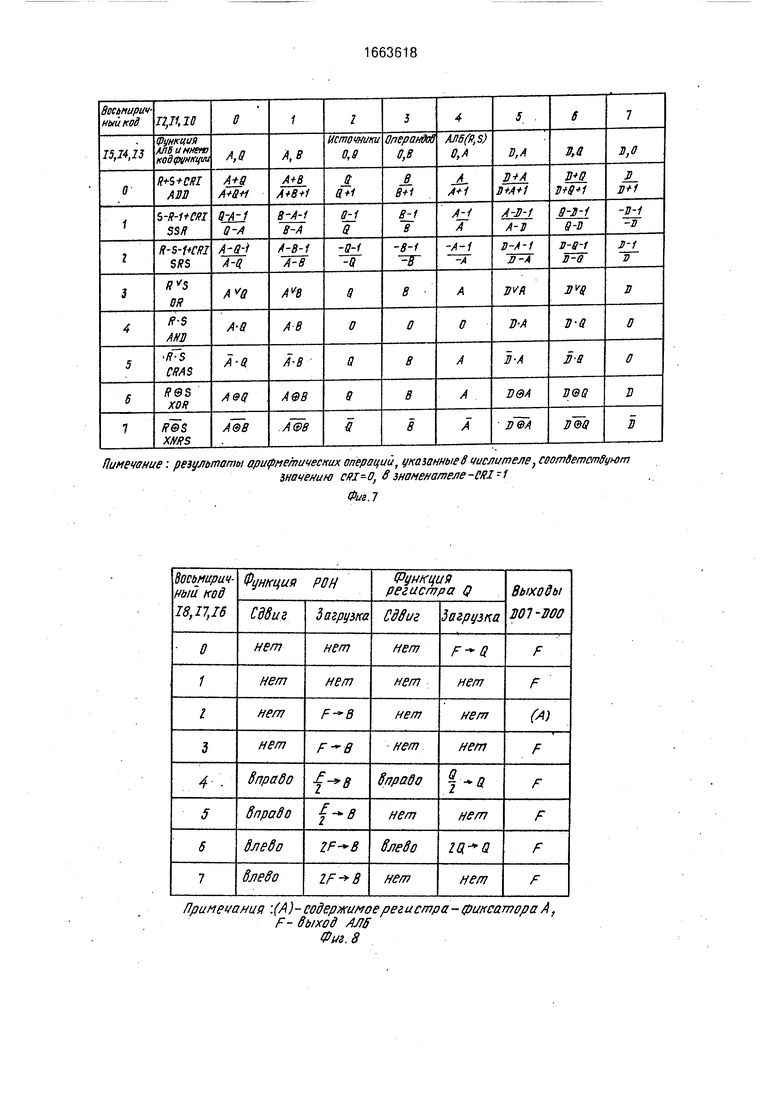

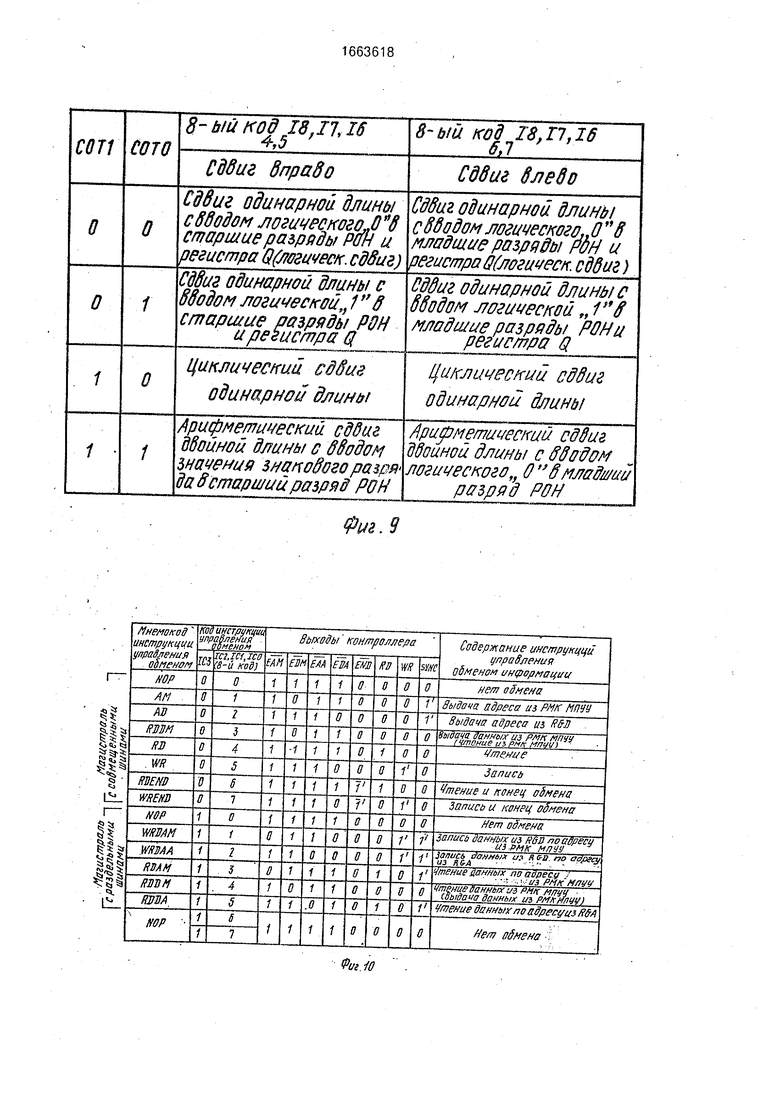

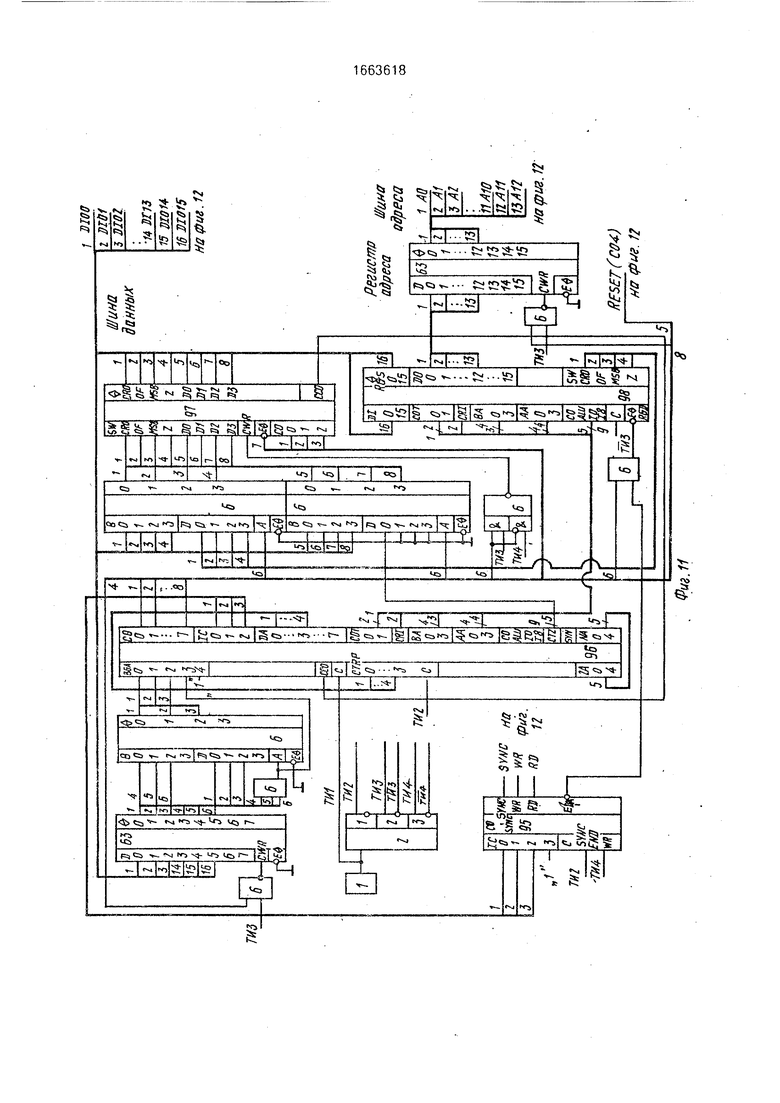

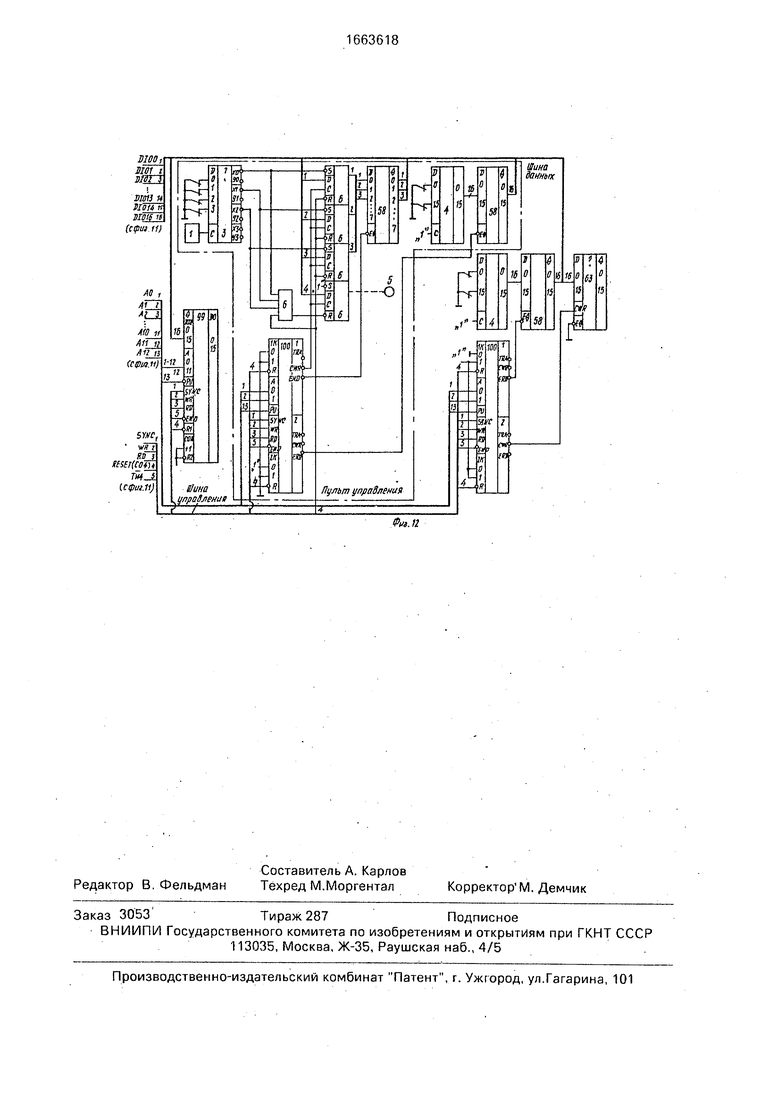

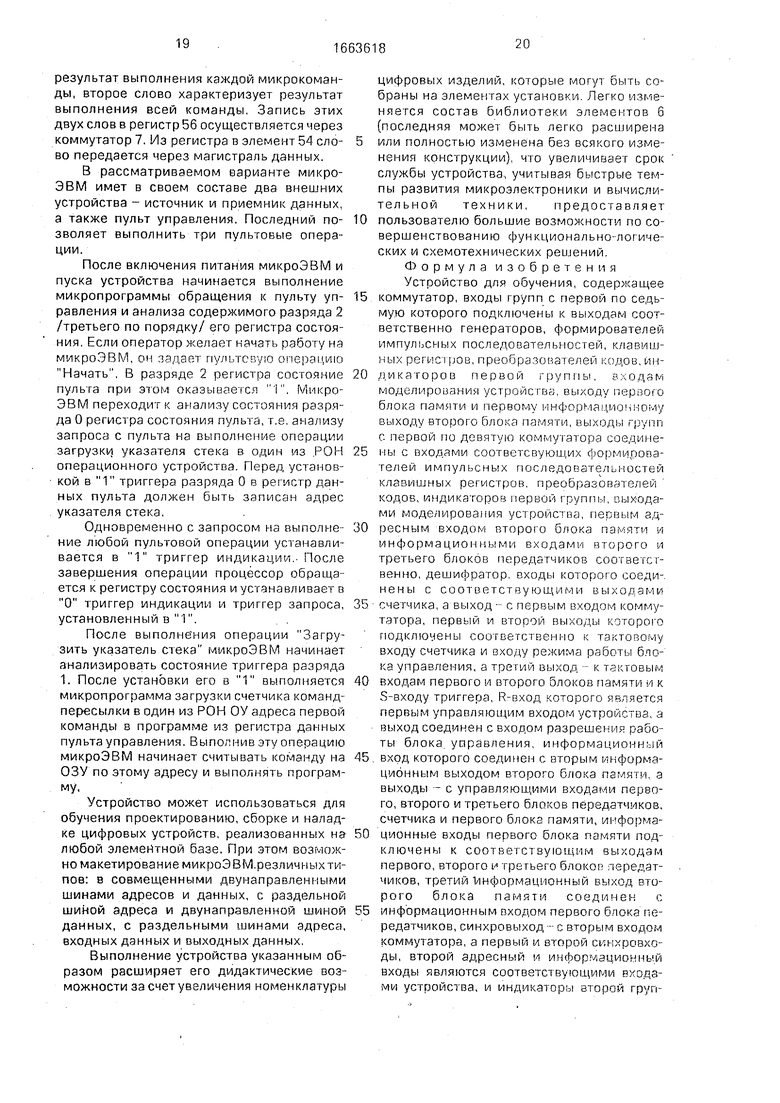

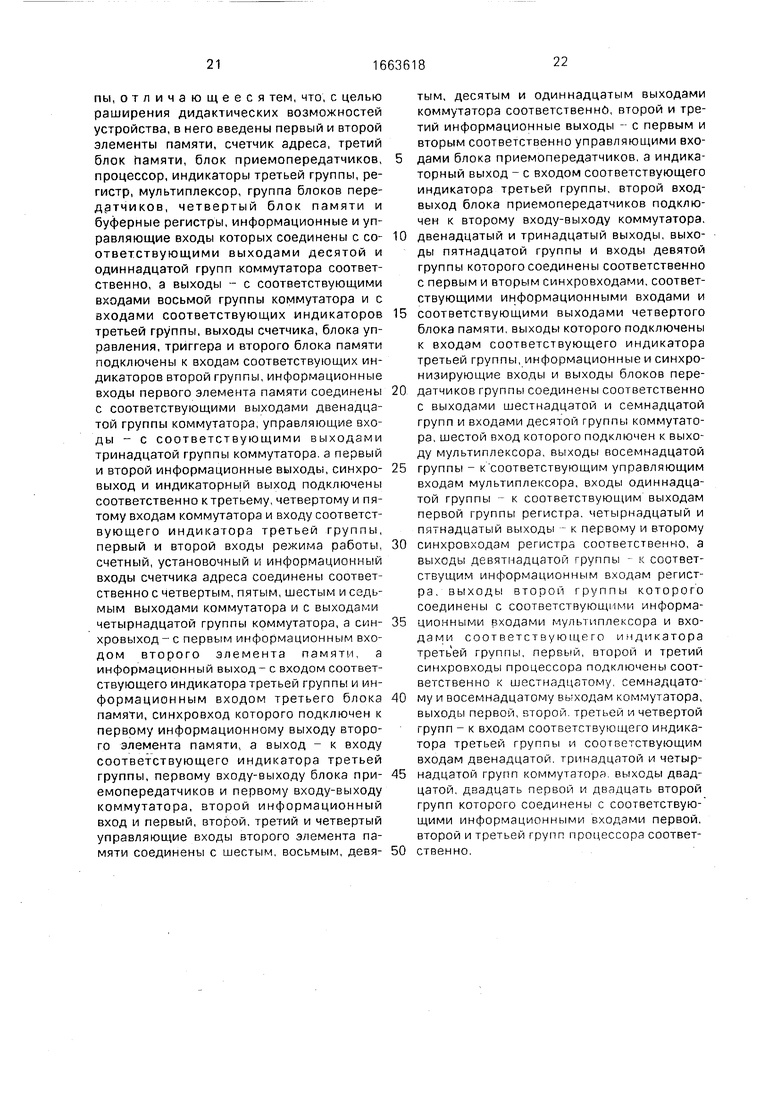

На фиг.1 представлена структурная схема предлагаемого устройства; на фиг.2 - пример реализации счетчика и блока управления; на фиг.З - пример реализации регистров, мультиплексора, узла элементов И, сумматора, и узла памяти, на фиг.4 - формат микрокоманды, на фиг 5 - структурная схема центрального процессорного элемента; на фиг.6 - пример реализации сдвига, центрального процессорного элемента и регистра, на фиг.7 - источники операндов для арифметико-логического блока (АЛБ) и выполняемые над ними операции; на фиг,8 - таблица, поясняющая процедуру управления АЛБ (управления выбором приемника

результата), на фиг 9 таблица поясняющая процедуру управления типом сдвига на фиг.10 - график управления обменом информации, на фиг 11 и 12 - предлагаемое устройство, пример взаимодействия его блоков.

Устройство для обучения содержит генераторы 1 импульсов формирователи 2 импульсных последовательностей клавишные регистры 3, преобразователи 4 кодов индикаторы 5 цифровые (изучаемые) эле менты 6, коммутатор 7 индикаторы 8, счет чик 9 циклов, дешифратор 10 блок 11 управления, триггер 12 начального пугка блоки 13, 14 15 передатчиков регистр 16 адреса, мультиплексор 17 узел 18 элемен тов И, сумматор 19, регистр 20 узел 21 памяти (стек) мультиплексор 22 дешифратор 23, узел 24 памяти, регистр 25 микрокоманд вход 26 начального пуска первый 27 и вто рой 28 входы задания режима работы фуп

О

о

со о

00

пу адресных входов 29, группу информационных входов 30, внутреннюю шину 31 управления, индикаторы 32, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 33, элемент НЕ 34, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 35, элемент НЕ 36, элемент И-НЕ 37, триггер 38, элементы И-НЕ 39 и 40, элемент НЕ 41, элемент И-НЕ 42, счетчик 43 (адреса), блок 44 памяти, элемент И 45, триггер 46, элемент И-НЕ 47, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 48, элемент НЕ 49, элемент И 50, элемент И-НЕ 51, блок 52 приемодатчиков, блок 53 сдвига, центральный процессорный элемент 54, регистр 55 данных, регистр 56, мультиплексор 57, блоки 58 передатчиков, узел 59 памяти, элементы И 60 и 61, элемент И-НЕ 62, буферные регистры 63 и внутреннюю шину 64,

Блок 11 управления содержит элементы И-НЕ 65 - 68 и узел 69 постоянной памяти.

Счетчик 9 содержит элементы И-НЕ 70 и 71, четырехразрядный счетчик 72 и элемент НЕ 73.

Регистр 16, мультиплексор 17, узел 18, сумматор 19, регистр 20 и узел 21 реализованы на двух микросхемах 74 и 75 типа К1804ВУ1.

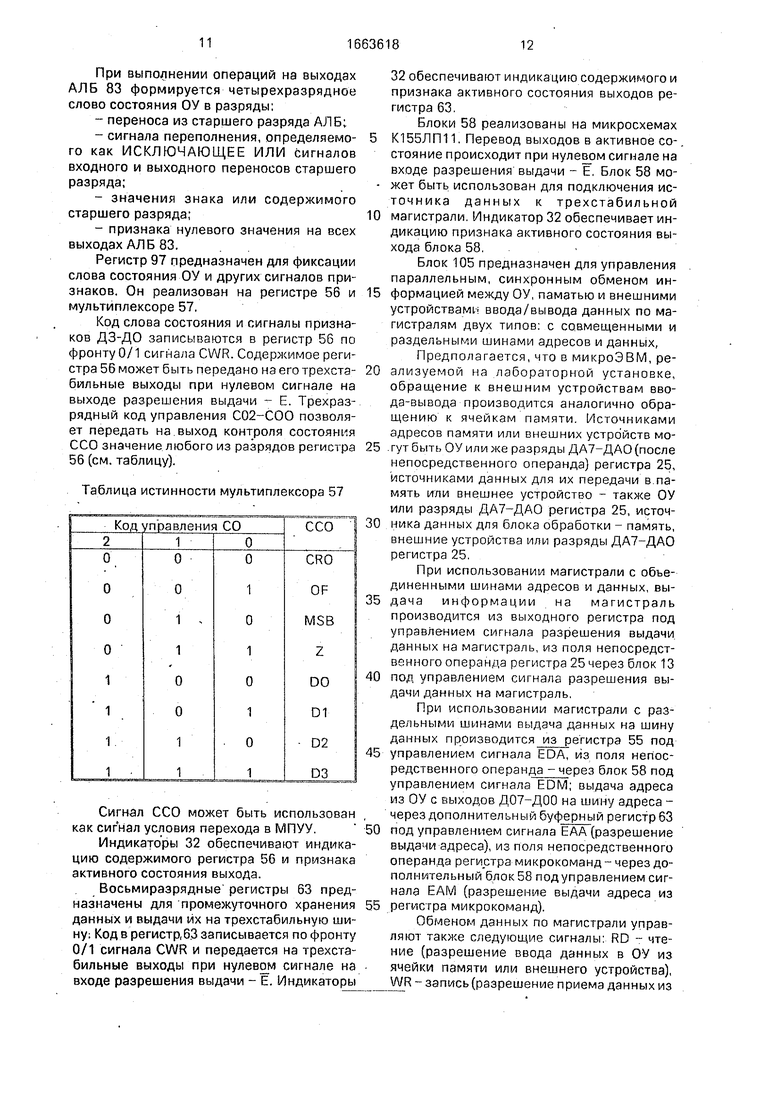

Центральный процессорный элемент 54 содержит сдвигатель 76 записи, блок 77 сверхоперативной памяти (16РОН), регистры-фиксаторы 78 и 79, сдвигатель 80 записи регистра, регистр 81, селектор 82 источника данных, АЛБ 83, селектор 84 выходных данный и дешифраторы 85 - 87,

Блок 53, элемент 54 и регистр 55 реализованы на микропроцессорных секциях 88 и 89 (К1804ВС1), регистрах 90 и 91 (К1804ЙР1), элементе НЕ 92 и мультиплексорах 93 и 94(К555КП12). На фиг. 11 и 12 показаны системный контроллер 95, блок 96 микропрограммного управления, регистр 97 слова состояния, операционный блок 98, блок 99 оперативной памяти контроллеры 100 внешних устройств ввода-вывода.

На фиг.1 указаны также укрупненные узлы устройства: элемент 101 памяти, счетчик 102, элемент 103 памяти, процессор 104, блоки 105 - 107 памяти.

Коммутатор 7 сконструирован по модульному принципу и содержит два уровня конструктивных модулей: первый уровень - ячейка, второй - панель, В состав установки входят четырепанели, вставляемые в проем стОла. Каждая панель представляет собой каркас с тремя вертикальными перегородками, разделяющими лицевую плоскость панели на четыре части - вертикальные ряды, в которые устанавливаются ячейки управляющего модуля ячейки цифровых

элементов, ячейка операционного устройства (ОУ), регистра слова состояния, буферных регистров, передатчиков, системного контроллера, контроллеров ввода-вывода и блока памяти.

В установке могут быть использованы ячейки различных типоразмеров, различное сочетание которых позволяет заполнить весь вертикальный ряд панели. Индикаторы

0 5, 8 и 32 входят в состав соответствующих ячеек.

Генератор 1 вырабатывает импульсы положительной и отрицательной полярности. В режиме одиночных импульсов (тумб5 лер в положении ГИ ОДИН) на выходе генератора 1 после каждого нажатия кнопки ГИ ОДИН в момент ее отпускания появляется один импульс. Одновременно инверсный сигнал появляется на инверсном выходе ге0 нератора 1. В непрерывном режиме (тумблер в положении ГИ НЕПР) на выходах генератора 1 присутствуют последовательности прямых и инверсных импульсов.

Фомирователь 2 предназначен для пол5 учения серии из трех импульсов, сдвинутых относительно фронта 0/1 запускающего сигнала.

Клавишный регистр 3 построен на регистрах хранения и используется для задания

0 значений операндов и управляющих сигналов, сохраняющих постоянное значение в течение нескольких циклов работы исследуемой схемы. Код на входах регистра 3 задается нажатием клавиш. Прием информации

5 в регистры 3 производится в течение единичного сигнала, подаваемого на вход С. При незакоммутированном входе С код на выходах разрядов регистра 3 повторяет код на соответствующих клавишах.

0Код на входах преобразователя 4 кода

также задается нажатием клавиш. Нажатие клавиш К-го разряда приводит к появлению импульсного инверсного сигнала на выходе Хк, совпадающего по времени с импульс5 ным сигналом, поданным на вход С преобразователя 4. Значение сигнала на выходе УК равно, в этом случае 1. При отжатой клавише инверсный импульсный сигнал присутствует на выходе YK, a XK 1. При

0 незакоммутированном входе С преобразователь 4 выполняет функцию клавишного регистра, когда код на выходах Y повторяет код на соответствующих клавишах.

Библиотека цифровых элементов 6 мо5 жет состоять из одного элемента, например, из элемента 3 И-НЕ, может быть определена из личного опыта разработчика, состоять из схем, соответствующих какой-либо серии или сериям микросхем, например серии К155, может состоять из постоянной части,

определенной каким-либо способом, и переменной, зависящей от специфических особенностей проектируемых устройств.

Коммутация элементов 6 осуществляется при помощи соединительных шнуров, вставляемых в коммутационные гнезда соответствующих ячеек.

Устройство работает следующим образом.

На этапе подготовки к работе с установкой производится разработка функциональных схем исследуемого устройств, схем для его настройки и испытаний. Определяется состав необходимых ячеек.

Генераторы 1, формирователи 2, преобразователи 4 используются для построения схем синхронизации и начальной установки, При необходимости для этих же целей могут использоваться некоторые из цифровых элементов 6.

Индикаторы 5, 8 и 32 служат для наблюдения за состояниями отдельных точек исследуемого устройства.

Исследуемый узел собирается на остальных элементах устройства. Узел 24 используется для хранения 32-и 48-разрядных слоев микрокоманд. Мультиплексор 22 позволяет передавать на адресные входы узла 24 код из двух источников: с клавиш на лицевой панели (группа адресных входов 29) 1А4- 1АО и с внешних входов 2А4-2АО под управлением сигнала 27 на входе выбора адреса.

В режиме записи данных{сигнал на входе 28 равен 1) код слова микрокоманды, набранный на клавиатуре (группа информационных входов 30), заносится в выбранную ячейку узла 24 и одновременно передается в регистр 25.

В режиме считывания код слова микрокоманды из выбранной ячейки заносится в регистр 25 по фронту 0/1 сигнала С. Свето- диоды индикаторов обеспечивают индикацию содержимого регистра 25 и кода адреса микрокоманды. На входы адреса 2А должен быть подан код адреса следующей микрокоманды с выходов узла 18. На выходы узел 18 может передавать код адреса из памяти источников: регистра 16, счетчика микрокоманд (сумматор 19 и регистр 20), узла 21, внутренней магистрали (шины) 64 (А4-АО) и с входа установки нулевого значения адреса. Выбор одного из первых четырех источников адреса выполняется мультиплексором 17 под управлением двухразрядного кода при единичном значении управляющего сигнала, при нулевом значении которого код на выходах узла 18 равен 00000.

Регистр 16 используется в качестве буфера для хранения кода А4-АО, записываемого в него по фронту 0/1 тактового сигнала С. Сумматор 19 позволяет увеличить код на

5 1.

Узел 21 состоит из накопителя, указателя стека, регистра записи адреса и схемы записи-считывания. Он обеспечивает при реализации последовательности микроко- 10 манд выполнение перехода с возвратом. Глубина узла 21 равна 4. Управление узлом 21 осуществляется сигналами с блока 11. Узел 21 может работать в трех режимах: считывание без изменения состояния стека, 15 запись эдреса из счетчика микрокоманд после увеличения на единицу содержимого указателя стека, выталкивание адреса микрокоманды и уменьшение на единицу содержимого указателя стека. В режиме

0 считывания содержимое указателя стека остается без изменения и на выходе узла 21 выдается информация из ячейки накопителя, на которую указывает указатель стека. В режиме записи по фронту 0/1 тактового сиг5 нала С увеличивается на 1 содержимое указателя стека и одновременно код адреса из регистра 20 фиксируется в регистре записи адреса стека. Схема записи-считывания переводится в режим записи и по фронту 1/0

0 тактового сигнала С происходит запись адреса микрокоманды в выбранную ячейку накопителя. В режиме выталкивания по фронту 0/1 тактового сигнала С происходит уменьшение на единицу содержимого ука5 зателя стека схема записи-считывания переходит в режим считывания и на выход узла 21 выводится адрес микрокоманды, записанный в стек предпоследним.

На внутреннюю магистраль (шину) 64

0 информации может поступать от трех внешних источников Такой информацией может являться код адреса перехода из поля адреса перехода,задаваемого непосредственно в слове микрокоманды, код начального ад5 реса микрокопрограммы и код адреса вектора прерывания

Выдача адресов на магистраль 64 управляется сигналами на входах блоков 13 - 15. Соответствующие индикаторы 8 обеспе0 чивают индикацию активного состояния выходов соответствующего блока 13 - 15.

Четырехразрядный счетчик 9 используется для организации циклического повторения одной или группы из нескольких

5 микрокоманд. Режим работы счетчика 9 задается сигналами на его входах параллельной загрузки и обратного счета. Сигнал, поступающий с блока 11 на вход параллельной загрузки счетчика 9 циклов, разрешает прием1 кода длительности цикла с входов

при единичном значении сигнала С. Код длительности цикла может приниматься от внешнего источника или же с регистра 25. Состояние счетчика 9, равное 0000, характеризуется наличием единичного потенциала на выходе дешифратора 10. Содержимое счетчика 9 высвечивается на светодиодах индикаторов 8.

Блок 11 формирует набор выходных сигналов на основе кода управления, задаваемого соответствующим полем слова микрокоманды. Одновременно блок 11 выполняет функцию проверки сигнала условия ССО (контроля состояния). Всего блок 11 позволяет реализовать 16 различных инструкций управления последовательностью микрокоманд.

Триггер 12 позволяет осуществлять начальный пуск микропрограммы. Нажатием клавиши СТАРТ триггер 12 устанавливается в 11. На лицевой панели это подтверждается свечением соответствующего индикатора 8. Установка триггера 12 в единичное состояние приводит к появлению нулевого кода на выходах узла 18. С появлением первого импульса на входе С в регистр 25 будет записано слово микрокоманды, хранившееся в узле 24 по нулевому адресу, а триггер 12 сброшен в О. Дальнейшая последовательность микрокоманд зависит от кода инструкции управления,записанной в нулевой микрокоманде.

Перед работой в узел 24 должна быть загружена микропрограмма. Должен быть определен адрес каждого слова микрокоманды и двоичные коды содержимого микрокоманды как ее адресной части (поле адреса перехода и поле инструкции управления последовательностью микрокоманд), так и управляющей части, Фактически назначение двоичных разрядов управляющей части зависит от ОУ, управляемого проектируемым микропрограммным устройством управления (МПУУ). Структура слова микрокоманды, используемой при построении микроЭВМ на данном устройстве показана на фиг.4. Назначение различных полей слова микрокоманды в этом случае однозначно определено и указано на клавиатуре набора данных. Выходы регистра 25, кроме разря- дов, относящихся к адресной части, выведены на лицевую панель.

Перед записью микропрограммы рекомендуется выполнить коммутацию источников и приемников сигналов с входами и выходами микропрограммного УУ. Подается сигнал с генератора 1 или формирователя 2 на вход С, выходы узла 18 соединяются с входами 2А. Сигналы на входы ДЗ-ДО в тактовый вход счетчика 9, входы BGA INRA

МПУУ подаются в случае необходимости. То же самое относится к коммутации выходных сигналов МПУУ. Сигнал CTZ может быть подан на один из входов регистра 97 слова состояния. На выходе SYN МПУУ подается . импульсный синхросигнал, совпадающий с моментом считывания слова микрокоманды из нулевой ячейки узла 24. При работе в динамическом режиме этот сигнал может 0 быть подан на вход синхронизации коммутатора входных каналов осциллографа.

Работа МПУУ в режиме записи микропрограммы,

Нажимают клавишу WR, выбирают ис- 5 точник адреса 1А - нажимают клавишу SEA. Код адреса слова микрокоманды набирает- ся на клавишах 1А4-1АО и индицируется на светодиодах индикаторов 8, код слова микрокоманды набирается на соответствующих 0 клавишах (входы 30), При нажатии кнопки ГИ ОДИН генератора 1 на вход С МПУУ поступает одиночный импульс и код слова микрокоманды заносится в выбранную ячейку узла 24, и одновременно высвечива- 5 ется на индикаторах 8. Любые исправления обеспечиваются повторной записью.

Работа МПУУ в режиме проверки содержимого ячеек узла 24.

Нажимают клавишу SEA, отжимают кла- 0 вишу WR. Код адреса проверяемого слова набирается на клавишах 1А4-1АО и высвечивается на индикаторах 8. При нажатии кнопки ГИ ОДИН код слова микрокоманды заносится в регистр 25 и высвечивается на 5 индикаторах 8.

При необходимости на входы 2А4-2АО подаются сигналы с выходов пятиразрядного двоичного счетчика, собранного на элементах 6. Клавиша SEA отжимается. 0 Тактовый сигнал +Г этого счетчика повремени должен предшествовать сигналу на входе С МПУУ Последовательное нажатие кнопки ГИ ОДИН позволяет быстро просмотреть содержимое всех ячеек узла 24. 5 Работа МПУУ в режиме считывания микропрограммы.

Отжимают клавишу WR, отжимают клавишу SEA, На входы 2А поданы сигналы с

0 выходов NA узла 18. Нажимают клавишу СТАРТ. При поступлении каждого тактового сигнала на с МПУУ слово микрокоманды считывается в регистр 25 микрокоманды и засвечивается на индикаторах 8. Работа

5 блоков 13-15 передатчиков, подключенных к внутренней магистрали 64 МПУУ, контролируется на соответствующих элементах 8ЕА. На индикаторах 8 высвечивается код адреса микрокоманды, которая будет считываться из узла 24 в следующем такте. .

МПУУ может быть использовано не только в составе микроЭВМ, а и с произвольным ОУ. В этом случае назначение двоичных разрядов управляющей части слова микрокоманды определяется конкретной ситуацией. Блок 107 может быть использован Автономно в качестве источника линейных управляющих последовательностей или же.в качестве управляющей памяти МПУУ с другой структурной организацией. При работе с узлом 24 в таких случаях на входы 2А подаются сигналы с внешнего источника адреса, поля слова микрокоманды BRA и COMOV не используются.

Блок 77 содержит 16 регистров с двумя независимыми каналами выбора информации по адресам А и В, задаваемым сигналами на входах ячейки - ААЗ-ААО, ВАЗ-ВАО. На выходе блока 77 находятся два 8-разрядных регистра-фиксатора 78 и 79, управляемых сигналом на тактовом входе С. Запись в блок 77 возможна только по адресу 8 как без сдвига, так и со сдвигом вправо (в сторону младших разрядов) или влево (в сторону старших разрядов) на один разряд, что выполняется сдвигателем 76.

Регистры 78 и 79 каналов А и В блока 77 являются регистрами с однофазной записью и однотактным управлением. При единичном значении сигнала на выходе С информация из выбранного регистра передается на вход регистра-фиксатора 78 (79) и фиксируется в нем в момент фронта 1/0 тактового сигнала. Информация сохраняется в регистрах-фиксаторах 78, 79 до тех пор пока на входе С вновь не появится единичный сигнал.

Из блока 77 можно считывать одновременно два слова. Если на входах ААЗ-ААО и ВАЗ-ВАО будут заданы одинаковые коды, в регистрах 78 и 79 будут записаны одинаковые данные. Запись данных по адресу В начинается в момент фронта 1/0 тактового сигнала. Результат фиксируется в выбранном регистре в момент 0/1.

Селектор 82 на входе АЛ Б 83 позволяет комбинировать в качестве операндов информацию из пямяти источников:

-с внешней шины данных (входы Д107- ДЮО);

-по каналам А и В из блока 77;

-из дополнительного регистра 81;

-сусловного источника нулевого значения.

Селектор 84 позволяет передавать на выходы Д07-ДОО данные с выхода АЛБ 83 или из регистра 78 канала А блока 77.

Основным назначением регистра 81 является реализация алгоритмов операций умножения и деления. В ряде случаев регистр 81 может использоваться в качестве дополнительного аккумулятора. Запись данных в регистр 81 осуществляется по фронту 0/1 тактового сигнала. 5Дешифраторы 85 - 87 формируют управляющие сигналы, показанные штриховыми линиями на фиг.5.

Блок 53, реализованный на мультиплексорах 93 и 94, под воздействием сигналов

10 управления типом сдвига СОТ1, СОТО коммутирует информацию на двунаправленные шины старших и младших разрядов сдвига- телей 76 и 80.

Восимиразрядный выходной регистр 55

5 данных, реализованный на микросхемах (регистрах) 90 и 91. позволяет в момент фронта 0/1 сигнала на тактовом входе С фиксировать информацию /результат операции/ с выходов Д07-ДОО. Трехстабиль0 ные выходные регистры 55 соединены с входами Д107-Д100 При подаче нулевого сигнала на вход разрешения выдачи данных содержимое регистра 55 передается на двунаправленную трехстабильную шину дан5 ных.

Соответствующие индикаторы 32 обеспечивают индикацию содержимого регистра 55 и признака активного состояния его выходов.

0Управляющие работой селектора 82,

АЛБ 83 и селектора 84 осуществляется сигналами в соответствии с фиг.7.

Код в разрядах 12-10 определяет источники операндов для АЛБ 83. Две комби5 нации операндов Д В и ВЦне реализуются.

Код в разрядах 15 - 13 задает вид функции АЛБ 831 три арифметические операции в двоичном коде и пять порязрядных логи0 ческих операций

Арифметические операции в блоке 83 выполняются с учетом арифметического значения входного переноса по правилам дополнительного кода при представлении

5 отрицательных чисел.

Код в разрядах 18-16 определяет приемник результата операции, выполнявшый- ся в АЛБ 83, точнее говоря, определяет характер передачи информации;

0- передачу на выходы Д07-ДОО без записи во внутренние регистры;

-запись в регистр 81;

-запись в блок 77 по адресу, заданному кодом на входах ВАЗ-ВАО;

5- запись в блок 77 со сдвигом;

-запись в блок 77 со сдвигом с одновременным сдвигом регистра 81.

Сдвиговые операции выполняются блоком 53 под управлением кода в разрядах СОЛ, СОТО микрокоманды ОУ.

При выполнении операций на выходах АЛБ 83 формируется четырехразрядное слово состояния ОУ в разряды;

-переноса из старшего разряда АЛБ;

-сигнала переполнения, определяемого как ИСКЛЮЧАЮЩЕЕ ИЛИ сигналов входного и выходного переносов старшего разряда;

-значения знака или содержимого старшего разряда;

-признака нулевого значения на всех выходах АЛБ 83.

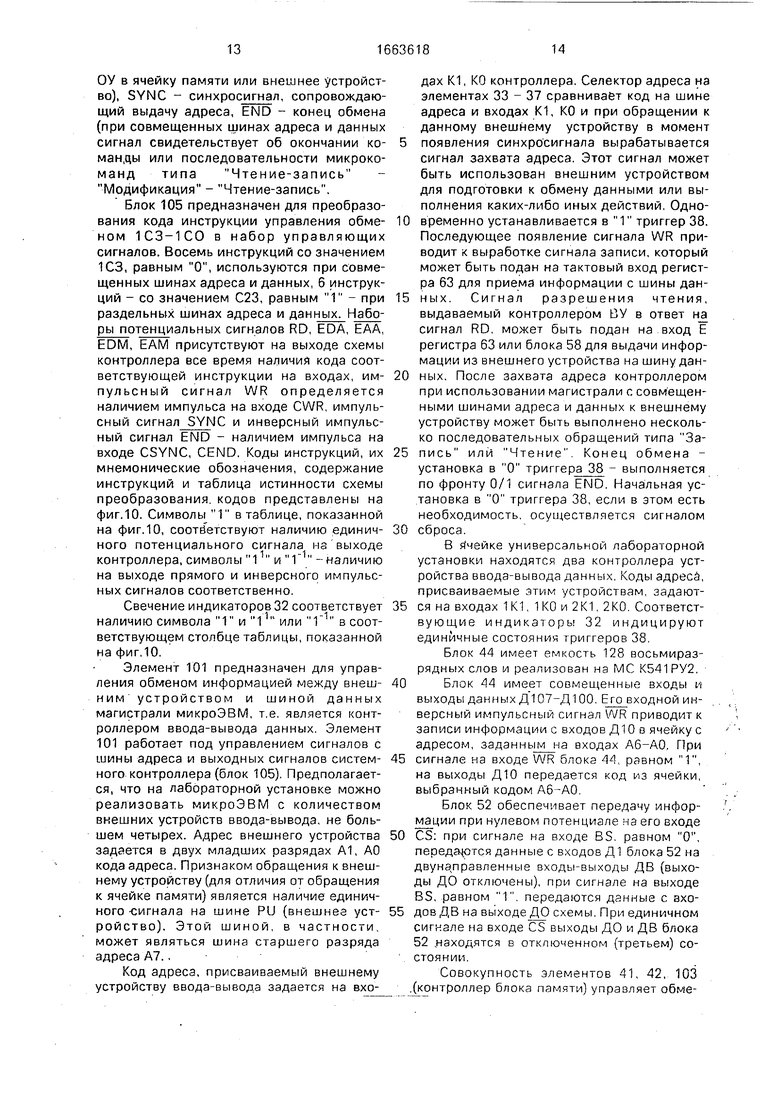

Регистр 97 предназначен для фиксации слова состояния ОУ и других сигналов признаков. Он реализован на регистре 56 и мультиплексоре 57.

Код слова состояния и сигналы признаков ДЗ-ДО записываются в регистр 56 по фронту 0/1 сигнала CWR. Содержимое регистра 56 может быть передано на его трехста- бильные выходы при нулевом сигнале на выходе разрешения выдачи - Е. Трехразрядный код управления С02-СОО позволяет передать на выход контроля состояния ССО значение любого из разрядов регистра 56 (см. таблицу).

Таблица истинности мультиплексора 57

Сигнал ССО может быть использован как сигнал условия перехода в МПУУ.

Индикаторы 32 обеспечивают индикацию содержимого регистра 56 и признака активного состояния выхода.

Восьмиразрядные регистры 63 предназначены для промежуточного хранения данных и выдачи их на трехстабильную шину: Код в регистр,63 записывается по фронту 0/1 сигнала CWR и передается на трехста- бильные выходы при нулевом сигнале на входе разрешения выдачи - Е. Индикаторы

32 обеспечивают индикацию содержимого и признака активного состояния выходов регистра 63.

Блоки 58 реализованы на микросхемах

К155ЛП11. Перевод выходов в активное со-.

стояние происходит при нулевом сигнале на

входе разрешения выдачи - Е, Блок 58 мо- жет быть использован для подключения источника данных к трехстабильной

0 магистрали. Индикатор 32 обеспечивает индикацию признака активного состояния выхода блока 58.

Блок 105 предназначен для управления параллельным, синхронным обменом ин5 формацией между ОУ, паматью и внешними устройствами ввода/вывода данных по магистралям двух типов: с совмещенными и раздельными шинами адресов и данных, Предполагается, что в микроЭВМ, ре0 ализуемой на лабораторной установке, обращение к внешним устройствам ввода-вывода производится аналогично обращению к ячейкам памяти. Источниками адресов памяти или внешних устройств мо5 гут быть ОУ или же разряды ДА7-ДАО (после непосредственного операнда) регистра 25, источниками данных для их передачи в память или внешнее устройство - также ОУ или разряды ДА7-ДАО регистра 25, источ0 пика данных для блока обработки - память, внешние устройства или разряды ДА7-ДАО регистра 25.

При использовании магистрали с объединенными шинами адресов и данных, вы5 дача информации на магистраль производится из выходного регистра под управлением сигнала разрешения выдачи данных на магистраль, из поля непосредственного операнда регистра 25 через блок 13

0 под управлением сигнала разрешения выдачи данных на магистраль.

При использовании магистрали с раздельными шинами выдача данных на шину данных производится из регистра 55 под

5 управлением сигнала EDA, из поля непосредственного операнда - через блок 58 под управлением сигнала EDM; выдача адреса из ОУ с выходов Д07-ДОО на шину адреса - через дополнительный буферный регистр 63

0 под управлением сигнала ЕАА (разрешение выдачи адреса), из поля непосредственного операнда регистра микрокоманд - через дополнительный блок 58 под управлением сигнала ЕАМ (разрешение выдачи адреса из

5 регистра микрокоманд).

Обменом данных по магистрали управляют также следующие сигналы: RD - чтение (разрешение ввода данных в ОУ из ячейки памяти или внешнего устройства), WR - запись (разрешение приема данных из

ОУ в ячейку памяти или внешнее устройство), SYNC - синхросигнал, сопровождающий выдачу адреса, END - конец обмена (при совмещенных шинах адреса и данных сигнал свидетельствует об окончании команды или последовательности микрокоманд типа Чтение-запись Модификация - Чтение-запись.

Блок 105 предназначен для преобразования кода инструкции управления обменом 1СЗ-1СО в набор управляющих сигналов. Восемь инструкций со значением 1СЗ, равным О, используются при совмещенных шинах адреса и данных, 6 инструкций - со значением С23, равным 1 - при раздельных шинах адреса и данных. Наборы потенциальных сигналов RD, EDA, EAA, EDM, ЕАМ присутствуют на выходе схемы контроллера все время наличия кода соответствующей инструкции на входах, импульсный сигнал WR определяется наличием импульса на входе CWR, импульсный сигнал SYNC и инверсный импульсный сигнал END - наличием импульса на входе CSYNC, CEND. Коды инструкций, их мнемонические обозначения, содержание инструкций и таблица истинности схемы преобразования, кодов представлены на фиг.10. Символы 1 в таблице, показанной на фиг.10, соответствуют наличию единичного потенциального сигнала на выходе контроллера, символы 11 и Г1 -наличию на выходе прямого и инверсного импульсных сигналов соответственно.

Свечение индикаторов 32 соответствует наличию символа 1 и 1 или 1 в соответствующем столбце таблицы, показанной на фиг,10.

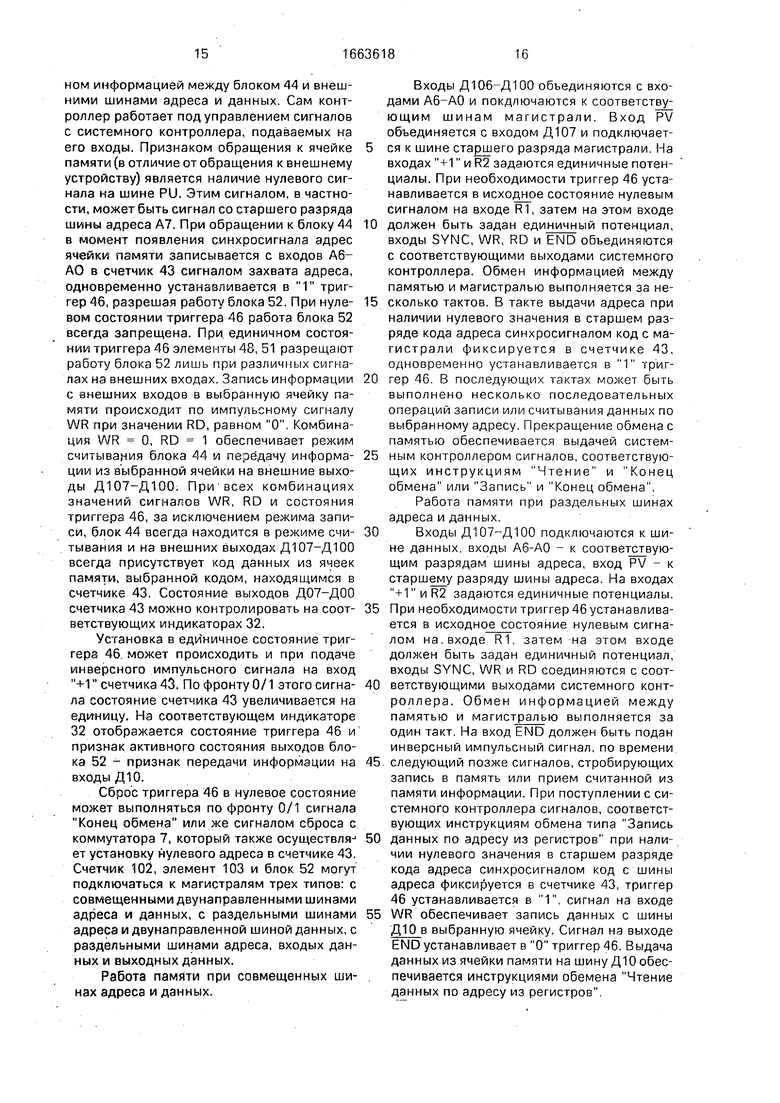

Элемент 101 предназначен для управления обменом информацией между внешним устройством и шиной данных магистрали микроЭВМ, т.е. является контроллером ввода-вывода данных. Элемент 101 работает под управлением сигналов с шины адреса и выходных сигналов системного контроллера (блок 105). Предполагается, что на лабораторной установке можно реализовать микроЭВМ с количеством внешних устройств ввода-вывода, не большем четырех. Адрес внешнего устройства задается в двух младших разрядах А1, АО кода адреса. Признаком обращения к внешнему устройству (для отличия от обращения к ячейке памяти) является наличие единичного -сигнала на шине PU (внешнее устройство). Этой шиной, в частности, может являться шина старшего разряда адреса А7..

Код адреса, присваиваемый внешнему устройству ввода-вывода задается на входах К1, КО контроллера. Селектор адреса на элементах 33 - 37 сравнивает код на шине адреса и входах К1, КО и при обращении к данному внешнему устройству в момент 5 появления синхросигнала вырабатывается сигнал захвата адреса. Этот сигнал может быть использован внешним устройством для подготовки к обмену данными или выполнения каких-либо иных действий. Одно10 временно устанавливается в 1 триггер 38. Последующее появление сигнала WR приводит к выработке сигнала записи, который может быть подан на тактовый вход регистра 63 для приема информации с шины дан5 ных. Сигнал разрешения чтения, выдаваемый контроллером ВУ в ответ на сигнал RD, может быть подан на вход Е регистра 63 или блока 58 для выдачи информации из внешнего устройства на шину дан0 ных. После захвата адреса контроллером при использовании магистрали с совмещенными шинами адреса и данных к внешнему устройству может быть выполнено несколько последовательных обращений типа За5 пись или Чтение. Конец обмена - установка в О триггера 38 - выполняется по фронту 0/1 сигнала END. Начальная установка в О триггера 38, если в этом есть необходимость, осуществляется сигналом

0 сброса.

В Ячейке универсальной лабораторной установки находятся два контроллера устройства ввода-вывода данных. Коды адреса, присваиваемые этим устройствам, задают5 ся на входах 1К1, 1 КО и 2К1, 2КО. Соответствующие индикаторы 32 индицируют единичные состояния триггеров 38.

Блок 44 имеет емкость 128 восьмиразрядных слов и реализован на МС К541 РУ2.

0Блок 44 имеет совмещенные входы и

выходы данных Д107-Д100. Его входной инверсный импульсный сигнал VA/R приводит к записи информации с входов Д10 в ячейку с адресом, заданным на входах А6-АО. При

5 сигнале на входе W.R блока 44, равном 1, на выходы Д10 передается код из ячейки, выбранный кодом А6-АО.

Блок 52 обеспечивает передачу инфор- . мации при нулевом потенциале на его входе

0 CS: при сигнале на входе BS, равном О, передается данные с входов Д1 блока 52 на двунаправленные входы-выходы ДВ (выходы ДО отключены), при сигнале на выходе BS, равном 1, передаются данные с зхо5 дов ДВ на выходе ДО схемы. При единичном сигнале на входе CS выходы ДО и ДВ блока 52 .находятся в отключенном (третьем) состоянии.

Совокупность элементов 41, 42, 103 .(контроллер блока памяти) управляет обменом информацией между блоком 44 и внешними шинами адреса и данных. Сам контроллер работает под управлением сигналов с системного контроллера, подаваемых на его входы. Признаком обращения к ячейке памяти (в отличие от обращения к внешнему устройству) является наличие нулевого сигнала на шине PU. Этим сигналом, в частности, может быть сигнал со старшего разряда шины адреса А7. При обращении к блоку 44 в момент появления синхросигнала адрес ячейки памяти записывается с входов А6- АО в счетчик 43 сигналом захвата адреса, одновременно устанавливается в 1 триггер 46, разрешая работу блока 52. При нуле- вом состоянии триггера 46 работа блока 52 всегда запрещена. При единичном состоянии триггера 46 элементы 48, 51 разрещают работу блока 52 лишь при различных сигналах на внешних входах. Запись информации с внешних входов в выбранную ячейку памяти происходит по импульсному сигналу WR при значении RD, равном О. Комбинация WR О, RD 1 обеспечивает режим считывания блока 44 и передачу информа- ции из выбранной ячейка на внешние выходы Д107-Д100. При всех комбинациях значений сигналов WR, RD и состояния триггера 46, за исключением режима записи, блок 44 всегда находится в режиме счи- тывания и на внешних выходах Д107-Д100 всегда присутствует код данных из ячеек памяти, выбранной кодом, находящимся в счетчике 43. Состояние выходов Д07-ДОО счетчика 43 можно контролировать на соот- ветствующих индикаторах 32.

Установка в единичное состояние триггера 46. может происходить и при подаче инверсного импульсного сигнала на вход +1 счетчика 43. По фронту 0/1 этого сигна- ла состояние счетчика 43 увеличивается на единицу. На соответствующем индикаторе 32 отображается состояние триггера 46 и признак активного состояния выходов блока 52 - признак передачи информации на входы Д10.

Сброс триггера 46 в нулевое состояние может выполняться по фронту 0/1 сигнала Конец обмена или же сигналом сброса с коммутатора 7, который также осуществля-1 ет установку нулевого адреса в счетчике 43. Счетчик 102, элемент 103 и блок 52 могут подключаться к магистралям трех типов: с совмещенными двунаправленными шинами адреса и данных, с раздельными шинами адреса и двунаправленной шиной данных, с раздельными шинами адреса, входых данных и выходных данных.

Работа памяти при совмещенных шинах адреса и данных.

Входы Д106-Д100 объединяются с входами А6-АО и покдлючаются к соответствующим шинам магистрали. Вход PV объединяется с входом Д107 и подключается к шине старшего разряда магистрали. На входах +1 и R2 задаются единичные потенциалы. При необходимости триггер 46 устанавливается в исходное состояние нулевым сигналом на входе R1, затем на этом входе должен быть задан единичный потенциал, входы SYNC, WR, RD и END объединяются с соответствующими выходами системного контроллера. Обмен информацией между памятью и магистралью выполняется за несколько тактов. В такте выдачи адреса при наличии нулевого значения в старшем разряде кода адреса синхросигналом код с магистрали фиксируется в счетчике 43, одновременно устанавливается в 1 триггер 46. В последующих тактах может быть выполнено несколько последовательных операций записи или считывания данных по выбранному адресу. Прекращение обмена с памятью обеспечивается выдачей системным контроллером сигналов, соответствующих инструкциям Чтение и Конец обмена или Запись и Конец обмена,

Работа памяти при раздельных шинах адреса и данных.

Входы Д107-Д100 подключаются к шине данных, входы А6-АО - к соответствующим разрядам шины адреса, вход PV - к старшему разряду шины адреса. На входах +1 и R2 задаются единичные потенциалы. При необходимости триггер 46 устанавливается в исходное состояние нулевым сигналом на. входе R1, затем на этом входе должен быть задан единичный потенциал, входы SYNC, WR и RD соединяются с соответствующими выходами системного контроллера. Обмен информацией между памятью и магистралью выполняется за один такт. На вход END должен быть подан инверсный импульсный сигнал, по времени следующий позже сигналов, стробирующих запись в память или прием считанной из памяти информации. При поступлении с системного контроллера сигналов, соответствующих инструкциям обмена типа Запись данных по адресу из регистров при наличии нулевого значения в старшем разряде кода адреса синхросигналом код с шины адреса фиксируется в счетчике 43, триггер 46 устанавливается в 1, сигнал на входе WR обеспечивает запись данных с шины Д10 в выбранную ячейку. Сигнал на выходе END устанавливает в О триггер 46. Выдача данных из ячейки памяти на шину Д10 обеспечивается инструкциями обемена Чтение данных по адресу из регистров.

Работа памяти при раздельных шинах адреса, входных и выходных данных.

Источник входных данных подключается к входам Д107 - Д100, приемник выходных данных - к выходам Д07 - ДОО, входы А6 -,АО прдсоединяются к шине адреса. На входах PV и RD задаются нулевые потенциалы, на входах +1 и R2 - единичные потенциалы. При необходимости тр иггер 46 нулевым потенциалом на входе R1 устанавливается в исходное состояние, затем на этом входе должен быть задан единичный потенциал. Для записи информации при установившихся значениях сигналов на шинах адреса и входных данных должны быть последовательно поданы импульсные сигналы на входы SYNC, WR и END. В режиме сигнал END должен поступать позже момента записи информации в приемник выходных данных. Если есть необходимость в последовательном обращении к одной и той же ячейке, то синхросигнал должен посту- пзть только при первом обращении и сигнал END - только при последнем. В других случаях на вход END может быть постоянно подан сигнал с генератора 1.

Работа памяти в режиме загрузки и контроля содержимого его ячеек.

Предварительная запись определенной информации в 5дну или несколько произвольных ячеек блока 44 проще всего может быть выполнена следующим образом.

Входы Д107 - Д100 подключаются к выходам клавишного регистра 3 - источника данных, входы А6 АО - к выходам регистра 3 - источника адреса. На входах PV и RD задаются нулевые потенциалы, на входах +1, R1, R2 и END - единичные. На входы SYNC и WR подаются сигналы с выходов генератора 1 (сигнал SYNC по времени должен опережать сигнал WR). На регистрах 3 набирается код адреса ячейки памяти и код данных. Запись выполняется при нажатии кнопки ГИ ОДИН и контролируется по индикаторам 32 (адрес ячейки и записанные в нее данные).

При необходимости записать данные в несколько ячеек памяти с последовательными адресами можно обойтись без регистра 3 - источника адреса. Входы Д107 - Д100 подключаются к выходам регистра 3 - источника данных. На входах SYNC, RD задаются нулевые потенциалы, на входах R1 и END - единичные потенциалы. На вход +1 подается инверсный сигнал с одного генератора 1, на вход WR - с другого генератора 1. Кратковременным включением одного генератора 1 в непрерывный режим обеспечивается установка в JT триггера 46. Нулевым сигналом на входе R2 устанавливается нулевой код в счетчике 43. Последовательной подачей сигналов с одного- генератора 1 в счетчике 43 устанавливается код адреса первой ячейки из-последовательности. На 5 клавишном регистре 3 набирается код данных. Сигналом с одного генератора 1 код адреса увеличивается на 1. Набирается основый код данных и заносится в эту ячейку и т.д. По окончании записи нулевым по0 тенциалом триггер 46 сбрасывается в О.

Если требуется быстро просмотреть содержимое ячеек блока 44, не пользуясь инструкциями обмена, необходимо задать О на синхровходах, установить в нулевое со5 стояние счетчик 43 и последовательной подачей инверсных импульсных сигналов на вход +1 просмотреть на индикаторах 32 содержимое ячеек памяти.

На фиг.11 и 12 представлена схема учеб0 ной микроЭВМ, позволяющая выполнять программу, состоящую из ограниченного набора команд.

Каждая команда реализуется микропрограммой, хранимом в управляющей па5 мяти (узел 24). Каждая микропрограмма начинается с некоторого начального адреса, образуемого из кода команды с помощью преобразователя начального адреса на мультиплексоре. Для рассматриваемого ва0 рианта задано, что при коде 111 в старших разрядах слова кода команды собственно КОП находится в трех младших разрядах. Код, не равный 111 в старших разрядах слова команды, также означает КОП.

5МикроЭВМ имеет раздельные шины адреса и данных. Адрес ячейки ОЗУ или внешнего устройства хранится в регист ре адреса. Адрес - восьмиразрядный. Значение А7 О соответствует ОЗУ. А7 - 1 - внешним уст0 ройствам.

.МикроЭВМ синхронизируется генератором, состоящим из генератора 1 и формирователя 2.

1-й такт -- выдача кода МК из.МПУУ.

52-й такт-синхронизация выдачи адреса

на магистраль и изменение состояния счетчика.

3-й такт - запись результата операции в регистр 81 блок 77 регистр 55, регистр

0 56.

4-й такт - запись кода с магистрали данных в приемники результата (ОЗУ, ВУ) и прекращение обмена

Записью кода адреса управляет разряд

5 С07 слова микрокоманды приемом кода команды в регистр команд - разряд СОЗ. Разряд С04 ислользуется для задания сигнала системного сброса.

МикроЭВМ использует два слова состо лния. Одно слово состояния характеризует

результат выполнения каждой микрокоманды, второе слово характеризует результат выполнения всей команды. Запись этих двух слов в регистр 56 осуществляется через коммутатор 7. Из регистра в элемент 54 слово передается через магистраль данных.

В рассматриваемом варианте микро- ЭВМ имет в своем составе два внешних устройства - источник и приемник данных, а также пульт управления. Последний позволяет выполнить три пультовые операции.

После включения питания микроЭВМ и пуска устройства начинается выполнение микропрограммы обращения к пульту управления и анализа содержимого разряда 2 /третьего по порядку/ его регистра состояния. Если оператор желает начать работу на микроЭВМ, он задает пультсг,ую операцию Начать, В разряде 2 регистра состояние пульта при этом оказывав ел 1. Микро- ЭВМ переходит к анализу состояния разряда 0 регистра состояния пульта, т.е. анализу запроса с пульта на выполнение операции загрузки указателя стека в один из РОН операционного устройства. Перед установкой в 1 триггера разряда 0 в регистр данных пульта должен быть записан адрес указателя стека.

Одновременно с запросом на выполнение любой пультовой операции устанавливается в 1 триггер индикации,- После завершения операции процессор обращается к регистру состояния и устанавливает в О триггер индикации и триггер запроса, установленный в 1.

После выполнения операции Загрузить указатель стека микроЭВМ начинает анализировать состояние триггера разряда 1. После установки его в 1 выполняется микропрограмма загрузки счетчика команд- пересылки в один из РОН ОУ адреса первой команды в программе из регистра данных пульта управления. Выполнив эту операцию микроЭВМ начинает считывать команду на ОЗУ по этому адресу и выполнять программу,

Устройство может использоваться для обучения проектированию, сборке и наладке цифровых устройств, реализованных на любой элементной базе. При этом возможно макетирование микроЭВМ.резличныхти- пов: в совмеа1енными двунаправленными шинами адресов и данных, с раздельной шиной адреса и двунаправленной шиной данных, с раздельными шинами адреса, входных данных и выходных данных.

Выполнение устройства указанным образом расширяет его дидактические возможности за счет увеличения номенклатуры

цифровых изделий, которые могут быть собраны на элементах установки. Легко изменяется состав библиотеки элементов 6 (последняя может быть легко расширена или полностью изменена без всякого изменения конструкции), что увеличивает срок службы устройства, учитывая быстрые темпы развития микроэлектроники и вычислительной техники, предоставляет 0 пользователю большие возможности по совершенствованию функционально-логических и схемотехнических решений. Формула изобретения Устройство для обучения, содержащее 5 коммутатор, входы групп с первой по седьмую которого подключены к выходам соответственно генераторов, формирователей импульсных последовательностей, клавишных регис ров, преобразователей кодов,ин- 0 дикагоров первой группы, ВАОДЙМ моделирования устройства, выходу первого блока памяти и первому информационному выходу второго блока памяти, выходы групп с первой по девятую коммутатора соедине- 5 ны с входами соответсвующих формирователей импульсных последователиностей клавишных регистров, преобразователей кодов, индикаторов первой группы, выходами моделирования устройства, первым ад- 0 ресным входом второго блока памяти и информационными входами второго -л третьего блоков передатчиков соответственно, дешифратор, входы которого соединены с соответствующими выходами 5 счетчика, а выход - с первым входом коммутатора, первый и второй выходы которого подключены соответственно к тактовому входу счетчика и входу режима работы блока управления, а третий выход - к тактовым 0 входам первого и второго блоков памяти s к 5-входу триггера, R-вход которого является первым управляющим входом устройства, а выход соединен с входом разрешения работы блока управления, информационный 5 вход которого соединен с вторым информационным выходом второго блока памяти, э выходы - с управляющими входами первого, второго и третьего блоков передатчиков, счетчика и первого блока памяти, ит форма- 0 ционные входы первого блока памяти подключены к соответствующим выходам первого, второго i третьего блоков передатчиков, третий Информационный выход второго блока памяти соединен с 5 информационным входом первого блока передатчиков, синхровыход - с вторым входом коммутатора, а первый и второй с нхровхо- ды, второй адресный и информационный входы являются соответствующими входами устройства, и индикаторы второй труппы, отличающееся тем, что, с целью раширения дидактических возможностей устройства, в него введены первый и второй элементы памяти, счетчик адреса, третий блок памяти, блок приемопередатчиков, процессор, индикаторы третьей группы, регистр, мультиплексор, группа блоков передатчиков, четвертый блок памяти и буферные регистры, информационные и управляющие входы которых соединены с со- ответствующими выходами десятой и одиннадцатой групп коммутатора соответственно, а выходы - с соответствующими входами восьмой группы коммутатора и с входами соответствующих индикаторов третьей группы, выходы счетчика, блока управления, триггера и второго блока памяти подключены к входам соответствующих индикаторов второй группы, информационные входы первого элемента памяти соединены с соответствующими выходами двенадцатой группы коммутатора, управляющие входы - с соответствующими выходами тринадцатой группы коммутатора, а первый и второй информационные выходы, синхро- выход и индикаторный выход подключены соответственно к третьему, четвертому и пятому входам коммутатора и входу соответствующего индикатора третьей группы, первый и второй входы режима работы. счетный, установочный и информационный входы счетчика адреса соединены соответственно с четвертым, пятым, шестым и седьмым выходами коммутатора и с выходами четырнадцатой группы коммутатора, а син- хровыход - с первым информационным входом второго элемента памяти, а информационный выход- с входом соответствующего индикатора третьей группы и ин- формационным входом третьего блока памяти, синхровход которого подключен к первому информационному выходу второго элемента памяти, а выход - к входу соответствующего индикатора третьей группы, первому входу-выходу блока при- емопередатчиков и первому входу-выходу коммутатора, второй информационный вход и первый, второй, третий и четвертый управляющие входы второго элемента памяти соединены с шестым, восьмым, девя-

тым, десятым и одиннадцатым выходами коммутатора соответственно, второй и третий информационные выходы - с первым и вторым соответственно управляющими входами блока приемопередатчиков, а индикаторный выход - с входом соответствующего индикатора третьей группы, второй вход- выход блока приемопередатчиков подключен к второму входу-выходу коммутатора, двенадцатый и тринадцатый выходы, выходы пятнадцатой группы и входы девятой группы которого соединены соответственно с первым и вторым синхровходами, соответствующими информационными входами и соответствующими выходами четвертого блока памяти, выходы которого подключены к входам соответствующего индикатора третьей группы, информационные и синхронизирующие входы и выходы блоков передатчиков группы соединены соответственно с выходами шестнадцатой и семнадцатой групп и входами десятой группы коммутатора, шестой вход которого подключен к выходу мультиплексора, выходы восемнадцатой группы - к соответствующим управляющим входам мультиплексора, входы одиннадцатой группы - к соответствующим выходам первой группы регистра, четырнадцатый и пятнадцатый выходы - к первому и второму синхровходам регистра соответственно, а выходы девятнадцатой группы - к соответ- ствущим информационным входам регистра, выходы второй группы которого соединены с соответствующими информационными входами мультиплексора и входами соответствующего индикатора третьей группы, первый, второй и третий синхровходы процессора подключены соответственно к шестнадцатому, семнадцатому и восемнадцатому выходам коммутатора, выходы первой, второй третьей и четвертой групп - к входам соответствующего индикатора третьей группы и соответствующим входам двенадцатой, тринадцатой и четырнадцатой групп коммутатора выходы двадцатой, двадцать первой и двадцать второй групп которого соединены с соответствующими информационными входами первой, второй и третьей групп процессора соответственно.

ф Ч Ф

ШИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| Устройство для контроля памяти | 1983 |

|

SU1280459A1 |

| Устройство для обучения | 1987 |

|

SU1559366A1 |

| Мультимикропрограммная управляющая система | 1983 |

|

SU1133594A1 |

| Процессор программируемого контроллера | 1988 |

|

SU1550515A2 |

| Процессор с микропрограммным управлением | 1982 |

|

SU1124298A1 |

| Процессор программируемого контроллера | 1985 |

|

SU1406595A1 |

| Устройство для сопряжения двух магистралей | 1986 |

|

SU1348874A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1142832A1 |

| Устройство для обмена информацией междуэлЕКТРОННОй ВычиСлиТЕльНОй МАшиНОй(эВМ) и уСТРОйСТВАМи ВВОдА и ВыВОдА | 1979 |

|

SU809140A1 |

Изобретение относится к техническим средствам обучения и может использоваться для макетирования цифровых устройств при обучении вычислительной технике. Цель изобретения - расширение дидактических возможностей устройства. Устройство может использоваться для обучения проектированию, сборке и наладке цифровых устройств, реализованных на любой элементной базе. При этом возможно макетирование микроЭВМ различных типов: с совмещенными двунаправленными шинами адресов и данных, с раздельной шиной адреса и двунаправленной шиной данных, с раздельными шинами адреса, входных данных и выходных данных. 12 ил.

Фиг.г

Фиг. 3

car 0°-

7

вл

-i

о- о-4

о-4

о-1 о-4 о-4

°м

54

4

76

4

ГН

«

ИДЛ4

77

в

A7W | - управления

85

86

И

-n

.

,

L

Н

5Логический

О П 5J

W

8

8

R J 5 83

(А)

F

4f-A

8

54

5J

Т

J2 Фиг. 5

53

7

/IBS

LB5

MBS

LBS

76

80

В

5

rf

J

W

1

8

8

J 5 83

8

54

5

SW

oCffff

n-°fff

MSB 2

.)

iffff f

Ч 7

Пимечание: результаты арифметических операций, указанные в числителе, соответствуют

мочению cffl-ff, ё знаменателе-CRI-1

Фиг Л

Примечания .(А)-содержимое регистра-фиксатора А, F-быход AM Фиг. 8

Ц -ггнй Д# (03}1Э$ЗУ

.// гпсЬон

iJVu urn

own

со

CD

со «о

UD

DOKL I

// Ыф

| Устройство для обучения | 1987 |

|

SU1559366A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1991-07-15—Публикация

1988-01-04—Подача