1

Изобретение относится к области радиоэлектроники и, в частности, к устройствам для измерения серии временных интервалов, следующих непосредственно друг за другом.

В известных устройствах нодсчет импульсов эталонной частоты за измеряемые отрезки времени происходит поочередно двумя счетчиками с запоминанием результатов измерений в запоминающем устройстве и с последующим их считыванием.

Число разрядов каждого счетчика определяется величиной лТ:ииамического диапазона измеряемых отрезков времепп и требуемой точностью их измерения.

Цель изобретения - повышение надежности работы и упрощение устройства.

Это достпгается тем, что старщие разряды обоих счетчиков выполнены общими и через дополнительную схему «ИЛИ подключены к младшим разрядам обоих счетчиков, количество которых в каждом счетчике определяется временем установления кода в счетчике н временем записи в запоминающем устройстве, причем цепи считывания и установки в нуль младших разрядов счетчиков через другие дополнительные схемы «ИЛИ соединены соответственно с цепями считывания и установки в нуль старших разрядов, а выходы заноминающего устройства связаны с установочными входами всех разрядов одного из счетчиков через блок управления, с которым соединены цепи установки в нуль этого счетчика. Один из выходов заноминающего устройства связан с запрещающими входами ключа в цепи генератора эталонной частоты н ключа на входе устройства для подачи на них сигнала переполнения счетчика.

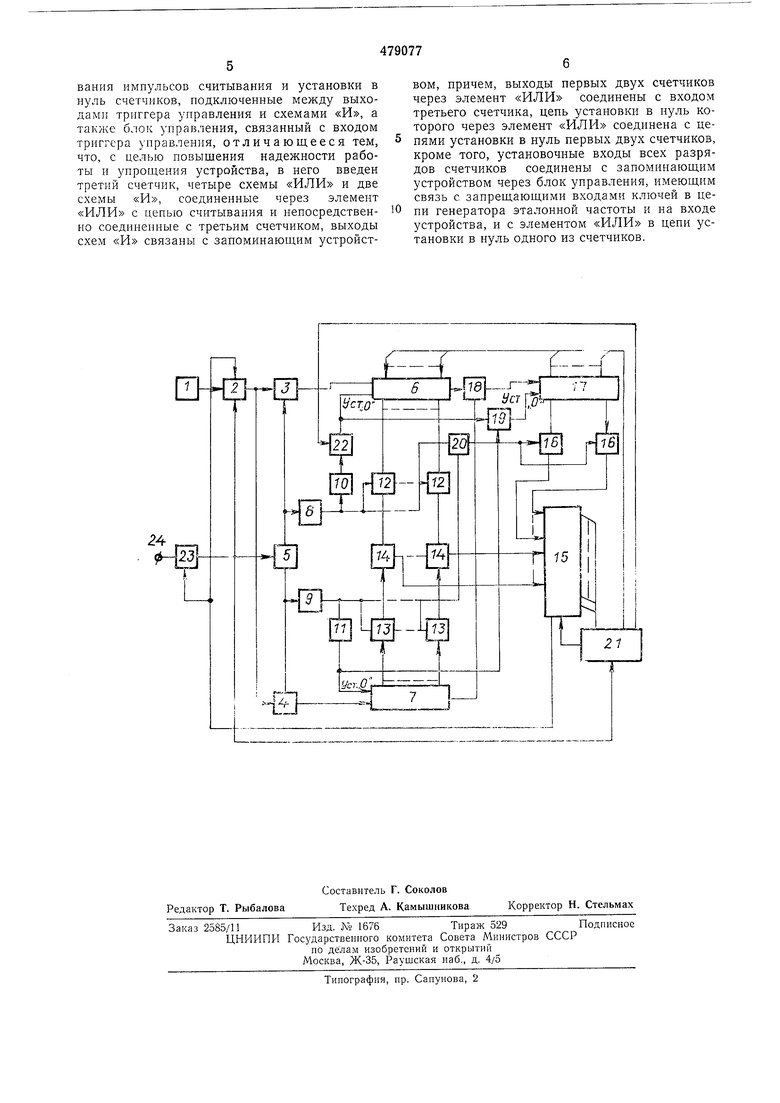

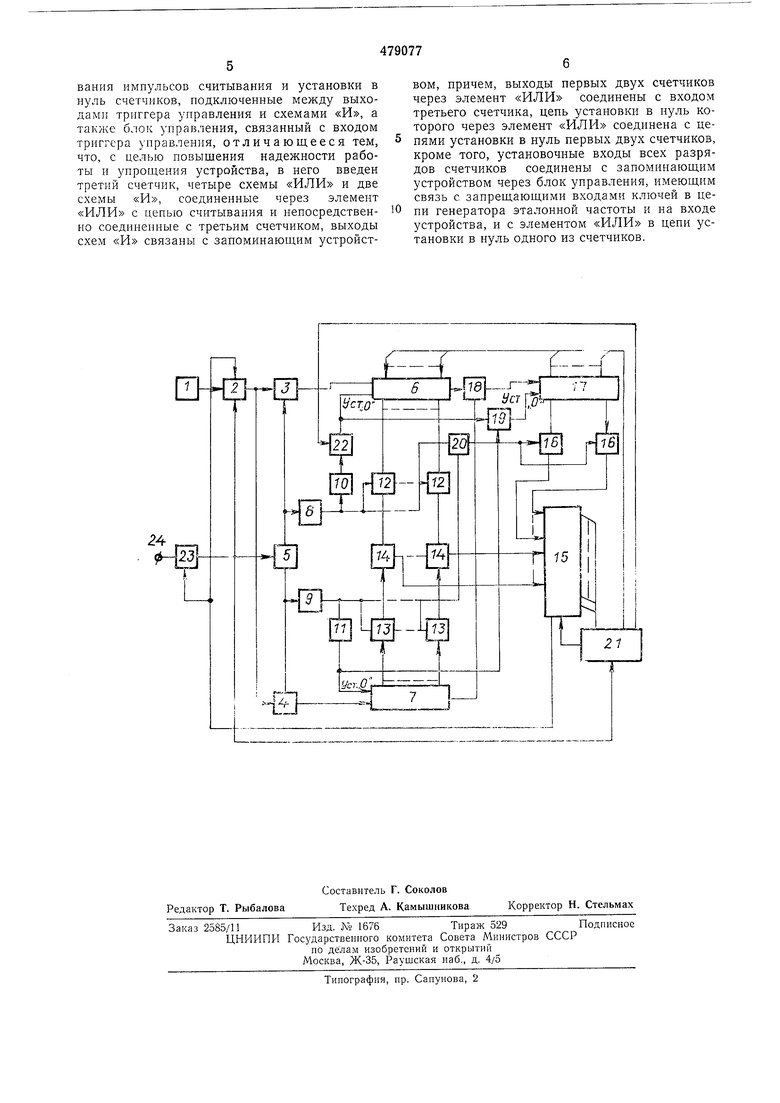

На чертеже показана блок-схема устройства для измерения серии временных интервалов.

Устройство содержит генератор 1 импульсов эталонной частоты соединенный с ним ключ 2, схемы «И 3 и 4, соединенные с выходами триггера 5 управления и включенные между выходом ключа 2 и входами счетчиков 6 и 7 младших разрядов, цепи формирования импульсов считывания и установки в нуль счетчиков, образованные формирователями 8 и 9 импульсов, соединенными с выходами триггера 5 управления н подключенными к схемам 10 и 11 задержки, схемы «И 12 и 13 и «ИЛИ 14, включенные между выходами счетчиков младщих разрядов и входами младших разрядов запоминающего устройства 15, входы старщих разрядов которого через другие схемы «И 16 связаны с выходами счетчика 17 старшнх разрядов, вход которого через схему «ИЛИ 18 соединен с выходами счетчиков младщих разрядов, а его цень установки в нуль связана через схему «ИЛИ 19 с цепями установки в нуль счетчиков младших разрядов, схему «ИЛИ 20, связывающую выходы формирователей импульсов 8 и 9, соединениых с входами схем «И 12 и 13 и схемами «И 16, блок 21 уиравлеиия, подключенный к входу запоминающего устройства и связывающий кодовые выходы запоминающего устройства с установочными входами счетчика, образованного счетчиками 6 и 7 младших и старших разрядов, а также через схему «ИЛИ 22, связанный с цепями установки в нуль этих счетчиков, ключ 23, связывающий вход устройства 24 с входом триггера управления и соединенный с выходом переполнения запоминающего устройства. Кроме того, выход ключа 23 соединен с блоком управления и разрешающим входом ключа 2, запрещающий вход которого соединен с запрещающим входом ключа 23.

Устройство работает следующим образом. В исходном состоянии ключ 2 закрыт, а ключ 23 открыт, счетчики 6, 7 и 17 установлены в нуль, а запоминающее устройство подготовлено к приему кодов из счетчиков, причем кодовые выходы запоминающего устройства с помощью блока управления отключены от установочных входов счетчиков 6 и 17 младших и старших разрядов.

Первый импульс измеряемой серии временных интервалов с входа устройства 24, пройдя через открытый ключ 23, устанавливает триггер о управления в одно из состояний и открывает ключ 2. С этого момента времени начинается счет импульсов эталонной частоты, которые подаются на вход счетчика 6 младших разрядов, если разрешающий потенциал от триггера 5 управления подан на схему «И 3, или на вход счетчика 7, если триггер уиравления установлен в противоположное состояние.

После переполнения счетчика младщих разрядов, импульсы с его выхода через схему «ИЛИ 18 подаются на счетчик 17 старших разрядов. Второй импульс измеряемой серии, соответствующий концу первого и началу второго временного интервала, переключает триггер уиравления, в результате чего начинается счет импульсов эталонной частоты другим счетчиком младших разрядов, и из перепада напряжения на соответствующем выходе триггера управления формирователем импульсов 8 или 9 формируется импульс считывания. Этот импульс подается на схемы «И 12 или «И 13 и через схему «ИЛИ 20 на схемы «И 16, в результате чего производится считывание кодов из счетчика младших разрядов, в котором счет к моменту формирования импульса считывания был прекращен, а также из счетчика старших разрядов. Кроме того, второй импульс измеряемой серии временных интервалов через блок 21 управления подается на запоминающее устройство 15, разрешая запись кода первого измеренного временного интервала.

По окончании считывания из счетчиков младщего и старшего разрядов сформированный формирователем В или 9 импульс после задержки схемой 10 или И на время записи в запоминающем устройстве подается в цепь устаповки в нуль счетчика младших разрядов 5 и через схему «ИЛИ 19 в цепь установки в нуль счетчика старших разрядов.

К моменту окончания записи кода в запоминающее устройство одии из счетчиков младШ.ИХ разрядов и счетчик старших разрядов

10 оказываются установленными в нуль, а в другом счетчике младших разрядов все это время идет счет импульсов эталонной частоты. При этом число импульсов эталонной частоты, иоступивших к этому моменту времени в счетчик младших разрядов, не должно превышать величину его емкости.

Измерение всех последующих временных интервалов серии происходит как описано выше.

0 Еслн количество измеряемых интервалов превышает емкость запоминающего устройства, с его выхода снимается импульс переполнения, который закрывает ключи 2 и 23, прекращая измерение всех последующих временных интервалов, благодаря чему исключается возможность повторной записи кодов в уже запятые.ячейки памяти.

Это особенно важно, когда за измеряемой серией временных интервалов следует серия

0 импульсных помех, которые, действуя на входе, приводят к переполнению запоминающего устройства и в случае отсутствия ключа 23 и при циклической работе запоминающего устройства - к стираиию записанной ранее ин5 формации.

Считывание информации из запоминающего устройства происходит следующим образом.

По команде из блока 21 управления снимаются три задержанных импульса. Первый импульс через схему «ИЛИ 22 подается в цепь установки в нуль счетчика 6 младщих разрядов и далее через схему «ИЛИ 19 в цепь установки в нуль счетчика 17 старших разрядов. Следующий за ним импульс устанавливает запоминающее устройство в начальное состояние. Третий управляющий импульс производит считывапие первого измеренного интервала, код которого из запоминающего устройства через блок управления подается на

0 установочные входы счетчиков 6 и 17.

Код из счетчиков 6 и 17 выводится на цифропечать или на индикаторные устройства, после чего осуществляется считывание из запоминающего устройства кода следующего

5 временного интервала.

Предмет изобретения

Устройство для измерения серии временных интервалов, содержащее последовательно

0 соединенные генератор импульсов эталонной частоты и ключ, две схемы «ИЛИ, связанные с двумя счетчиками, выходом ключа и выходами триггера управления, запоминающее устройство, соединенное через схемы «И и

5 «ИЛИ с выходами счетчиков, цепи формирования импульсов считывания и установки в нуль счетчиков, подключенные между выходами триггера управления и схемами «И, а также блок управления, связанный с входом триггера управления, отличающееся тем, что, с целью повышения надежности работы и упрощения устройства, в него введен третий счетчик, четыре схемы «ИЛИ и две схемы «И, соединенные через элемент «ИЛИ с цепью считывания и непосредственно соединенные с третьим счетчиком, выходы схем «И связаны с запоминающим устройством, причем, выходы первых двух счетчиков через элемент «ИЛИ соединены с входом третьего счетчика, цепь установки в нуль которого через элемент «ИЛИ соединена с цепями установки в нуль первых двух счетчиков, кроме того, установочные входы всех разрядов счетчиков соединены с запоминающим устройством через блок управления, имеющим связь с запрещающими входами ключей в цепи генератора эталонной частоты и на входе устройства, и с элементом «ИЛИ в цепи установки в нуль одного из счетчиков.

| название | год | авторы | номер документа |

|---|---|---|---|

| Измеритель временных интервалов | 1979 |

|

SU809037A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ВРЕМЕННОГО ИНТЕРВАЛА | 1991 |

|

RU2040854C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1992 |

|

RU2038694C1 |

| Устройство для измерения длительности переходного процесса | 1973 |

|

SU479246A1 |

| ТАЙМЕР С КОНТРОЛЕМ | 1991 |

|

SU1832976A1 |

| УСТРОЙСТВО ДЛЯ АВТОМАТИЧЕСКОГО ДИСКРЕТНОГО РЕГУЛИРОВАНИЯ КОЭФФИЦИЕНТА ПЕРЕДАЧИ | 1971 |

|

SU292215A1 |

| Устройство для измерения серии временных интервалов | 1977 |

|

SU690434A1 |

| ЦИФРОВОЙ ИЗМЕРИТЕЛЬ СЕРИИ ВРЕМЕННЫХ ИНТЕРВАЛОВ | 1968 |

|

SU208038A1 |

| Устройство для регулирования расходажидКОСТи | 1979 |

|

SU842728A1 |

| Измерительный двухфазный генератор | 1987 |

|

SU1442931A1 |

Авторы

Даты

1975-07-30—Публикация

1973-01-18—Подача