Изобретение относится к импульсной технике, в частности к аналого-цифровым преобразователям (АЦП) с промежуточным преобразованием напряжения в частоту импульсов и может быть использовано в устройствах сбора аналоговой информации систем контроля и управления технологическими процессами. Известны АЦП, в которых промежуточное преобразование выполняется с помощью преобразователя напряжения в частоту ПНЧ с компенсацией заряда интегрирующего конденсатора [1] В них ПНЧ имеет интегратор с операционным усилителем, конденсатором и резисторами для преобразования преобразуемого и встроенного эталонного напряжений. Из последнего формируется эталонный заряд q, который компенсируется до нуля зарядом от тока Ux/R с частотой повторения Fx= Ux/qR. За фиксированный интервал времени Тo, получается результат преобразования x ToFx UxTo/qR.

Эти АЦП имеют недостаток, обусловленный влиянием нестабильности q и R на результат преобразования.

Среди этих АЦП лучшими характеристиками обладают преобразователи, в которых изменение q и R не влияет на х благодаря выполняемой коррекции результата преобразования. Например, в АЦП по авт. св. СССР N 1504789, Б.И. N 32, 1989 выполняется цифровая коррекция результата преобразования, а в АЦП по авт.св. СССР N 1654976, Б.И. N 21, 1991 эта коррекция выполняется с меньшим квантом и устраняются дополнительные погрешности при выполнении временного квантования, но это требует дополнительных затрат времени по сравнению с То.

Наиболее близким к изобретению является АЦП с более высокими характеристиками [2] в котором дополнительные затраты времени по сравнению с То, имеющие место в упомянутых АЦП, исключаются. Такой АЦП имеет преимущество при использовании благодаря простоте его синхронизации и временной привязке результатов преобразования к внешним сигналам.

Поэтому этот АЦП принят в качестве прототипа. Он содержит преобразователь напряжения в частоту импульсов, выход которого соединен с первыми входами первого, второго и третьего элементов И и первого элемента ИЛИ, первый вход является шиной нулевого потенциала и объединен с первым входом преобразователя напряжения в ток и с первым информационным входом первого переключателя, второй вход через токоограничивающий элемент объединен с первым информационным входом второго переключателя, а третий вход соединен с выходом третьего переключателя, первый информационный вход которого объединен с вторым входом преобразователя напряжения в ток и является первой входной информационной шиной, второй информационный вход второй информационной шиной, а вход управления подключен к "1" выходу первого триггера, входы управления первого и второго переключателей объединены, их выходы объединены через накапливающий элемент, а вторые информационные входы объединены с входом ключа и соединены с выходом последнего, вход установки исходного состояния первого триггера объединен с одноименными входами второго триггера и первого счетчика и через первый одновибратор подключен к шине синхронизации, "0" выход первого триггера соединен с первым входом четвертого элемента, а "0" вход объединен с вторым входом третьего элемента И, выход которого через второй одновибратор подключен к второму и первому входам соответственно первого и второго элементов ИЛИ, выходы которых соединены с первым и вторым входами соответственно пятого и второго элементов И, выход последнего из которых подключен к входу синхронизации генератора импульсов, к входу установки исходного состояния второго счетчика и к "1" входу второго триггера, "1" выход которого соединен с первым и вторым входами соответственно шестого и первого элементов И, "0" вход с выходом последнего и объединен с первым входом третьего элемента ИЛИ, "0" выход с вторым входом четвертого элемента И, третий вход которого подключен к выходу среднего разряда первого счетчика и через третий одновибратор объединен с входом синхронизации распределителя импульсов, а выход подключен к первому счетному входу среднего разряда третьего счетчика, первый счетный вход старшего разряда которого соединен с выходом пятого элемента И, счетные входы младших разрядов с выходами элементов И первой группы, а выходы средних и старших разрядов с соответствующими информационными входами регистра, выходы разрядов которого являются выходной шиной, а вход записи кода подключен к выходу первого формирователя импульсов и объединен с входом второго формирователя импульсов, выход генератора импульсов соединен с счетным входом первого счетчика и с вторым входом шестого элемента И, выход которого подключен к счетному входу второго счетчика, первые входы элементов И первой группы соединены с выходами младших разрядов распределителя импульсов, первые входы седьмого и восьмого элементов И объединены, выход четвертого одновибратора соединен с первым входом девятого элемента И, выход которого является шиной готовности результата преобразования, при этом вход и выход ключа подсоединены соответственно к второй входной шине и к выходу преобразователя напряжения в ток, управляющие входы ключа и первого переключателя соединены соответственно с выходами седьмого и восьмого элементов И, вторые входы которых подсоединены соответственно к "0" выходу первого триггера и второму входу второго элемента ИЛИ и к "1" выходу первого триггера и второму входу третьего элемента ИЛИ, выход которого соединен с вторым входом пятого элемента И, выход которого подсоединен к входу распределителя импульсов, первый вход седьмого элемента И объединен с "0" выходом первого одновибратора, "1" вход первого триггера объединен с "0" входом второго триггера, "1" выход которого соединен с вторым и третьим входами соответственно девятого элемента И и первого элемента ИЛИ, вход установки исходного состояния с входом четвертого одновибратора, а "0" выход с входом первого формирователя импульсов, выход второго формирователя импульсов подсоединен к входу установки исходного состояния третьего счетчика, вход включения режима вычитания которого соединен с выходом четвертого элемента И, вторые входы элементов И первой группы подсоединены к соответствующим выходам второго счетчика, а выход переполнения первого счетчика соединен с "0" входом первого триггера.

В этом АЦП в начале То преобразуется опорное напряжение Uo в частоту Fq, период tq которой измеряется. Отличие полученной величины от номинальной, полученной в виде кода n, используется для коррекции результата преобразования в процессе подсчета импульсов Fx ПНЧ.

В этом АЦП выполняются также две дополнительные коррекции зарядов, которые участвуют в формировании Fx в начале То за время tk до появления первого импульса Fx и далее за время tq при формировании кода n, когда ПНЧ преобразует напряжение Uo. Необходимые для выполнения этих коррекций замеры совмещаются с процессом измерения Ux. При этом информация о величине Ux в течение этого времени не теряется и формируется соответствующий заряд, который участвует при получении окончательного результата преобразования. Благодаря этому результаты преобразования соответствуют средним значениям  (To) за временные интервалы То, между которыми отсутствуют временные промежутки, что повышает быстродействие АЦП.

(To) за временные интервалы То, между которыми отсутствуют временные промежутки, что повышает быстродействие АЦП.

Эти свойства прототипа использованы в предлагаемом АЦП.

Однако в этом АЦП время квантования Uх и получение  (To) определяется временным интервалом То, который равен или кратен периоду помехи, наложенной на Ux, и получение результатов за меньшее время недопустимо. Поэтому стоит задача сокращения времени между получением отдельных результатов преобразования Ux, т. е. увеличения частоты квантования преобразуемого сигнала с сохранением времени его интегрирования в течение То для обеспечения подавления помехи.

(To) определяется временным интервалом То, который равен или кратен периоду помехи, наложенной на Ux, и получение результатов за меньшее время недопустимо. Поэтому стоит задача сокращения времени между получением отдельных результатов преобразования Ux, т. е. увеличения частоты квантования преобразуемого сигнала с сохранением времени его интегрирования в течение То для обеспечения подавления помехи.

С целью решения этой задачи предложен АЦП, реализация которого позволит повысить быстродействие АЦП.

Для этого в аналого-цифровой преобразователь, содержащий преобразователь напряжения в частоту импульсов, выход которого соединен с первыми входами первого, второго и третьего элементов И и первого элемента ИЛИ, первый вход является шиной нулевого потенциала и объединен с первым входом преобразователя напряжения в ток и с первым информационным входом первого переключателя, второй вход через токоограничивающий элемент объединен с первым информационным входом второго переключателя, а третий вход соединен с выходом третьего переключателя, первый информационный вход которого объединен с вторым входом преобразователя напряжения в ток и является первой входной информационной шиной, второй информационный вход второй входной информационной шиной, а вход управления подключен к "1" выходу первого триггера, входы управления первого и второго переключателей объединены, их выходы объединены через накапливающий элемент, а вторые информационные входы объединены с входом ключа и соединены с выходом последнего, вход установки исходного состояния первого триггера объединен с одноименными входами второго триггера и первого счетчика и через первый одновибратор подключен к шине синхронизации, "0" выход первого триггера соединен с первым входом четвертого элемента И, а "0" вход объединен с вторым входом третьего элемента И, выход которого через второй одновибратор подключен к второму и первому входам соответственно первого и второго элементов ИЛИ, выходы которых соединены с первым и вторым входами соответственно пятого и второго элементов И, выход последнего из которых подключен к входу синхронизации генератора импульсов, к входу установки исходного состояния второго счетчика и к "1" входу второго триггера, "1" выход которого соединен с первым и вторым входами соответственно шестого и первого элементов И, "0" вход с выходом последнего и объединен с первым входом третьего элемента ИЛИ, "0" выход с вторым входом четвертого элемента И, третий вход которого подключен к выходу среднего разряда первого счетчика и через третий одновибратор объединен с входом синхронизации распределителя импульсов, а выход подключен к первому счетному входу среднего разряда третьего счетчика, первый счетный вход старшего разряда которого соединен с выходом пятого элемента И, счетные входы младших разрядов с выходами элементов И первой группы, а выходы средних и старших разрядов -- с соответствующими информационными входами регистра, выходы разрядов которого являются выходной шиной, а вход записи кода подключен к выходу первого формирователя импульсов и объединен с входом второго формирователя импульсов, выход генератора импульсов соединен с счетным входом первого счетчика и с вторым входом шестого элемента И, выход которого подключен к счетному входу второго счетчика, первые входы элементов И первой группы соединены с выходами младших разрядов распределителя импульсов, первые входы седьмого и восьмого элементов И объединены, выход четвертого одновибратора соединен с первым входом девятого элемента И, выход которого является шиной готовности результата преобразования, введены блок запоминания кодов, четвертый и пятый счетчики, коммутатор кодов, третий и четвертый триггеры, четвертый, пятый и шестой элементы ИЛИ, десятый элемент И, вторая и третья группы элементов И, первые входы которых соединены соответственно с выходами средних и старших разрядов распределителя импульсов, вторые входы элементов И всех трех групп подсоединены к соответствующим выходам коммутатора кодов, выходы элементов И второй группы соединены соответственно с вторым счетным входом первого среднего разряда и с счетными входами остальных средних разрядов третьего счетчика, а выходы элементов И третьей группы соединены соответственно с вторым счетным входом первого старшего разряда и с счетными входами остальных старших разрядов третьего счетчика, первый счетный вход старшего разряда которого соединен с первым входом четвертого элемента ИЛИ, а счетные входы всех разрядов третьего счетчика объединены с одноименными счетными входами разрядов четвертого счетчика, выходы разрядов которого подключены к соответствующим информационным входам блока запоминания кодов, а вход включения режима вычитания подключен к выходу четвертого элемента И и объединен с первым входом пятого элемента ИЛИ, выход которого соединен с входом включения режима вычитания третьего счетчика, а второй вход соединен с выходом четвертого одновибратора и объединен с входом установки исходного состояния четвертого счетчика, с входом управления коммутатора кодов, входом управления считыванием блока запоминания кодов и "1" входом третьего триггера, "0" выход которого подключен к второму входу второго элемента ИЛИ, вход установки исходного состояния объединен с одноименными входами четвертого триггера, первого, третьего и пятого счетчиков и входом управления ключа, а "1" выход к первым входам шестого элемента ИЛИ и десятого элемента И, второй вход которого соединен с выходом первого элемента ИЛИ, третий вход объединен с одноименным входом первого элемента И и с входом первого формирователя импульсов и соединен с "0" выходом первого триггера, а выход с вторым входом третьего элемента ИЛИ, выход которого подключен к "1" входу первого триггера, "1" выход которого соединен с входом управления первого переключателя, второй информационный вход которого подключен к выходу преобразователя напряжения в ток, вторые информационные входы второго и третьего переключателей объединены, четвертый вход четвертого элемента И объединен с вторыми входами пятого и седьмого элементов И и соединен с выходом шестого элемента ИЛИ, второй вход которого объединен с вторыми входами восьмого и девятого элементов И и подключен к "1" выходу четвертого триггера, "1" вход которого соединен с выходом первого старшего разряда первого счетчика, выход второго старшего разряда и выход переполнения средних разрядов которого подключен к "0" входам соответственно третьего и первого триггеров, выход второго формирователя импульсов подключен к входу четвертого одновибратора и к первому входу восьмого элемента И, выход которого соединен с вторым входом четвертого элемента ИЛИ, выход которого подключен к управляющему входу распределителя импульсов, третьи входы второго и пятого элементов И объединены и подключены к "0" выходу второго триггера, выход первого формирователя импульсов соединен с входом записи блока запоминания кодов, адресные входы которого подключены к выходам разрядов пятого счетчика, счетный вход которого соединен с выходом седьмого элемента И, а первые и вторые входы коммутатора кодов подключены соответственно к выходам разрядов второго счетчика и блока запоминания кодов.

В результате поисков среди известных АЦП не обнаружены технические решения, которые содержат признаки, сходные с отличительными признаками предлагаемого решения.

В данном изобретении технический эффект повышения быстродействия достигается благодаря тому, что результаты преобразования формируются в последовательно выполняемых тактах работы АЦП с длительностью каждого из них, равной tiTo/p.

При этом одноименные такты ti повторяются через временные интервалы То, равные периоду помехи, наложенной на преобразуемое напряжение.

В каждом текущем такте tiт формируются, во-первых, текущий промежуточный результат Niт, соответствующий среднему значению  (tiт) за этот временной интервал, и, во-вторых, текущий результат преобразования хт, полученный в результате суммирования р предыдущих промежуточных результатов Nin и поэтому соответствующий среднему значению

(tiт) за этот временной интервал, и, во-вторых, текущий результат преобразования хт, полученный в результате суммирования р предыдущих промежуточных результатов Nin и поэтому соответствующий среднему значению  (Tn) за прошедший интервал времени Tn, равный То.

(Tn) за прошедший интервал времени Tn, равный То.

Промежуточный результат Niт используется для получения хт и запоминается на время То до следующего одноименного такта ti, в котором он будет использован в качестве предыдущего результата Nin, полученного в ti-1 такте, путем его увеличения на Niт и уменьшения на Nin. Благодаря этому текущие значения хт, соответствующие  (Tn) и не содержащие погрешностей от наложенной помехи на преобразуемый сигнал, формируются через временные интервалы ti, которые в р раз меньше времени преобразования прототипа.

(Tn) и не содержащие погрешностей от наложенной помехи на преобразуемый сигнал, формируются через временные интервалы ti, которые в р раз меньше времени преобразования прототипа.

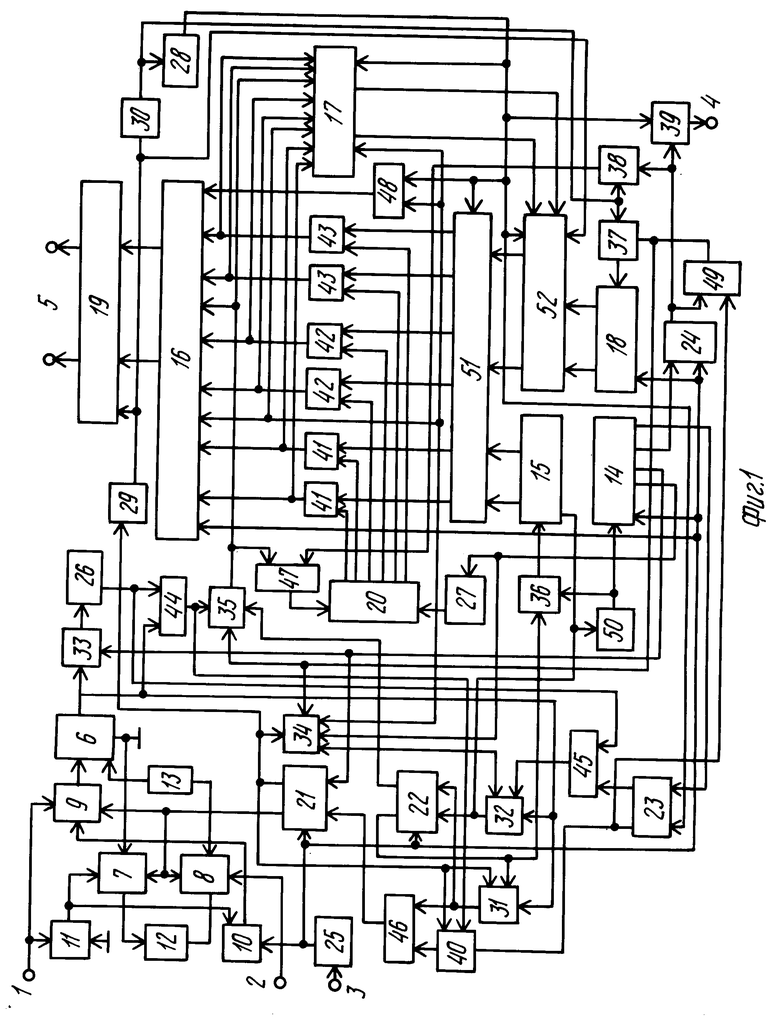

На фиг. 1 приведена блок-схема предлагаемого АЦП; на фиг.2 временная диаграмма его работы.

АЦП содержит входные информационные шины 1 и 2 преобразуемого Ux и опорного Uo напряжений, шины 3 и 4 синхронизации и готовности результата преобразования, выходную шину 5 результата преобразования, преобразователь 6 напряжения в частоту импульсов, с первого по третий переключатели 7-9, у которых при наличии сигнала на управляющем входе первый информационный вход соединен с выходом и при его отсутствии второй вход соединен с выходом, ключ 10, у которого вход соединен с выходом при отсутствии сигнала на управляющем входе, преобразователь 11 напряжения в ток, накапливающий элемент 12, например конденсатор, токоограничивающий элемент 13, например резистр, с первого по пятый счетчики 14-18, каждый из которых имеет вход установки в исходное состояние и счетный вход младшего разряда, а счетчики 16 и 17 имеют счетные входы во всех остальных разрядах, причем первые средний и старший разряды имеют по два счетных входа, кроме этого в каждом из этих двух счетчиков имеется вход включения режима вычитания, при наличии сигнала на котором в счетчике выполняется вычитание поступающих на счетные входы импульсов, регистр 19, распределитель 20 импульсов, имеющий два входа: вход управления, предназначенный для его запуска по импульсу, после прихода которого на выходах последовательно во времени будут возникать импульсы, и вход синхронизации его работы, по импульсу на котором обеспечивается временной сдвиг всех выходных импульсов распределителя, с первого по четвертый триггеры 21-24, с первого по четвертый одновибраторы 25-28, первый и второй формирователи 29 и 30 импульсов, с первого по десятый элементы И 31-40, с первой по третью группы элементов И 41-43, с первого по шестой элементы ИЛИ 44-49, генератор 50 импульсов, имеющий вход синхронизации, коммутатор 51 кодов и блок 52 запоминания кодов.

На фиг.2 показаны импульс 53 одновибратора 25, сигналы 54-57 на "1" выходах триггеров 21-24, импульсы 58 ПНЧ 6, напряжения 59 и 60 на выходе переключателя 7 и заряд элемента 12, импульсы 61-63 на выходах элементов И 32, 31 и 40, импульсы 64 формирователя 29, импульсы 65-67 на выходах элементов И 37, 38 и 35, временные интервалы 68 работы распределителя 20 импульсов, импульсы 69 и 70 одновибратора 28 и шины 4, импульсы 71-73 переполнения средних разрядов, сигналы первого и второго старших разрядов счетчика 14 и адресный сигнал 74 на входе блока 52.

В АЦП шина 1 соединена с вторым входом преобразователя 11 и первым информационным входом переключателя 9, шина 2 с вторым информационным входом последнего, с одноименным входом переключателя 8 и выходом ключа 10, шина 3 с входом одновибратора 25, шина 4 с выходом элемента И 39, шина 5 с выходами разрядов регистра 19, входы разрядов которого соединены с выходами средних и старших разрядов счетчика 16, а вход записи кода с выходом и входом соответственно формирователей 29 и 30, входом записи кодов блока 52, информационные и адресные входы которого соединены с выходами разрядов соответственно счетчиков 17 и 18, вход считывания с "1" входом триггера 24, первым входом элемента И 39, вторым входом элемента ИЛИ 48, входом установки исходного состояния счетчика 17, выходом одновибратора 28 и управляющим входом коммутатора 51, а выходы с вторыми входами последнего, первые входы которого соединены с выходами разрядов счетчика 15, а выходы с вторыми входами элементов И 41-43, первые входы которых соединены с выходами разрядов распределителя 20, выходы элементов И 41 соединены с соответствующими входами младших разрядов счетчика 16, выходы элементов И 42 соответственно с вторым счетным входом первого среднего разряда и счетными входами остальных средних разрядов счетчика 16, выходы элементов И 43 соответственно с вторым счетным входом первого старшего разряда и счетными входами остальных старших разрядов счетчика 16, первый счетный вход первого старшего разряда которого соединен с выходом элемента И 35 и с первым входом элемента ИЛИ 47, первый счетный вход первого среднего разряда с выходом элемента И 34, первым входом элемента ИЛИ 48 и входом включения режима вычитания счетчика 17, а счетные входы всех разрядов последнего объединены с одноименными счетными входами разрядов счетчика 16, вход включения вычитания которого соединен с выходом элемента ИЛИ 48, выход формирователя 30 соединен с входом одновибратора 28 и первыми входами элементов И 38 и 37, выход первого из которых соединен с вторым входом элемента ИЛИ 47, а выход второго с счетным входом счетчика 18, вход установки исходного состояния которого соединен с одноименными входами счетчиков 14 и 16, триггеров 21-24, с выходом одновибратора 25 и входом управления ключа 10, вход которого соединен с выходом преобразователя 11 и вторым информационным входом переключателя 7, первый информационный вход которого соединен с первыми входами преобразователей 6 и 11 и общей шиной, вход через элемент 12 с входом переключателя 8, а управляющий вход с одноименными входами переключателей 8 и 9 и "1" выходом триггера 21, "0" выход которого соединен с входом формирователя 29, первым и третьими входами соответственно элементов И 34 и 31, 40, "1" вход с выходом элемента ИЛИ 46, а "0" вход с вторым входом элемента И 33 и выходом переполнения средних разрядов счетчика 14, выход среднего разряда которого соединен с третьим входом элемента И 34 и через одновибратор 27 с входом синхронизации распределителя 20, выходы первого и второго старших разрядов с "1" и "0" входами соответственно триггеров 24 и 23, а счетный вход с выходом генератора 50 и с вторым входом элемента И 36, выход которого соединен со счетным входом счетчика 15, вход установки исходного состояния которого соединен с входом синхронизации генератора 50, выходом элемента И 32 и "1" входом триггера 22, "0" вход которого соединен с выходом элемента И 31 и первым входом элемента ИЛИ 46, "1" выход с первым и вторым входами соответственно элементов И 36 и 31, "0" выход с вторым и третьими входами соответственно элементов И 34 и 35, 32, второй вход последнего соединен с выходом элемента ИЛИ 45, первый вход которого соединен с вторым входом элемента ИЛИ 44 и через одновибратор 26 с выходом элемента И 33, первый вход которого соединен с первыми входами элементов И 31; 32, ИЛИ 44 и выходом преобразователя 6, второй вход которого через элемент 13 соединен с первым информационным входом переключателя 8, третий вход с выходом переключателя 9, второй вход элемента ИЛИ 45 соединен с "0" выходом триггера 23, "1" выход которого соединен с первыми входами элементов ИЛИ 49 и И 40, выход которого соединен с вторым входом элемента ИЛИ 46, а второй вход с выходом и входом соответственно элементов ИЛИ 44 и И 35, второй вход которого соединен с четвертым и вторым входами соответственно элементов И 34 и 37 и выходом элемента ИЛИ 49, второй вход которого соединен с одноименными входами элементов И 38 и 39 и с "1" выходом триггера 24, а выход элементов ИЛИ 47 соединен с входом распределителя 20.

АЦП работает следующим образом.

Как и в прототипе, время измерения входного напряжения Ux(t) равно То, величина которого кратна периоду помехи и формируется с помощью счетчика 14 по импульсам частоты f генератора 50. В АЦП сохранены соотношения между параметрами прототипа To No/Fq, где Fq максимальная частота ПНЧ 6 при преобразовании опорного напряжения в результате компенсации его внутреннего эталонного заряда q током Uo/R за время tq 1/Fq, a q  tq. Время To No2not, где t 1/f временной квант работы АЦП. Частота f NonoFq. Квант АЦП по напряжению равен Δp Uo/Nono.

tq. Время To No2not, где t 1/f временной квант работы АЦП. Частота f NonoFq. Квант АЦП по напряжению равен Δp Uo/Nono.

В отличие от прототипа изменены: величина временного интервала Тн, через который определяется значение q и формируется величина n, величина временного кванта tcp при формировании кода η при оценке величины qk и величина длительности тактов ti работы АЦП.

Величина Тн составляет несколько периодов То и формируется по сигналам 73 в результате подсчета импульсов 72 длительностью То старшими разрядами счетчика 14. Выбор Тн определяется у словием обеспечения допустимого изменения q за Тн от температурного и временного дрейфа параметров ПНЧ.

Величина tcp задается сигналом среднего разряда счетчика 14 и по сравнению с прототипом она должна быть уменьшена в р раз, как будет показано ниже. Длительность такта работы АЦП равна ti To/p и задается импульсами 71 переполнения средних разрядов счетчика 14, пересчет которых первыми старшими разрядами дает сигналы 72, имеющие длительность То. За каждый текущий такт tiт формируется промежуточный результат преобразования Niт, а их суммирование за прошедшие р тактов дает текущий результат преобразования хт за время измерения То. На фиг.2 для упрощения в качестве примера приведены соотношения Тн 2То и ti 0,5To.

Каждый такт ti начинается по импульсу 71 в результате пересчета импульсов генератора 50, т.е. смена тактов происходит через время ti Импульс 71 устанавливает в "0" триггер 21, в это состояние он устанавливается также сигналом 53 одновибратора 25, который запускается импульсом по шине 3, поступающим после включения питания АЦП или при необходимости временной привязки результатов преобразования к сигналам внешней синхронизации.

Импульс 71 устанавливает в "0" триггер 21, в это состояние он устанавливается также сигналом 53 одновибратора 25, который запускается импульсом по шине 3, поступающим после включения питания АЦП или при необходимости временной привязки результатов преобразования к сигналам внешней синхронизации.

Сигнал 53 устанавливает в "0" состояние триггеры 21-24 и счетчики 14, 16 и 18 и замыкает ключ 10. Отсутствие сигнала 54 на "1" выходе триггера 21 обеспечивает с помощью переключателей 7-9 включение конденсатора 21 между входом и выходом ключа 10 и подключение напряжения Uo к третьему входу ПНЧ 6. Конденсатор 12 разряжается и на его обкладных устанавливается напряжение 59, равное Uo, а ПНЧ 6 преобразует это же напряжение в импульсы 58.

По окончании импульса 53 ключ 10 размыкается и в конденсаторе 12 начинает накапливаться заряд 60 qx Int от тока преобразователя 11, равного In и напряжение 59 начинает уменьшаться.

и напряжение 59 начинает уменьшаться.

Для тактов ti работы АЦП, выполняемых после импульса 53 или сигнала 73, и в которых определяются величины q и n, первый импульс 58, появляющийcя через время t1, проходит через элемент И 32, работа которого разрешена сигналами с "0" выходов триггеров 23 и 28, и его выходной импульс 61 установит последний в "1", счетчик 15 в "0" и синхронизирует начало формирования в генераторе 50 импульсов f, которые с возникновением сигнала 55 проходят через элемент И 36 на счетный вход счетчика 15. Сигнал 55 будет действовать в течение времени tq до появления второго импульса 58, который проходит через элемент И 31, а его импульс 62 установит в "0" триггер 22 и в "1" триггер 21. После снятия сигнала с "0" выхода последнего последовательно запускаются формирователи 29 и 30 и одновибратор 28, сигнал 69 которого устанавливает в "1" триггер 23 и в исходное состояние счетчик 17. За время tq в ПНЧ 6 заряд q скомпенсирован до нуля током Uo/R, т.е. q  tq и в счетчике 15 будет получен код nq tq ˙f.

tq и в счетчике 15 будет получен код nq tq ˙f.

При номинальном значении q qo длительность tq будет равна to Nonot, которой соответствует код tof Nono. Изменение q приводит к величинам tq to+tn-(Nono+n)t,

nq Nono+ n и q  (Nono+n)t.

(Nono+n)t.

В дальнейшем при коррекции результата преобразования будет использована величина n, поэтому число разрядов счетчика 15 выбирается с учетом ее максимального значения и наличие старших разрядов, в которых находилась бы величина Nono, не требуется.

Если такт tiт начинался в момент времени Т, то за время tн t1+tq в конденсаторе 12 накопится заряд 60, равный

qc=

Ux(t)dt.

Ux(t)dt.

Для всех других тактов ti работы АЦП, кроме двух рассмотренных, первый импульс 58, появляющийся через время t1 после начала такта, проходит через элементы ИЛИ 44 и И 40, работа которого разрешена сигналами 56, и с "0" выхода триггера 21, а далее импульсы 63 проходят через элемент ИЛИ 46 и устанавливает в "1" триггер 21. Поэтому его сигнал 54 появляется сразу после t1 и величины tн для этих тактов tiравна t1.

Во всех тактах ti работы АЦП с появлением сигнала 54 к третьему входу ПНЧ 6 вместо напряжения Uo подключается Ux(t), а к его второму входу с помощью переключателей 7 и 8 через резистор 13 напряжение, накопленное в конденсаторе 12, вторая обкладка которого подключается к общей шине.

Как и в прототипе ПНЧ 6 может быть выполнен по схеме, использующей компенсацию заряда интегрирующего конденсатора и реализуемой на основе интегратора, имеющего операционный усилитель с конденсатором в цепи обратной связи и с входным резистором величиной R.

С помощью последнего входные напряжения Ux(t) или Uo преобразуются в ток, а вход операционного усилителя служит вторым входом ПНЧ.

В течение сигнала 54 заряды q ПНЧ 6 компенсируются суммарным током от Ux(t) и от конденсатора 12. Для полной передачи заряда qc последнего в конденсатор ПНЧ 6 за время ti параметры конденсатора 12 и резистора 13 выбираются из условия обеспечения постоянной времени цепи разряда, значительно меньшей времени ti. После разряда конденсатора 12 ПНЧ 6 будет выполнять преобразование только напряжения Ux(t) в импульсы 58.

За время действия сигнала 54 на выходе ПНЧ 6 будет сформировано Niимпульсов 58, которые проходят через элементы ИЛИ 44 и И 35, а с выхода последнего импульсы 67 подаются на первые счетные входы первых старших разрядов счетчиков 16 и 17, имеющих вес Nono, и в этих старших разрядах формируется код NiNono. Каждый импульс 67 проходит также через элемент ИЛИ 47 и запускает распределитель 20 импульсов. На его выходах последовательно во времени будут возникать импульсы, которые проходят через элементы И 41, имеющие на вторых входах "1" сигналы с выходов разрядов коммутатора 51, обеспечивающего подключение кода n с выходов счетчика 15. Импульсы с выходов элементов И 41 поступают на счетные входы младших разрядов счетчиков 16 и 17, благодаря этому в течение временных интервалов 68 выполняется поразрядное суммирование кода n с кодом этих счетчиков. Поэтому сформированные ПНЧ 6 Ni импульсов образуют в счетчиках 16 и 17 коды, имеющие значения Ni(Nono+n).

Как и в прототипе, при формировании этих кодов для исключения сбоев, которые могут возникнуть в двух случаях (когда окончание ti и сигнала 54 совпадает с импульсом 58 или происходит в течение временного интервала 68), в АЦП предусмотрены специальные средства. Для первого случая с помощью одновибратора 26, элементов И 33 и ИЛИ 44 обеспечивается расширение импульса 58 на выходе последнего и таким образом такт ti заканчивается без сбоев. Во втором случае с помощью импульсов одновибратора 27 синхронизируется работа распределителя 20, что обеспечивает временной сдвиг импульсов с выхода элементов И 41-43 и импульса 67 на счетных входах счетчиков 16 и 17 и исключает сбои в их работе.

Если за время после tн до окончания ti в ПНЧ 6 ток от Ux(t) и заряд qc выполнили компенсацию целого числа Ni зарядов q и частичную компенсацию заряда qk в течение времени tk от последнего импульса 58 до окончания ti, а величина

q

Ux(t)dt, то справедливо равенство

Ux(t)dt, то справедливо равенство

Niq+qk= qc+

Ux(t)dt+qk=

Ux(t)dt+qk=

Ux(t)dt +

Ux(t)dt +

Ux(t)dt+

Ux(t)dt+

Ux(t)dt

Ux(t)dt

Ux(t)dt.

Ux(t)dt.

Для определения величины qk в начале ti+1 такта к ПНЧ 6 подключается напряжение Uo до появления первого импульса 58. Оно заканчивает компенсацию заряда qk током Uo/R за время t1, т.е. q qk+  t1 или qk q-

t1 или qk q-  t1. Поэтому можно записать равенство

t1. Поэтому можно записать равенство

Ux(t)dt (Ni+1)q

Ux(t)dt (Ni+1)q  t1.

t1.

Длительность t1 преобразуется в код η t1 ˙ fcp с помощью импульсов частоты fcp, снимаемых со среднего разряда счетчика 14. Использование для этих цепей частоты f генератора 50 целесообразно, так как в этом случае получаемая разрешающая способность намного будет больше требуемой точности измерения t1. Поэтому в прототипе величина этой частоты была равна fc f/No и она соответствовала временному кванту To/Nono. В предлагаемом АЦП поправки η при формировании результата преобразования суммируются р раз, поэтому для уменьшения общей погрешности, вызываемой ошибками квантования при измерении t1, временной квант tc при получении η должен быть уменьшен не менее чем в р раз, т.е. частота сигналов среднего разряда счетчика 14 должна быть не менее fcp pfc f.

f.

Выделение временного интервала t1 осуществляется с помощью элемента И 34 по сигналам с "0" выходов триггеров 21 и 22 и с выхода элемента ИЛИ 49. Через элемент И 34 импульсы fcp проходят на первые счетные входы первых средних разрядов счетчиков 16 и 17 и на их входы управления режимом вычитания, поэтому они будут уменьшать коды в этих счетчиках, вычитаясь из них с весом No/p, т.е. коды уменьшаться на  .

.

Кроме перечисленных импульсов Ni на вход управления распределителя 20 и на входы первых старших разрядов счетчиков 16 и 17 в начале каждого такта ti поступает первый импульс 58, проходящий через элементы ИЛИ 44 и И 35. Он относится к tiт такту работы АЦП и предназначен для окончательного формирования промежуточного результата преобразования Niт. Поэтому с учетом дополнительного импульса 58 в каждом текущем такте tiт в счетчиках 16 и 17 получаются коды

Niт (Nono+n)(Ni+1)  .

.

Если в это выражение подставить значения (Ni+1) из предыдущего равенства, а затем значения q, η и fcp, то получим

NiT= (Nono+n)

Ux(t)dt+

Ux(t)dt+  t

t

Ux(t)dt+

Ux(t)dt+

t1fcp=

t1fcp=

Ux(t)dt+

Ux(t)dt+ t1f

t1f

Ux(t)dt.

Ux(t)dt.

Значение Niт при последовательном выполнении тактов ti суммируются в счетчике 16 и записываются из счетчика 17 в ячейки памяти блока 52. Это начинается после импульса 53, который устанавливает в исходное "0" состояние триггеры 21-24 и счетчики 14, 16 и 18.

К окончанию текущего такта tiт код счетчика 16 увеличивается на Niт, а в счетчике 17 фиксируется код Niт. По заднему фронту его импульса 64 код Niт записывается в ячейку памяти блока 52, которая имеет адрес, соответствующий номеру i выполненного такта ti. Коды адреса передаются на соответствующие входы блока 52 с выходов счетчика 18, годе они формируются по импульсам 65 формирователя 30, проходящим через элемент И 37. Причем из этих импульсов 65 после импульса 53 появится только во втором такте после записи значения Niт в ячейку памяти, имеющую нулевой код адреса.

Емкость счетчика 18 равна р, поэтому через р импульсов 65 коды i адреса повторяются и в блоке 52 достаточно иметь р ячеек памяти. Смена кода адреса и изменение сигналов 74 происходит после окончания текущего tiт такта и после записи в блок 52 значения Niт, когда импульс 64 запускает формирователь 30, который далее запускает одновибратор 28, устанавливающий сигналом 69 в исходное нулевое состояние счетчик 17 перед началом формирования в нем нового кода Niт.

Если импульс синхронизации по шине 3 поступает в момент времени Т, то первый результат преобразования х1т будет получен через время Топосле выполнения р тактов ti. За это время, определяемое отсутствием сигнала 57, в счетчике 16 будет получен код, представляющий собой сумму р промежуточных результатов

X1T=  NiT=

NiT=

Ux(t)dt и соответствующий среднему значению Ux(t) за это время, равному

Ux(t)dt и соответствующий среднему значению Ux(t) за это время, равному (To)

(To)

Ux(t)dt, так как

Ux(t)dt, так как

X1T (To)·

(To)·

N

N

Код Х1т представляет собой результат преобразования Ux(t), но в нем младшие разряды не имеют достоверной информации, так как они не участвовали при определении величины qk, а в первых средних разрядах, имеющих емкость р, из-за погрешностей квантования при определении t1может находиться недостоверная информация. Поэтому запись кода результата преобразования Х1р импульсом 64 в регистр 19 выполняется из остальных средних и старших разрядов счетчика 16, общая емкость которых равна Nono, а вес первого из них равен No.

Вес младшего разряда регистра 19 равен единице, поэтому величина записанного кода х1р будет равна

X1p=

· Nono=

· Nono=  , где Δp

, где Δp  квант АЦП.

квант АЦП.

В дальнейшем, начиная с появления сигнала 57, в каждом такте tiработы АЦП формируется текущее значение результата преобразования Хт, который получается в счетчике 16 из предыдущего кода Хп, сформированного в ti-1 такте, путем уменьшения его на величину Nin, хранящуюся в блоке 52, и увеличения на Niт, т.е.

Хт Xn-Nin+Niт.

Вычитание Nin из Xn выполняется по импульсам 66, которые формируются из импульсов формирователя 30 в элементе И 38 и проходят через элемент ИЛИ 47 на вход управления распределителя 20, запуская его в работу. В это же время импульс 69 разрешает считывание кода Nin из блока 52, подключает на выход коммутатора 51 сигналы с выходов блока 52 и включает режим вычитания в счетчике 16, пройдя через элемент ИЛИ 48. Импульсы распределителя 20 с помощью элементов И 41-43 выполняют, как было показано выше, поразрядное вычитание кода Nin в счетчике 16. Затем в течение этого такта tiт его код будет увеличен на Niт.

Если окончание tiт происходит в момент времени tт, то получаемым кодам соответствуют следующие величины

Xn=

(t)dt,

(t)dt,

Nin=

Ux(t)dt, NiT=

Ux(t)dt, NiT=

Ux(t)dt.

Ux(t)dt.

Подставляя эти величины в выражение для Хт получим

XT=

Ux(t)dt-

Ux(t)dt- Ux(t)dt +

Ux(t)dt +  Ux(t)dt

Ux(t)dt

Ux(t)dt

Ux(t)dt  (Tn)

(Tn)  где Tn временной интервал от момента (tт-To) до tт, который равен То.

где Tn временной интервал от момента (tт-To) до tт, который равен То.

Из счетчика 16, в котором в tiт получен код Хт, в регистр 19 с окончанием импульса 64 записывается код Xтр=

, запускается формирователь 30, а затем одновибратор 28. Его импульс 69 проходит через элемент И 39, работа которого разрешена сигналом 57, и формирует импульсы 70, передаваемые по шине 4 и информирующие о готовности текущего результата Хтр.

, запускается формирователь 30, а затем одновибратор 28. Его импульс 69 проходит через элемент И 39, работа которого разрешена сигналом 57, и формирует импульсы 70, передаваемые по шине 4 и информирующие о готовности текущего результата Хтр.

Таким образом, через временные интервалы ti To/p формируются текущие значения импульсов преобразования Хтр, каждое из которых соответствует среднему значению преобразуемого напряжения за предыдущее время, равное То, т.е. Хтр не содержит составляющей погрешности от помехи с периодом повторения Tn To.

По сравнению с прототипом, в котором результат преобразования формируется через временные интервалы То, в предлагаемом АЦП это выполняется через время ti To/p, т.е. в р раз чаще и во столько же раз повышено быстродействие АЦП.

На повышение быстродействия АЦП и на выбор величины р накладываются ограничения, связанные с возникновением дополнительных погрешностей от квантования при получении кода η и р-кратного их суммирования, а также от р-кратной передачи зарядов q из конденсатора 12 в ПНЧ 6. Для уменьшения этих суммарных погрешностей до величин, не превышающих кванта АЦП, необходимо повысить не менее чем в р раз как частоту fcp, так и точность работы преобразователя 11.

Так повышение в р 8 раз быстродействия АЦП с параметрами прототипа, приведенными в тексте его описания: To 20 мс, Fq 25 кГц, No 29, no 24 и f 200 МГц, потребует следующегоо. Во-первых, частота fcp должна быть не менее fcp f  ≥ 3,2 МГц, но это не влияет на состав применяемых элементов, как и в прототипе быстродействующие интегральные схемы, например серии 100 или 500, должны быть использованы для построения генератора 50, счетчиков 14 и 15, триггеров 21-24 и управляемых ими элементов И и ИЛИ, а работающий на частоте fcpраспределитель 20 импульсов этих схем не требует и может быть выполнен на интегральных схемах, например, серии 530 или 555.

≥ 3,2 МГц, но это не влияет на состав применяемых элементов, как и в прототипе быстродействующие интегральные схемы, например серии 100 или 500, должны быть использованы для построения генератора 50, счетчиков 14 и 15, триггеров 21-24 и управляемых ими элементов И и ИЛИ, а работающий на частоте fcpраспределитель 20 импульсов этих схем не требует и может быть выполнен на интегральных схемах, например, серии 530 или 555.

Во-вторых, при компенсации заряда qk точность передачи заряда qc в ПНЧ должна быть повышена не менее чем в 8 раз. В прототипе для тактов работы АЦП, в которых определяется величина кода n, максимальному значению qc соответствует 2no квантов, т.е. динамический диапазон работы преобразователя 11 равен 32 и его погрешность не должна превышать 3% В предлагаемом АЦП для рассматриваемого примера его реализации с учетом запаса по точности она должна быть не более 0,3% Поэтому в прототипе преобразователь 11 можно было выполнять, например, в виде эмиттерного повторителя, а в данном АЦП целесообразно его выполнять на основе операционного усилителя с токовым выходным элементом.

Все это показывает, что предлагаемый АЦП может быть реализован с сохранением всех положительных свойств и точности прототипа, при этом повышается быстродействие за счет формирования результатов преобразования с более высокой частотой квантования преобразуемого сигнала при его интегрировании в течение времени, равного периоду помехи.

| название | год | авторы | номер документа |

|---|---|---|---|

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ С ПРОМЕЖУТОЧНЫМ ПРЕОБРАЗОВАНИЕМ В ЧАСТОТУ | 1990 |

|

RU2007029C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1991 |

|

RU2012132C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1992 |

|

RU2037267C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1992 |

|

RU2062549C1 |

| ИНТЕГРИРУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1991 |

|

RU2012131C1 |

| ИНТЕГРИРУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1991 |

|

RU2012130C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ СОВМЕЩЕННОГО ИНТЕГРИРОВАНИЯ | 1992 |

|

RU2036559C1 |

| Аналого-цифровой преобразователь | 1990 |

|

SU1748253A1 |

| Аналого-цифровой преобразователь | 1991 |

|

SU1800617A1 |

| Аналого-цифровой преобразователь | 1990 |

|

SU1730722A2 |

Изобретение относится к импульсной технике, в частности к преобразователям напряжения в цифровой код с промежуточным преобразованием напряжения в частоту импульсов, и может быть использовано в устройствах сбора аналоговой информации систем контроля и испытаний изделий и управления технологическими процессами. Аналого-цифровой преобразователь содержит преобразователь напряжения в частоту импульсов, три счетчика, два триггера, четыре одновибратора, два формирователя импульсов, элементы И и ИЛИ, генератор и распределитель импульсов, преобразователь напряжения в ток, три переключателя, ключ, накопительный элемент на конденсаторе и токоограничивающий элемент на резисторе. Новым является введение двух счетчиков, двух триггеров, элементов И, блока запоминания и коммутатора кодов, благодаря которым измерение входного напряжения выполняется за то же время, что и в прототипе, а результаты формируются через меньшие временные интервалы, что повышает быстродействие преобразователя. 2 ил.

АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ, содержащий преобразователь напряжения в частоту импульсов, выход которого соединен с первыми входами первого, второго и третьего элементов И и первого элемента ИЛИ, первый вход является шиной нулевого потенциала и объединен с первым входом преобразователя напряжения в ток и первым информационным входом первого переключателя, второй вход через токоограничивающий элемент объединен с первым информационным входом второго переключателя, а третий вход соединен с выходом третьего переключателя, первый информационный вход которого объединен с вторым входом преобразователя напряжения в ток и является первой входной информационной шиной, второй информационный вход второй входной информационной шиной, а вход управления подключен к единичному выходу первого триггера, входы управления первого и второго переключателей объединены, их выходы объединены через накапливающий элемент, а вторые информационные входы объединены с входом ключа и соединены с выходом последнего, вход установки исходного состояния первого триггера объединен с одноименными входами второго триггера и первого счетчика и через первый одновибратор подключен к шине синхронизации, нулевой выход первого триггера соединен с первым входом четвертого элемента И, а нулевой вход объединен с вторым входом третьего элемента И, выход которого через второй одновибратор подключен к второму и первому входам соответственно первого и второго элементов ИЛИ, выходы которых соединены с первым и вторым входами соответственно пятого и второго элементов И, выход последнего из которых подключен к входу синхронизации генератора импульсов, к входу установки исходного состояния второго счетчика и единичному входу второго триггера, единичный выход которого соединен с первым и вторым входами соответственно шестого и первого элементов И, нулевой вход с выходом последнего и объединен с первым входом третьего элемента ИЛИ, нулевой выход с вторым входом четвертого элемента И, третий вход которого подключен к выходу среднего разряда первого счетчика и через третий одновибратор объединен с входом синхронизации распределителя импульсов, а выход подключен к первому счетному входу среднего разряда третьего счетчика, первый счетный вход старшего разряда которого соединен с выходом пятого элемента И, счетные входы младших разрядов с выходами элементов И первой группы, а выходы средних и старших разрядов с соответствующими информационными входами регистра, выходы разрядов которого являются выходной шиной, а вход записи кода подключен к выходу первого формирователя импульсов и объединен с входом второго формирователя импульсов, выход генератора импульсов соединен со счетным входом первого счетчика и вторым входом шестого элемента И, выход которого подключен к счетному входу второго счетчика, первые входы элементов И первой группы соединены с выходами младших разрядов распределителя импульсов, первые входы седьмого и восьмого элементов И объединены, выход четвертого одновибратора соединен с первым входом девятого элемента И, выход которого является шиной готовности результата преобразования, отличающийся тем, что в него введены блок запоминания кодов, четвертый и пятый счетчики, коммутатор кодов, третий и четвертый триггеры, четвертый, пятый и шестой элементы ИЛИ, десятый элемент И, вторая и третья группы элементов И, первые входы которых соединены соответственно с выходами средних и старших разрядов распределителя импульсов, вторые входы элементов И всех трех групп подсоединены к соответствующим выходам коммутатора кодов, выходы элементов И второй группы соединены соответственно с вторым счетным входом первого среднего разряда и счетными входами остальных средних разрядов третьего счетчика, а выходы элементов И третьей группы соединены соответственно с вторым счетным входом первого старшего разряда и со счетными входами остальных старших разрядов третьего счетчика, первый счетный вход старшего разряда которого соединен с первым входом четвертого элемента ИЛИ, а счетные входы всех разрядов третьего счетчика объединены с одноименными счетными входами разрядов четвертого счетчика, выходы разрядов которого подключены к соответствующим информационным входам блока запоминания кодов, а вход включения режима вычитания подключен к выходу четвертого элемента И и объединен с первым входом пятого элемента ИЛИ, выход которого соединен с входом включения режима вычитания третьего счетчика, а второй вход соединен с выходом четвертого одновибратора и объединен с входом установки исходного состояния четвертого счетчика, входом управления коммутатора кодов, входом управления считыванием блока запоминания кодов и единичным входом третьего триггера, нулевой выход которого подключен к второму входу второго элемента ИЛИ, вход установки исходного состояния объединен с одноименными входами четвертого триггера, первого, третьего и пятого счетчиков и входом управления ключа, а единичный выход подключен к первым входам шестого элемента ИЛИ и десятого элемента И, второй вход которого соединен с выходом первого элемента ИЛИ, третий вход объединен с одноименным входом первого элемента И и входом первого формирователя импульсов и соединен с нулевым выходом первого триггера, а выход с вторым входом третьего элемента ИЛИ, выход которого подключен к единичному входу первого триггера, единичный выход которого соединен с входом управления первого переключателя, второй информационный вход которого подключен к выходу преобразователя напряжения в ток, вторые информационные входы второго и третьего переключателей объединены, четвертый вход четвертого элемента И объединен с вторыми входами пятого и седьмого элементов И и соединен с выходом шестого элемента ИЛИ, второй вход которого объединен с вторыми входами восьмого и девятого элементов И и подключен к единичному выходу четвертого триггера, единичный вход которого соединен с выходом первого старшего разряда первого счетчика, выход второго старшего разряда и выход переполнения средних разрядов которого подключены к нулевым входам соответственно третьего и первого триггеров, выход второго формирователя импульсов подключен к входу четвертого одновибратора и первому входу восьмого элемента И, выход которого соединен с вторым входом четвертого элемента ИЛИ, выход которого подключен к управляющему входу распределителя импульсов, третьи входы второго и пятого элементов И объединены и подключены к нулевому выходу второго триггера, выход первого формирователя импульсов соединен с входом записи блока запоминания кодов, адресные входы которого подключены к выходам разрядов пятого счетчика, счетный вход которого соединен с выходом седьмого элемента И, а первые и вторые входы коммутатора кодов подключены соответственно к выходам разрядов второго счетчика и блока запоминания кодов.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Аналого-цифровой преобразователь | 1990 |

|

SU1748253A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1995-06-27—Публикация

1992-04-17—Подача