Изобретение относится к автоматике и импульсной технике и используется для формирования исполнительной команды через определенный интервал времени, называемый уставкой, задаваемый последовательным импульсным кодом перед запуском таймера. Таймер предназначен для эксплуатации в условиях воздействия интенсивных электромагнитных помех и импульсного ионизирующего излучения.

Цель изобретения повышение быстродействия в режимах задания и контроля уставки.

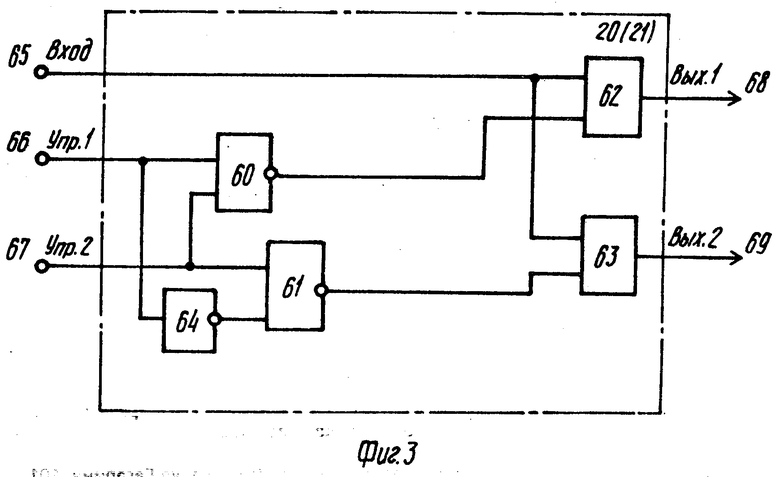

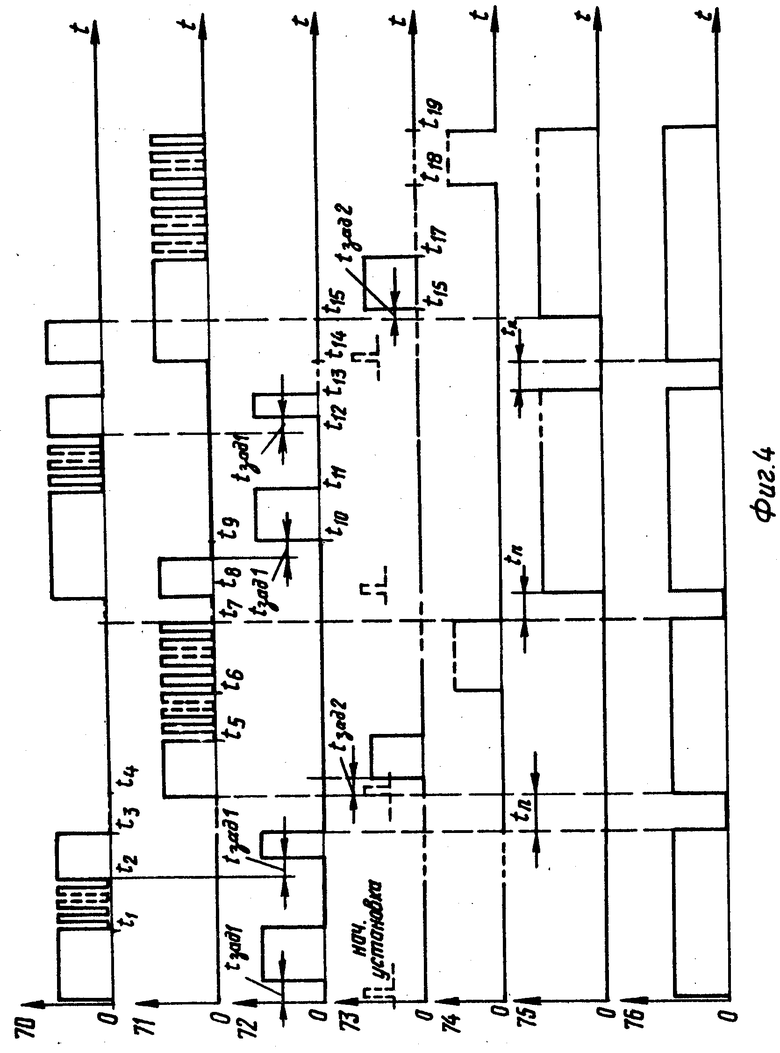

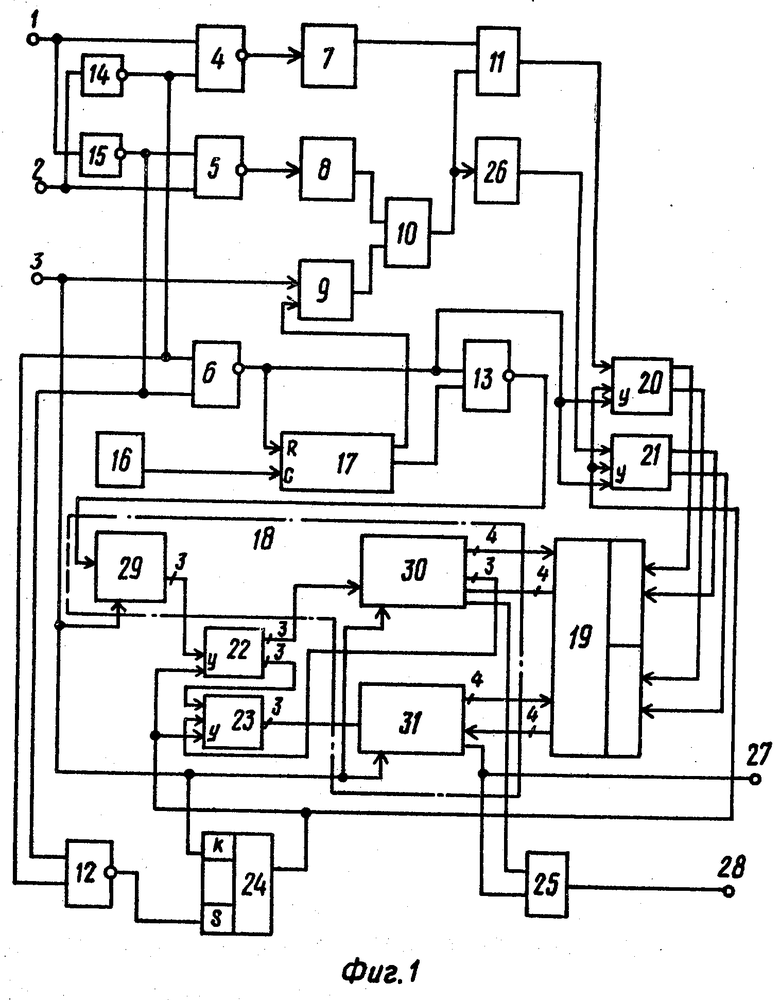

На фиг. 1 представлена структурная схема таймера с контролем; на фиг. 2 структурная схема третьего и четвертого коммутаторов; на фиг. 3 структурная схема первого и второго коммутаторов; на фиг. 4 представлены временные диаграммы работы таймера с контролем.

Таймер с контролем (фиг. 1) содержит вход 1 разрешения записи, вход 2 разрешения контроля, вход 3 начальной установки, первый, второй, третий элементы И-НЕ 4 6, первый 7, второй 8, третий 9 формирователи импульсов, первый, второй элементы ИЛИ 10, 11 первый, второй элементы ИЛИ-НЕ 12, 13, второй, первый элементы НЕ 14, 15, задающий генератор 16, делитель 17 частоты, счетчик 18 импульсов, блок 19 памяти, первый 20, второй 21, третий 22, четвертый 23 коммутаторы, триггер 24, элемент 25 сложения по модулю два, элемент 26 задержки, выход 27, контрольный выход 28. Счетчик 18 импульсов содержит младшие 29 разряды, первую 30 и вторую 31 группы старших разрядов.

На фиг. 2 коммутатор 22 содержит двунаправленные ключи 32, 33, инвертор 34. Вход 35 коммутатора 22 соединен с выходом линейки счетных сигналов 2-го разряда счетчика 18 импульсов. Входы 36, 37 соединены, соответственно, с прямым и инверсным выходами 2-го разряда счетчика 18 импульсов. Выходы 38 40 образуют первую группу выходов коммутатора 22 и соединены с соответствующими входами линейки счетных сигналов 3-го разряда счетчика 18. Выходы 41 43 образуют вторую группу выходов коммутатора 22 и соединены с соответствующими входами 44 46 первой группы коммутатора 23. Коммутатор 23 содержит двунаправленные ключи 47 49, инвертор 50, резисторы 51, 52.

Вход 53 коммутатора 23 соединен с выходом линейки счетных сигналов 7-го разряда счетчика 18 импульсов. Входы 54, 55 соединены соответственно с прямым и инверсным выходами 7-го разряда счетчика 18. Входы 53 55 образуют вторую группу входов коммутатора 23. Выходы 56 58 коммутатора 3 соединены с соответствующими входами линейки счетных сигналов 8-го разряда счетчика 18. Вход 59 является входом управления коммутаторов 22, 23.

Каждый из коммутаторов 20, 21 содержит два элемента И-НЕ 60, 61, два элемента И 62, 63, инвертор 64. Вход 65 является входом коммутатора 20 (21). Вход 66 является первым, а вход 67 вторым управляющим входом коммутатора 20 (21). Выходы 68 и 69 являются соответственно первым и вторым выходами коммутатора 20 (21).

Таймер с контролем работает следующим образом. Вначале организуется задание кода уставки в первую группу 30 старших разрядов счетчика 18. При этом на вход 1 разрешения записи подается сигнал высокого уровня "лог. 1", на входе 2 разрешения контроля сигнал "лог. 0" (см. диаграммы 70, 71, фиг. 4 интервал времени 0-t1). В течение интервала времени 0-t1 на вход 3 таймера подается сигнал начальной установки, которым производится обнуление триггерных устройств формирователя 9, счетчика 18 и RS-триггера 24. Питание элементов, схем и блоков таймера (см. диаграмму 76, фиг. 4) в рассматриваемом режиме производится от вторичного источника питания, который запитывается либо по отдельному входу таймера, либо от сигнала, поступающего на вход 1 (вход запитки таймера, вторичный источник питания и цепи питания элементов, схем и блоков таймера на схемах фиг. 1 3 не показаны). На входе инвертора 14 сигнал "лог. 1", потому сигнал "лог. 1" со входа 1 таймера проходит на вход формирователя 7. Через время tзад.1 с момента поступления сигнала по входу 1 формируется сигнал разрешения записи на выходе формирователя 7 (см. диаграмму 72, фиг. 4). Время tзад.1 определяется инерционностью RC-цепи на входе формирователя 7. Через элемент 11 ИЛИ указанный сигнал поступает на вход коммутатора 20. Так как с прямого выхода RS-триггера 24 на первые входы 66 (фиг. 3) управления коммутаторов 20, 21 поступает сигнал "лог. 0" а на вторых входах 67 управления коммутаторов 20, 21 действует сигнал "лог. 1" с выхода элемента И-НЕ 6 сигнал разрешения записи с входа 65 через элемент И 62 поступает на первый выход 68 коммутатора 20 и на первый вход разрешения записи блока 19 памяти. Поскольку элемент И-НЕ 5 закрыт сигналом "лог. 0" со входа 2 таймера, а делитель 17 блокирован сигналом "лог. 1" с выхода элемента И-НЕ 6, действующим по входу обнуления делителя 17, на выходах формирователей 8, 9 элемента ИЛИ 10, элемента 26 задержки сигнал разрешения считывания не формируется. В результате, в элементы памяти блока 19 памяти, связанные с разрядными выходами первой группы 30 старших разрядов счетчика 18 запишется нулевая информация. Кодовые сигналы задания, поступающие по входу 1 в виде импульсов отрицательной полярности (относительно уровня "лог. 1" см. интервал времени t1 t2, фиг. 4), через инвертор 15 и элементы И-НЕ 6, ИЛИ-НЕ 13 поступают на счетный вход счетчика 18.

Поскольку на управляющих входах коммутатора 22, 23 (вход 59, фиг. 2) действует сигнал "лог. 0", коммутаторы 22, 23 в этом режиме обеспечивают последовательное заполнение первой группы 30 старших разрядов счетчика 18 в соответствии с логикой кода Грея (ключи 32, 47 49 коммутаторов 22, 23 открыты, ключ 33 закрыт. Сигналы с выхода линейки счетных сигналов и выходов 2-го разряда счетчика 18 через входы 35 37 коммутатора 22 проходят на выходы 38 40 коммутатора 22 и на соответствующие входы 3-го разряда счетчика 18. Сигналы с выхода линейки счетных сигналов 7-го разряда счетчика 18 через входы 53 55 коммутатора 23 проходят на выходы 56 58 коммутатора 23 и на соответствующие входы 8-го разряда счетчика 18). В счетчике, работающем в коде Грея, каждым нечетным (1-м, 3-м и т.д.) импульсом производится переключение в противоположное состояние 1-го разряда счетчика 18, каждым четным (2-м, 4-м, и т. д. ) импульсом кодовой последовательности производится переключение в противоположное состояние разрядов с 2-го по 12-ый, причем переключение происходит в разряде, следующем за самым младшим, находящимся в состоянии "лог. 1". На время действия каждого кодового импульса делитель 17 частоты кратковременно разблокируется по входу обнуления, однако длительность кодового импульса и коэффициенты пересчета делителя 17 по его выходам выбраны так, что сигналы на этих выходах делителя 17 формироваться не успевают. Первым же кодовым импульсом производится разряд конденсатора RC-цепи формирователя 7, благодаря чему он к моменту времени t2 подготовлен к формированию второго сигнала разрешения записи. Формирование сигнала разрешения записи производится с задержкой tзад.1 относительно момента времени t2 (диаграмма 72, фиг. 4). Указанный сигнал также поступает через элемент ИЛИ 11 и коммутатор 20 на первый вход разрешения записи блока 19 памяти, в результате чего в соответствующие элементы памяти блока 19 памяти, связанные с разрядными выходами первой группы 30 старших разрядов счетчика 18, будет записана первая часть кода уставки.

В интервале времени t3 t4 сигналы с входов 1, 2 таймера снимаются, может быть на сколько угодно продолжительное время снято и питание элементов, блоков и схем таймера. В интервале времени t4 t7 производится контроль кода, записанного в первую группу 30 старших разрядов счетчика 18. В указанном режиме сигнал "лог. 1" поступает на вход 2 таймера, на входе 1 таймера сигнал "лог. 0". Одновременно с началом сигнала на входе 1 (момент времени t4) подается питание таймера, по входу 3 подается сигнал обнуления триггерных устройств, входящих в состав формирователя 9, счетчика 18, RS-триггера 24. Поскольку на выходе инвертора 14 присутствует сигнал "лог. 1" формирователь 7 сигнала разрешения записи не формирует. Сигнал с выхода 2 через элемент И-НЕ 5 поступает на вход формирователя 8, на выходе которого формируется сигнал считывания с задержкой tзад.2 относительно момента t4 (диаграмма 73, фиг. 4). Указанный сигнал через элемент 10 ИЛИ поступает на входы элемента ИЛИ 11 и элемента 26 задержки. Поскольку RS-триггер 24 в нулевом состоянии, а на выходе элемента И-НЕ 6 сигнал "лог. 1", формируются сигналы на первых выходах 68 коммутаторов 20 и 21 и на первых входах разрешения записи и считывания блока 19 памяти, в результате, из соответствующих элементов блока 19 памяти происходит считывание информации в разряды первой группы 30 старших разрядов счетчика 18. К моменту времени t5 в указанных разрядах счетчика 18 восстановлена ранее записанная информация и в интервале времени t5 t7 производится досчет первой группы 30 разрядов до переполнения. Счетные импульсы, формируемые из входных импульсов отрицательной полярности, проходит через инвертор 14, элементы И-НЕ 6, ИЛИ-НЕ 13 на вход счетных сигналов счетчика 18 импульсов. При появлении сигнала переполнения на выходе первой группы 30 старших разрядов счетчика 18 он проходит через элемент 25 сложения по модулю два на контрольный выход 28 (см. диаграмму 74, фиг. 4, момент времени t6). После регистрации указанного сигнала на выходе 28 таймера, сигнал на входе 2 и питание таймера снимаются. В интервале времени t8 t13 производится задание кода уставки на вторую группу 31 старших разрядов счетчика 18. Особенностью процессов в указанном режиме является то обстоятельство, что он начинается с подачи сигналов высокого уровня одновременно на входах 1 и 2 таймера. Одновременно с началом подачи этих сигналов, как и в предыдущих режимах, формируется напряжение питания таймера, а на входе 3 формируется сигнал начальной установки, в результате, триггерные устройства формирователя 9 счетчика 18 импульсов, RS-триггера 24 обнуляется. В результате того, что в интервале времени t8 t9 на входах 1, 2 таймера одновременно присутствуют сигналы "лог. 1", на выходе элемента ИЛИ-НЕ 12 также формируется сигнал "лог. 1", и после окончания сигнала начальной установки таймера RS-триггер 24 переключится в состояние "лог. 1" (см. диаграмму 75, фиг. 4, интервал времени t8 t13). Сигнал разрешения записи на входе формирователя 7 может начать формироваться только после снятия в момент времени t9 сигнала "лог. 1" на входе 2 таймера, т. к. до этого момента элемент И-НЕ 4 закрыт сигналом "лог. 0" с выхода инвертора 17. Элемент И-НЕ 5 в интервале времени t8 t11 закрыт сигналом "лог. 0" с выхода инвертора 14, поэтому сигнал разрешения считывания на выходе формирователя 8 в указанном режиме не формируется. С задержкой tзад.1 относительно момента времени t9 формируется сигнал разрешения записи (диаграмма 72, фиг. 4, интервал времени t10 t11). Указанный сигнал через элемент ИЛИ 11 поступает на вход коммутатора 20. Поскольку RS-триггер 24 находится в состоянии "лог. 1", а элемент И-НЕ 6 формирует на выходе сигнал "лог. 1", на управляющих входах 66, 67 коммутаторов 20, 21 присутствуют сигналы "лог. 1", в результате на выходе элемента И-НЕ 60 и на выходе инвертора 64 сигнал "лог. 0", на выходе элемента И-НЕ 61 сигнал "лог. 1". Сигнал с входа 65 коммутатора 20 через элемент И 63 поступает на второй выход 69 и далее поступает на второй вход разрешения записи блока 19 памяти. При этом в элементы памяти блока 19 памяти, связанные с разрядными выходами второй группы 31 старших разрядов счетчика 18, запишется нулевая информация. На входе 59 управления коммутаторов 22, 23 действует сигнал "лог. 1", ключи 32, 47, 48, 49 закрыты (т. к. на выходах инверторов 34, 50 сигнал "лог. 0", см. фиг. 2). Ключ 33 открыт. В результате указанной коммутации сигналы с выхода линейки счетных сигналов и выходов 2-го разряда счетчика 18 через входы 35 37 коммутатора 22, ключ 33, выходы 41 43 коммутатора 22, входы 44 46 коммутатора 23, резисторы 51, 52, выходы 56 58 коммутатора 23 поступают на соответствующие входы 8-го разряда счетчика 18 импульсов. В интервале времени t11 t12 происходит заполнение второй группы 31 старших разрядов счетчика 18 кодовыми сигналами, поступающими по входу 1 таймера (через инвертор 15, элементы И-НЕ 6, ИЛИ-НЕ 13, младшие разряды 29 счетчика 18). В интервале времени t12 t13 (с задержкой tзад.1 относительно момента времени t12) на втором входе разрешения записи блока 19 памяти формируется очередной сигнал, по которому в элементы памяти блока 19 памяти, связанные с второй группой 31 старших разрядов счетчика 18, записывается информация. После возможной паузы (интервал времени t13 t14) по сигналам на входах 1, 2 и по питанию таймера организуется режим контроля кода, записанного во вторую группу 31 старших разрядов счетчика 18. Как и в ранее описанных режимах, происходит предварительное обнуление триггерных устройств таймера. В момент времени t15 переключится и будет находиться в состоянии "лог. 1" до момента времени t19 RS-триггер 24 (см. диаграмму 75, фиг. 3). Сигнал разрешения считывания, формируемый в интервале времени t16 t17 формирователей 8, коммутируется на вторые выходы коммутаторов 20, 21 и поступает на вторые входы разрешения записи и считывания блока 19 памяти. В результате происходит считывание из соответствующих элементов памяти блока 19 памяти информации во вторую группу 31 старших разрядов. В интервале времени t17 t19 происходит досчет второй группы 31 старших разрядов счетчика 18.

В момент времени t18 начинает формироваться сигнал переполнения на выходе переполнения второй группы 31 старших разрядов счетчика 18, который проходит через элемент 25 на контрольный выход 28 таймера (см. диаграмму 74, фиг. 4). После регистрации указанного сигнала на выходе 28 таймера сигнал на его входе 2 и питание таймера снимаются. Таймер готов к работе в режиме отработки уставки. Для включения таймера в режим отработки уставки необходимо подавать напряжение питания на все его элементы, схемы и блоки и одновременно с фронтом напряжения питания сформировать по входу 3 импульс начальной установки, обнуляющий входящие в его состав триггерные устройства. Поскольку в рассматриваемом режиме делитель 17 частоты не блокируется входными сигналами таймера (на входах 1 и 2 сигналы отсутствуют), сигналы с выхода задающего генератора 16 осуществляют счет делителя 17 в последовательном двоичном коде. Импульс переполнения с первого выхода делителя 17, формируемый примерно через 2 мс после подачи напряжения питания таймера, вызывает срабатывание формирователя 9. Импульс разрешения считывания, формируемый на выходе формирователя 9, проходит через элементы И-ИЛИ 10, ИЛИ 11, элемент 26 задержки на входы коммутаторов 20, 21. Поскольку на вторых входах управления коммутаторов 20, 21 сигнал "лог. 0" сигналы разрешения записи и считывания будут формироваться на обоих входах блока 19 памяти. В результате, произойдет считывание информации во все старшие разряды счетчика 18 импульсов. Тактовые сигналы со второго выхода делителя 17 (Т 32 с) поступают через элемент ИЛИ-НЕ 13 на счетный вход счетчика 18. Поскольку RS-триггер 24 находится в состоянии "лог. 0" младшие разряды 29, первая 30 и вторая 31 группы старших разрядов счетчика 18 соединены последовательно. Счетчик 18 работает до переполнения по выходу второй группы 31 старших разрядов. Сигнал переполнения регистрируется на выходе 27 таймера. В качестве выхода переполнения второй группы 31 старших разрядов может быть использован выход линейки счетных сигналов последнего разряда или дешифратор, подключенный к определенным разрядным выходам второй группы 31 старших разрядов.

| название | год | авторы | номер документа |

|---|---|---|---|

| ТАЙМЕР С КОНТРОЛЕМ | 1986 |

|

SU1505257A1 |

| ТАЙМЕР С КОНТРОЛЕМ | 1995 |

|

RU2113007C1 |

| Многоканальный программируемый преобразователь код-фаза | 1990 |

|

SU1742998A1 |

| Цифровой фазометр | 1989 |

|

SU1688189A1 |

| ТАЙМЕР С КОНТРОЛЕМ | 1990 |

|

RU2037872C1 |

| ТАЙМЕР С КОНТРОЛЕМ | 1991 |

|

SU1769611A1 |

| Многоканальное программное задающее устройство | 1986 |

|

SU1383297A1 |

| Устройство для вычисления временных интервалов микропроцессорных систем | 1980 |

|

SU960781A1 |

| Формирователь импульсных последовательностей для контроля запоминающих модулей на цилиндрических магнитных доменах | 1987 |

|

SU1513514A1 |

| УСТРОЙСТВО ДЛЯ ЗАДЕРЖКИ СИГНАЛОВ | 1992 |

|

RU2024186C1 |

Изобретение относится к автоматике и импульсной технике и используется для формирования исполнительной команды через определенный интервал времени, называемой уставкой и задаваемый последовательным кодом перед запуском таймера. Цель изобретения - повышение быстродействия в режимах задания и контроля уставки. Таймер с контролем содержит элементы И-НЕ 4-6:формирователи импульсов 7-9; элементы ИЛИ 10,11; элементы ИЛИ-НЕ 12, 13; элементы НЕ 14, 15; задающий генератор 16; делитель частоты 17; счетчик импульсов 18; блок памяти 19; коммутаторы 20-23, триггер 24, элемент сложения по модулю два 25, элемент задержки 26. 4 ил.

ТАЙМЕР С КОНТРОЛЕМ, содержащий блок памяти, делитель частоты, счетчик импульсов, задающий генератор, два элемента ИЛИ, элемент задержки, два формирователя импульсов, элемент сложения по модулю два, триггер, причем выход задающего генератора соединен с синхровходом делителя частоты, вход начальной установки таймера подключен к входу обнуления счетчика импульсов, информационные выходы старших разрядов счетчика импульсов соединены с информационными входами блока памяти, выходы которого соединены с входами установки в единицу, старших разрядов счетчика импульсов, отличающийся тем, что, с целью повышения быстродействия в режимах задания и контроля установки, он содержит два элемента НЕ, три элемента И-НЕ, третий формирователь, импульсов, два элемента ИЛИ-НЕ и четыре коммутатора, причем вход разрешения записи таймера соединен с первым входом первого элемента И-НЕ, через первый элемент НЕ с первыми входами второго и третьего элементов И-НЕ и первого элемента ИЛИ-НЕ, вход разрешения контроля таймера соединен со вторым входом второго элемента И-НЕ и через второй элемент НЕ со вторыми входами первого и третьего элемента И-НЕ и первого элемента ИЛИ-НЕ, выход которого соединен с S-входом триггера, R-вход которого соединен с входом начальной установки таймера, прямой выход триггера соединен с первыми управляющими входами первого и второго коммутаторов и управляющими входами третьего и четвертого коммутаторов, выходы первого и второго элементов И-НЕ через соответственно первый и второй формирователи импульсов соединены с первыми входами соответственно второго и первого элементов ИЛИ, выход первого элемента ИЛИ соединен с вторым входом второго элемента ИЛИ, выход которого соединен с информационным входом первого коммутатора, первый и второй выходы которого соединены соответственно с первым и вторым входами разрешения записи блока памяти, первый и второй входы разрешения считывания которого соединены соответственно с первым и вторым выходами второго коммутатора, информационный вход которого через элемент задержки соединен с выходом первого элемента ИЛИ, второй вход которого соединен с выходом третьего формирователя импульсов, первый и второй входы которого соединены соответственно с входом начальной установки таймера и первым выходом делителя частоты, второй выход которого соединен с первым входом второго элемента ИЛИ-НЕ, вход обнуления делителя частоты соединен с выходом третьего элемента И-НЕ, вторыми управляющими входами первого и второго коммутаторов и вторым входом второго элемента ИЛИ-НЕ, выход которого соединен со счетным входом счетчика импульсов, группа выходов младших разрядов которого соединена с группой информационных входов третьего коммутатора, первая и вторая группы выходов которого соединены соответственно с входами первой группы старших разрядов счетчика импульсов и с информационными входами первой группы четвертого коммутатора, вторая группа информационных входов и группа выходов которого соединены соответственно с выходами группы старших разрядов счетчика импульсов и входами второй группы старших разрядов счетчика импульса, первый и второй выходы переполнения которого соединены с входами элемента сложения по модулю два, выход которого является контрольным выходом таймера.

| ТАЙМЕР С КОНТРОЛЕМ | 1986 |

|

SU1505257A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1995-10-27—Публикация

1991-04-04—Подача