1

Изобретение относится к области вычислительной техники, автоматики и телемеханики.

Известен синхронизатор импульсов, содержащий логические элементы И-НЕ, R-5 триггеры памяти и R-5 триггер обратной связи.

Цель изобретения - упрощение устройства, расщирение его функциональных возможностей и повышение надежности работы.

Для этого предлагаемый синхронизатор содержит два трехпозиционных переключателя, причем вход установки «1 К-S триггера обратной связи и входы установки «1 и «О первого R-S триггера памяти подключены к щине управляющих сигналов «Останов, «Старт, «Стоп соответственно, выходы первого R-5 триггера памяти соединены со входами первого и второго логического элементов И-НЕ, другие входы которых подключены к щине импульсов, а выходы соединены со входами установки «1 и «О второго R-S триггера памяти и со входами третьего элемента И-НЕ, дополнительный вход которого подключен к выходу «1 этого триггера, а выход подключен ко входу установки «О R-S триггера обратной связи, выход «1 которого соединен с дополнительным входом первого элемента И-НЕ и входом установки «О первого R-5 триггера памяти, причем входы R-5 Триггера обратной связи и первого R--S триггера памяти подключены к щинам управляющих сигналов через два трехпозиционных переключателя, замыкающие контакты которых соединены с общей щиной, к первому замыкаемому контакту первого переключателя подключен вход установки «1 R-5 триггера обратной связи, второй замыкаемый контакт соединен со входом установки «I первого R-S триггера памяти и с первым замыкаемым контактом второго переключателя, второй замыкаемый контакт которого соединен со входом установки «О первого R-5 триггера памяти. Кроме того, с целью расщирения функциональных возможностей, в нем выходная щина

соединена со входом установки в «О первого R-5 триггера памяти.

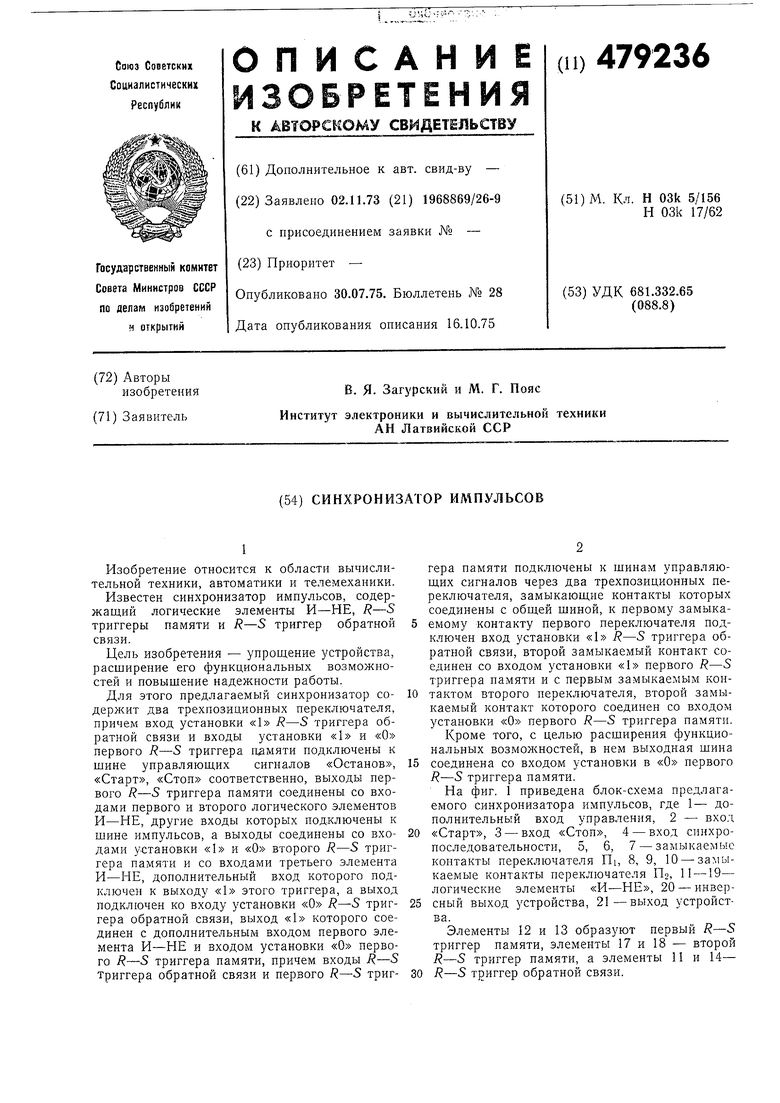

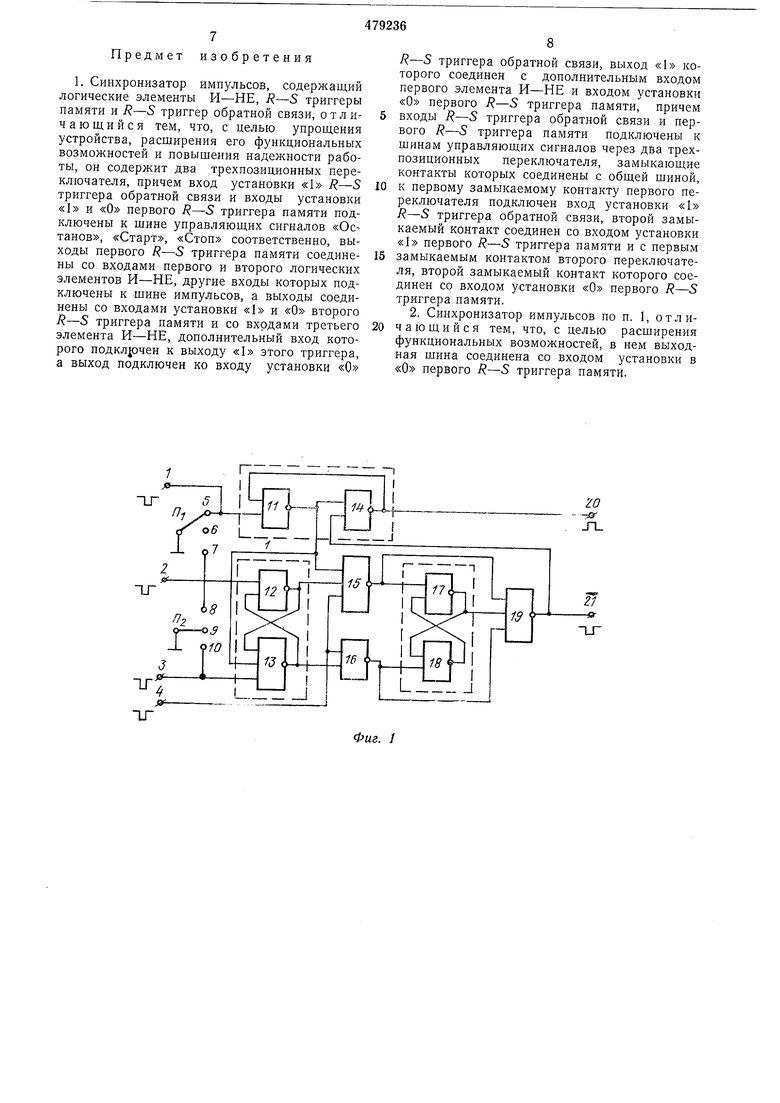

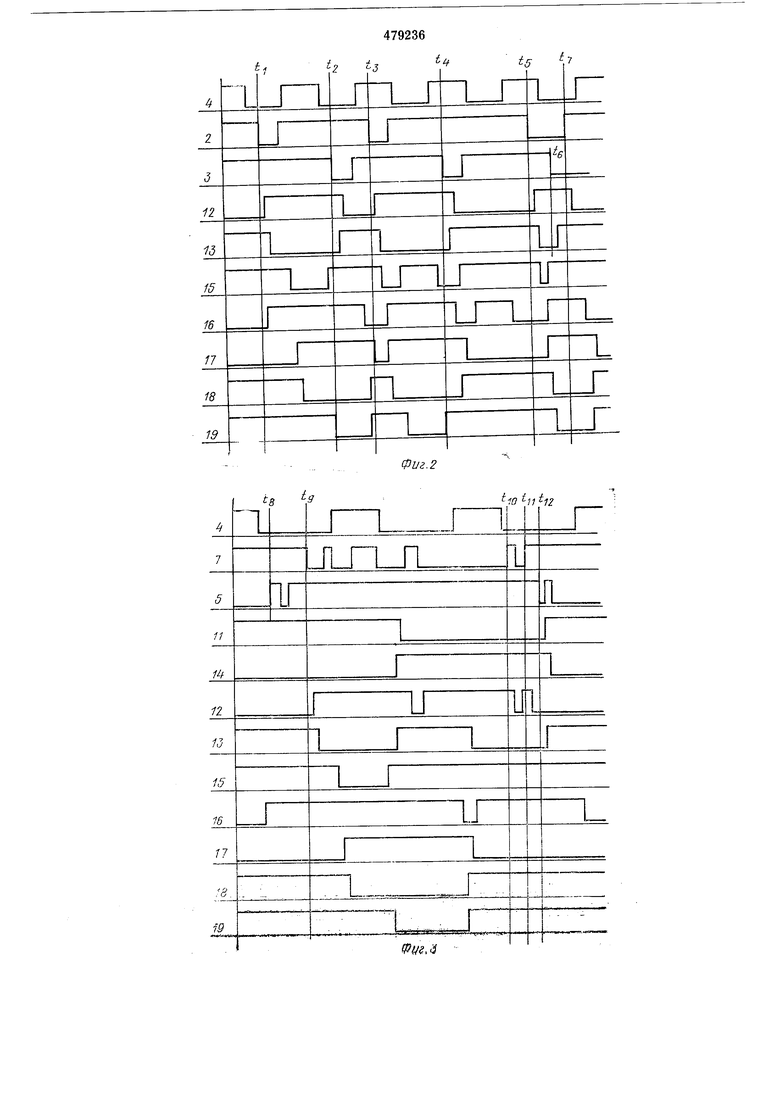

На фиг. 1 приведена блок-схема предлагаемого синхронизатора импульсов, где 1- дополнительный вход управления, 2 - вход

«Старт, 3 - вход «Стоп, 4 - вход спнхропоследовательности, 5, 6, 7 - замыкаемые контакты переключателя Hi, 8, 9, 10 - замыкаемые контакты переключателя По, 11 -19- логические элементы «И-НЕ, 20 - инверсный выход устройства, 21-выход устройства.

Элементы 12 и 13 образуют первый R-5 триггер памяти, элементы 17 и 18 - второй R-5 триггер памяти, а элементы II и 14-

R-S триггер обратной связи.

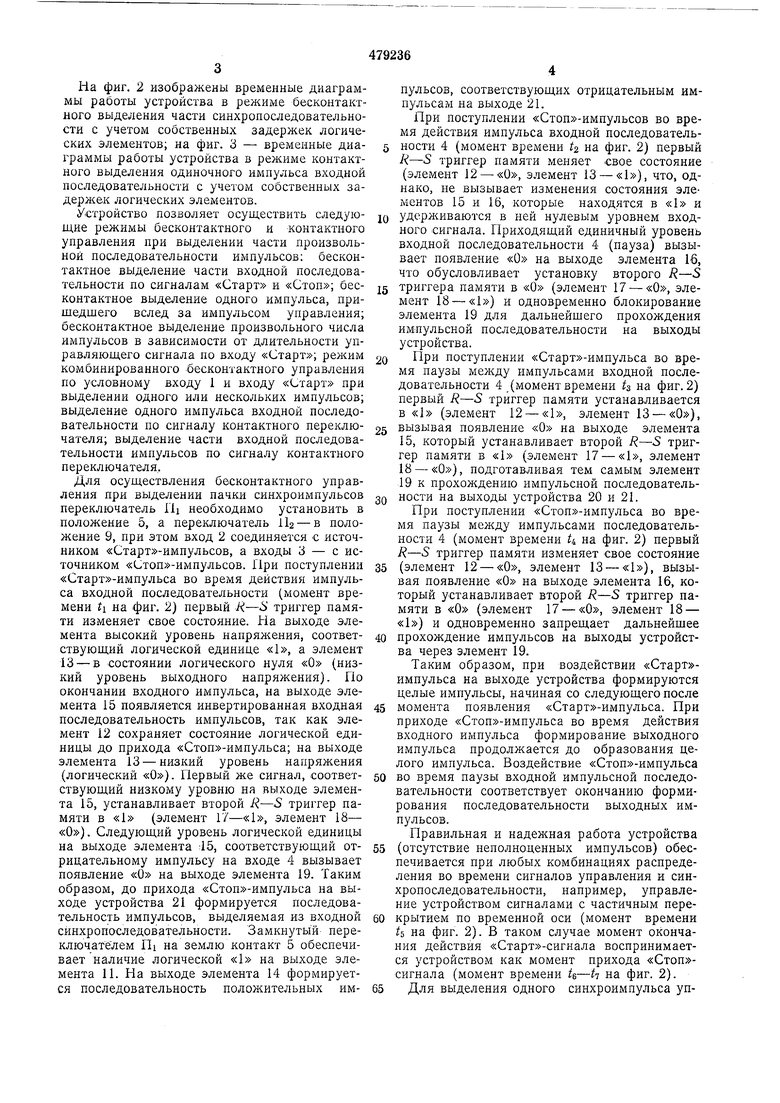

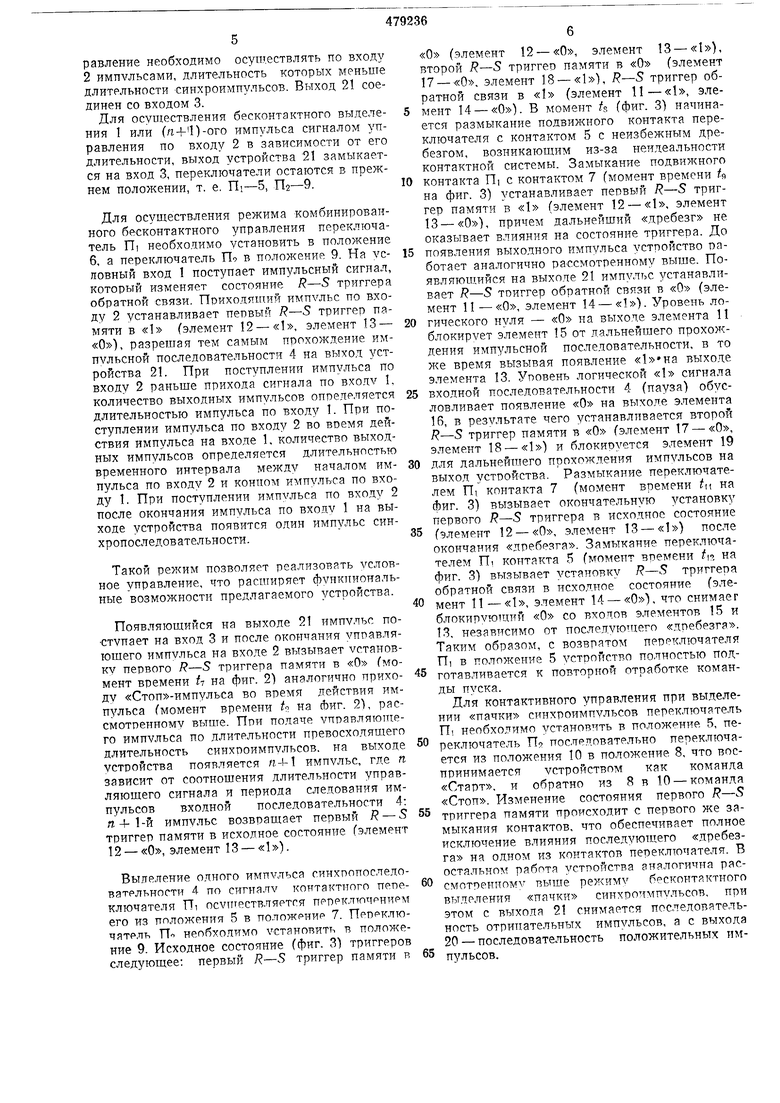

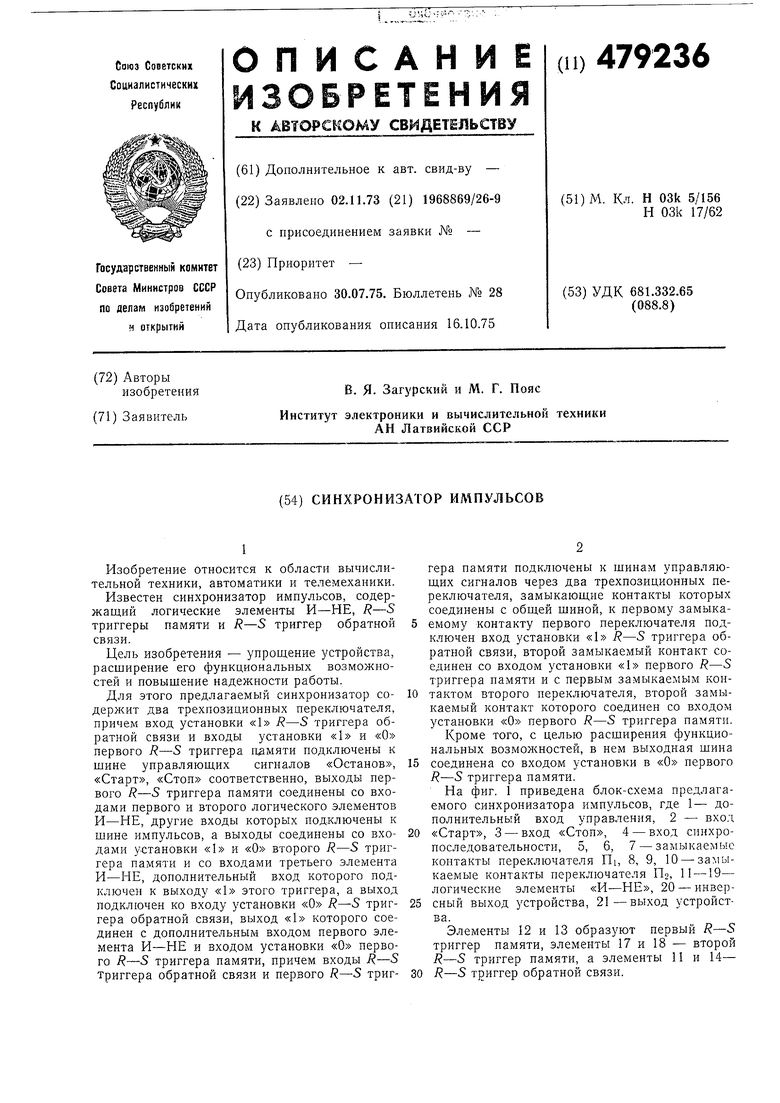

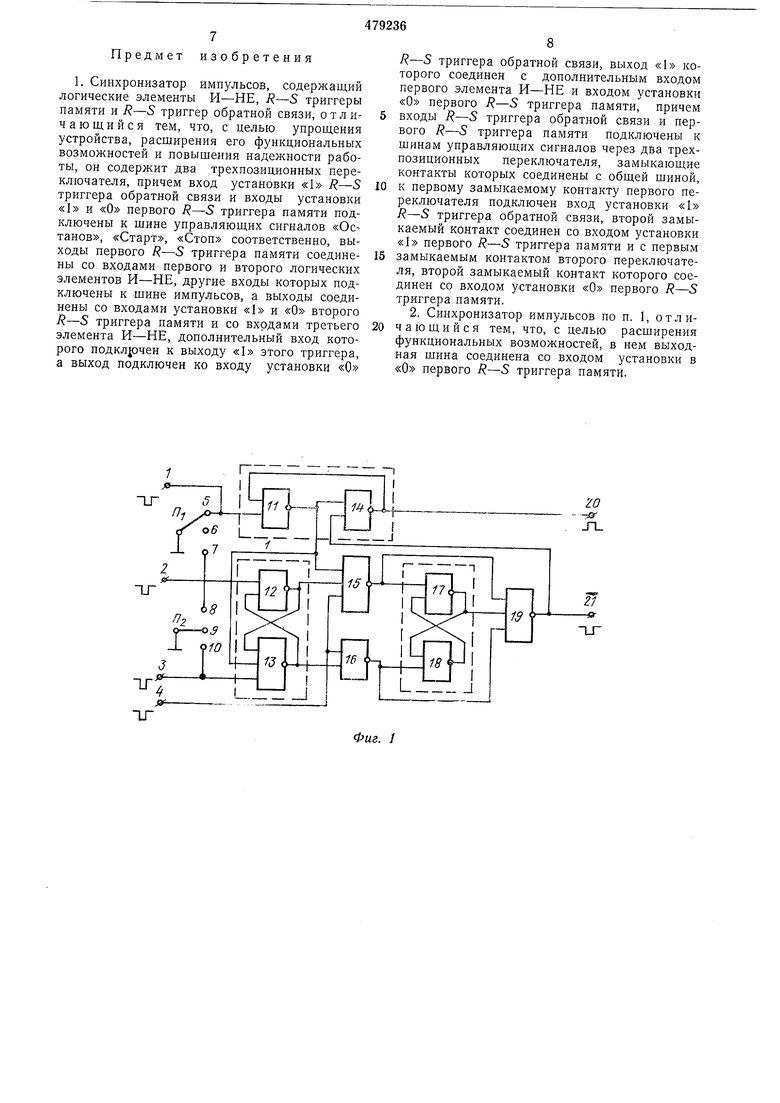

На фиг. 2 изображены временные диаграммы работы устройства в режиме бесконтактного выделения части синхропоследовательности с учетом собственных задержек логических элементов; на фиг. 3 - временные диаграммы работы устройства в режиме контактного выделения одиночного импульса входной последовательности с учетом собственных задержек логических элементов.

Устройство позволяет осуществить следующие режимы бесконтактного и контактного управления при выделении части произвольной последовательности импульсов; бесконтактное выделение части входной последовательности по сигналам «Старт и «Стоп ; бесконтактное выделение одного импульса, пришедшего вслед за импульсом управления; бесконтактное выделение произвольного числа импульсов в зависимости от длительности управляющего сигнала по входу «Старт ; режим комбинированного бесконтактного управления по условному входу 1 и входу «Старт при выделении одного или нескольких импульсов; выделение одного импульса входной последовательности по сигналу контактного переключателя; выделение части входной последовательности импульсов по сигналу контактного переключателя.

Для осуществления бесконтактного управления при выделении пачки синхроимпульсов переключатель Hi необходимо установить в положение 5, а переключатель 1 - в положение 9, при этом вход 2 соединяется с источником «Старт -импульсов, а входы 3 - с источником «Стоп -импульсов. При поступлении «Старт -импульса во время действия импульса входной последовательности (момент времени ti на фиг. 2) первый триггер памяти изменяет свое состояние. На выходе элемента высокий уровень напряжения, соответствующий логической единице «1, а элемент 13 - в состоянии логического нуля «О (низкий уровень выходного напряжения). По окончании входного импульса, на выходе элемента 15 появляется инвертированная входная последовательность импульсов, так как элемент 12 сохраняет состояние логической единицы до прихода «Стоп -импульса; на выходе элемента 13 - низкий уровень напряжения (логический «О). Первый же сигнал, соответствующий низкому уровню на выходе элемента 15, устанавливает второй R--S триггер памяти в «1 (элемент 17-«1, элемент 18- «О). Следующий уровень логической единицы на выходе элемента 15, соответствующий отрицательному импульсу на входе 4 вызывает появление «О на выходе элемента 19. Таким образом, до прихода «Стоп -импульса на выходе устройства 21 формируется последовательность импульсов, выделяемая из входной синхропоследовательности. Замкнутый переключателем П1 на землю контакт 5 обеспечивает наличие логической «1 на выходе элемента И. На выходе элемента 14 формируется последовательность положительных импульсов, соответствующих отрицательным импульсам на выходе 21.

При поступлении «Стоп -импульсов во время действия импульса входной последовательности 4 (момент времени t на фиг. 2) первый R-5 триггер памяти меняет свое состояние (элемент 12 - «О, элемент 13 - «1), что, однако, не вызывает изменения состояния элементов 15 и 16, которые находятся в «1 и

удерживаются в ней нулевым уровнем входного сигнала. Приходящий единичный уровень входной последовательности 4 (пауза) вызывает появление «О на выходе элемента 16, что обусловливает установку второго R-S

триггера памяти в «О (элемент 17 - «О, элемент 18 - «1) и одновременно блокирование элемента 19 для дальнейшего прохождения имлульсной последовательности на выходы устройства.

При поступлении «Старт -импульса во время паузы между импульсами входной последовательности 4 (момент времени з на фиг. 2) первый R-5 триггер памяти устанавливается в «1 (элемент 12 - «1, элемент 13 - «О),

вызывая появление «О на выходе элемента 15, который устанавливает второй триггер памяти в «1 (элемент 17 - «1, элемент

18- «О), подготавливая тем самым элемент

19к прохождению импульсной последовательности на выходы устройства 20 и 21.

При поступлении «Стоп -импульса во время паузы между импульсами последовательности 4 (момент времени 4 на фиг. 2) первый R-5 триггер памяти изменяет свое состояние

(элемент 12 - «О, элемент 13 - «1), вызывая появление «О на выходе элемента 16, который устанавливает второй R-5 триггер памяти в «О (элемент 17 - «О, элемент 18 - «1) и одновременно запрещает дальнейшее

прохождение импульсов на выходы устройства через элемент 19.

Таким образом, при воздействии «Старт импульса на выходе устройства формируются целые импульсы, начиная со следующего после

момента появления «Старт -импульса. При приходе «Стоп -импульса во время действия входного импульса формирование выходного импульса продолжается до образования целого импульса. Воздействие «Стоп -импульса

во время паузы входной импульсной последовательности соответствует окончанию формирования последовательности выходных импульсов. Правильная и надежная работа устройства

(отсутствие неполноценных импульсов) обеспечивается при любых комбинациях распределения во времени сигналов управления и синхропоследовательности, например, управление устройством сигналами с частичным перекрытием по временной оси (момент времени и на фиг. 2). В таком случае момент окончания действия «Старт -сигнала воспринимается устройством как момент прихода «Стоп сигнала (момент времени 4-ti на фиг. 2).

Для выделения одного синхроимпульса управление необходимо осуитествлять по входу 2 импульсами, длительность которых меньше длительности синхроимпульсов. Выход 21 соединен со входом 3.

Для осуществления бесконтактного выделения I или (n-fl)-oro импульса сигналом управления по входу 2 в зависимости от его длительности, выход устройства 21 замыкается на вход 3, переключатели остаются в прежнем положении, т. е. IIi-5, П2-9.

Для осуществления режима комбинированного бесконтактного управления переключатель П необходимо установить в положение 6, а переключатель По в положение 9. На УСЛОВНЫЙ вход 1 поступает импульсный сигнал, который изменяет состояние R-S триггера обратной связи. Приходящий ИМПУЛЬС по входу 2 устанавливает первый R-S триггер памяти в «1 (элемент 12 - «1, элемент 13 - «О), разрешая тем самым прохождение ИМПУЛЬСНОЙ последовательности 4 на выход устройства 21. При поступлении импульса по входу 2 раньше прихода сигнала по ВХОДУ 1, количество выходных импульсов определяется длительностью импульса по входу 1. При поступлении импульса по входу 2 во время действия импульса на входе 1, количество выходных импульсов определяется длительностью временного интервала между началом импульса по входу 2 н конном импульса по входу 1. При поступлении импульса по входу 2 после окончания импульса по входу 1 на выходе устройства появится один импульс синхропоследовательности.

Такой режим позволяет реализовать условное управление, что расширяет функпиональные возможности предлагаемого устройства.

Появляющийся на выходе 21 импульс поступает на вход 3 и после окончания управляюшего импульса на входе 2 вызывает установку первого R-S триггера памяти в «О (момент времени / на фиг. 2) аналогично приходу «Стоп -импульса во время действия импульса (момент времени fo на фиг. 2), рассмотренному вьгате. При подаче управляюптего импульса по длительности превосходящего длительность синхроимпульсов, на выходе устройства появляется «4-1 импульс, где п зависит от соотношения длительности управляющего сигнала и периода следования импульсов входной последовательности 4: ,74-1-й импульс возвращает первый R - S триггер памяти в исходное состояние (элемент 12 - «О, элемент 13 - «1).

Вы.ггеление одного импульса синхропоследовательности 4 по сигналу контактного переключателя Пч осуществляется переключ ниелт его из положения 5 в положение 7. Переключатель По необходимо установить в положение 9. Исходное состояние (фиг. 3) триггеров следующее: первый R-S триггер памяти в

«О (элемент 12 - «О, элемент 13 - «1), второй R-S триггер палтяти в «О (элемент 17-«О, элемент 18 - «1), R-S триггер обратной связи в «1 (элемент П-«1, элемент 14 - «О). В момент fs. (фиг. 3) начинается размыкание подвижного контакта переключателя с контактом 5 с неизбежным дребезгом, возникающим из-за неидеальности контактной системы. Замыкание подвижного

контакта П с контактом 7 (момент времени U на фиг. 3) устанавливает первый R-S триггер памяти в «1 (элемент 12 - «1, элемент 13 - «О), причем дальнейший «дребезг не оказывает влияния на состояние триггера. До

появления выходного импульса устройство работает аналогично рассмотренному выше. ПоЯВЛЯЮЩ.ИЙСЯ на выходе 21 импульс устанавливает R-S триггер обратной связи в «О (элемент И -«О, элемент 14 - «). Уровень логического нуля - «О на выходе элемента 11 блокирует элемент 15 от дальнейщего прохождения импульсной последовательности, в то же время вызывая появление выходе элемента 13. Уровень логической «1 сигнала

входной последовательности 4 (пауза) обусловливает появление «О на выходе элемента 16, в результате чего устанавливается второй R-S триггер памяти в «О (элемент 17 - «О, элемент 18 - «1) и блокируется элемент 19

для дальнейшего прохождения импульсов на выход устройства. Размыкание переключателем П) контакта 7 (момент времени fn на фиг. 3) вызывает окончательную установку первого R-S триггера в исходное состояние

(элемент 12 - «О, элемент 13 - «1) после окончания «дребезга. Замыкание переключателем П) контакта 5 (момент времени на фиг. 3) вызывает установку R-S триггера обратной связи в исходное состояние (элемент 11-«1, элемент 14 - «О), что снимает блокирующий «О со входов элементов 15 и 13, независимо от последующего «дребезга. Таким образом, с возвратом переключателя П в положение 5 устройство полностью подготавливается к повторной отработке команды пуска.

Для контактивного управления при выделении «пачки синхроимпульсов переключатель П) необходимо установить в положение 5, переключатель П последовательно переключается из положения 10 в положение 8, что воспринимается устройством как команда «Старт, и обратно из 8 в 10 - команда «Стоп. Излтенение состояния первого R-S

триггера памяти происходит с первого же замыкания контактов, что обеспечивает полное исключение влияния последуюш,его «дребезга на одном из контактов переключателя. В остальном работа устройства аналогична рассмотренному выще режиму бесконтактного выделения «пачки сиихроттмпульсов, при этом с выхода 2 снимается последовательность отрипательных импульсов, а с выхода 20 - последовательность положительных импульсов.

Предмет изобретения

1. Синхронизатор импульсов, содержащий логические элементы И-НЕ, R-5 триггеры памяти и R-5 триггер обратной связи, отличающийся тем, что, с целью упрощения устройства, расширения его функциональных возможностей и повышения надежности работы, он содержит два трехпозиционных переключателя, причем вход установки «1 К-5 триггера обратной связи и входы установки «I и «О первого R-5 триггера памяти подключены к шине управляющих сигналов «Останов, «Старт, «Стоп соответственно, выходы первого R-S триггера памяти соединены со входами первого и второго логических элементов И-НЕ, другие входы которых подключены к шине импульсов, а выходы соединены со входами установки «1 и «О второго R-5 триггера памяти и со входами третьего элемента И-НЕ, дополнительный вход которого подкл очен к выходу «Ь этого триггера, а выход подключен ко входу установки «Q

R-5 триггера обратной связи, выход «1 которого соединен с дополнительным входом первого элемента И-НЕ и входом установки «О первого R-S триггера памяти, причем

входы R-5 триггера обратной связи и первого R-5 триггера памяти подключены к шинам управляющих сигналов через два трехпозиционных переключателя, замыкающие контакты которых соединены с общей шиной,

к первому замыкаемому контакту первого переключателя подключен вход установки «1 R-5 триггера обратной связи, второй замыкаемый контакт соединен со входом установки «1 первого R-5 триггера памяти и с первым

замыкаемым контактом второго переключателя, второй замыкаемый контакт которого соединен со входом установки «О первого R-5 триггера памяти. 2. Синхронизатор импульсов по п. 1, отличающийся тем, что, с целью расширения функциональных возможностей, в нем выходная шина соединена со входом установки в «О первого R-5 триггера памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Синхронизатор импульсов | 1976 |

|

SU588622A1 |

| Устройство для подографии | 1981 |

|

SU995739A1 |

| Устройство управления электрофицированной дождевальной машиной | 1988 |

|

SU1547783A1 |

| Устройство для измерения временныхпАРАМЕТРОВ иМпульСОВ | 1979 |

|

SU842614A1 |

| СПОСОБ ПОМОЩИ ВОДИТЕЛЯМ ПРИ ПЕРЕСТРОЕНИЯХ И СИСТЕМА ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2016 |

|

RU2646782C2 |

| ПЕРЕКЛЮЧАТЕЛЬ С ЗАПОМИНАНИЕМ СИГНАЛА УПРАВЛЕНИЯ | 1990 |

|

RU2018204C1 |

| Устройство управления трехфазным асинохронным электродвигателем криогенной системы с защитой от обрыва фазы | 1989 |

|

SU1791893A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ИМПУЛЬСОВ | 2004 |

|

RU2256288C1 |

| УСТРОЙСТВО ДЛЯ ОБУЧЕНИЯ ОСНОВАМ ВЫЧИСЛИТЕЛЬНОЙ ТЕХНИКИ | 1991 |

|

RU2011230C1 |

| Устройство для управления позиционированием в ноль исполнительных органов станка | 1988 |

|

SU1571549A1 |

Фиг. 1

Авторы

Даты

1975-07-30—Публикация

1973-11-02—Подача