Изобретение относится к учебно-лабораторному оборудованию и может быть использовано в учебном процессе, а также в конструкторских бюро для моделирования и откладки дискретных устройств, построенных на интегральных микросхемах.

Известно устройство для обучения основам вычислительной техники, содержащее пульт оператора, счетчик, дешифратор, распределитель импульсов, коммутатор и сдвигающий регистр.

Недостатком такого устройства являются низкие дидактические возможности, так как оно не позволяет наглядно исследовать нерегулярные дискретные устройства, получаемые в результате логического синтеза.

Известна моделирующая установка, состоящая из генератора одиночных импульсов и генератора непрерывной последовательности импульсов, пульта оператора, входного регистра, наборного поля, модулей логических элементов и элементов памяти, а также индикаторов.

Недостатком такой установки являются низкие дидактические возможности за счет отсутствия индикации последующих и предыдущих состояний элементов памяти.

Известно также устройство для обучения основам вычислительной техники, содержащее пульт оператора, блок предъявления информации (внешних входных сигналов), коммутатор, наборное поле, логические элементы и блоки памяти. Пульт оператора содержит генератор одиночных импульсов, генератор непрерывной последовательности импульсов, генератор нуля, переключатель, управляющую клавиатуру и и регистр. Логический элемент содержит два коммутатора, логический узел и коммутатор. Блок памяти содержит два коммутатора, элемент памяти, два индикатора и узел прогнозирования, который содержит инвертор, два элемента И и элемент ИЛИ.

Недостатком такого устройства являются низкие дидактические возможности, а также большие затраты времени на анализ синтезированного дискретного автомата.

Наиболее близким по технической сущности к предлагаемому является устройство для обучения основам вычислительной техники, содержащее пульт оператора, первый выход которого соединен с соответствующими входами блока предъявления информации и наборного поля, второй выход - с соответствующим входом наборного поля, а выходы группы - с соответствующими входами группы блока предъявления информации и с соответствующими входами первой группы наборного поля, входы второй группы и выходы первой группы которого являются соответствующими входами и выходами устройства, элемент памяти, узел индикации и элемент 2И-ИЛИ, причем выходы второй группы наборного поля соединены с соответствующими входами элемента памяти, единичный выход которого соединен с первым входом узла индикации и первым входом наборного поля, а нулевой выход подключен к второму входу наборного поля, выход элемента 2И-ИЛИ соединен с вторым входом узла индикации и третьим входом наборного поля, а первый, второй, третий и четвертый входы - соответственно с единичным и нулевым выходами и I- и К-входами элемента памяти, два элемента НЕ и шесть элементов И-НЕ, причем входы первого и второго элементов НЕ соединены с I- и К-входами элемента памяти соответственно, первые входы первого и четвертого элементов И-НЕ соединены с I- и К-входами элемента памяти соответственно, первые входы второго и третьего элементов И-НЕ соединены с выходами первого и второго элементов НЕ соответственно, вторые входы первого и третьего элементов И-НЕ соединены с единичным выходом элемента памяти, нулевой выход которого подключен к вторым входам второго и четвертого элементов И-НЕ, выходы первого и второго элементов И-НЕ соединены с первым и вторым входами пятого элемента И-НЕ соответственно, а выходы третьего и четвертого элементов И-НЕ подключены к первому и второму входам шестого элемента И-НЕ соответственно, выходы пятого и шестого элементов И-НЕ соединены с третьим и червертым входами узла индикации соответственно.

Недостатком такого устройства являются низкие дидактические возможности, а также большие затраты времени на анализ синтезированного дискретного автомата.

Цель изобретения - повышение быстродействия устройства с сокращением затрат времени на анализ дискретного автомата, описываемого вырожденными рекуррентными булевыми функциями и расширение его дидактических возможностей.

Это достигается тем, что в устройство для обучения основам вычислительной техники, содержащее пульт оператора, первый выход которого соединен с соответствующими входами блока представления информации и наборного поля, второй выход - с соответствующим входом наборного поля, а выходы группы - с соответствующими входами группы блока предъявления информации и с соответствующими входами первой группы наборного поля, входы второй группы и выходы первой группы которого являются соответствующими входами и выходами устройства, при этом пульт оператора содержит три генератора, переключатель рода работ, управляющую клавиатуру и регистр, причем выход первого генератора подключен к первому входу переключателя рода работ, к второму входу которого подключен выход второго генератора, выход переключателя рода работ является первым выходом пульта оператора, выход третьего генератора является вторым выходом пульта оператора, выходами группы которого являются прямые выходы соответствующих разрядов регистра, входами которых являются выходы управляющей клавиатуры, элемент памяти, узел индикации и элемент 2И-ИЛИ, причем выходы второй группы наборного поля соединены с соответствующими входами элемента памяти, единичный выход которого соединен с первым входом узла индикации и третьим входом наборного поля, а нулевой выход подключен к четвертому входу наборного поля, выход элемента 2И-ИЛИ соединен с вторым входом узла индикации и пятым входом наборного поля, а первый, второй, третий и четвертый входы соответственно с единичным и нулевым выходами и I- м К-входами элемента памяти, первый и второй входы группы узла индикации соединены с первым и вторым входами третьей группы входов наборного поля, согласно изобретению введены счетчик импульсов, две группы индикаторов и регистр, причем счетный вход счетчика импульсов соединен с выходом переключателя рода работ, а вход обнуления - с шестым входом наборного поля, выходы счетчика импульсов соединены с входами соответствующих индикаторов первой группы, информационный вход, входы сдвига вправо и обнуления регистра соединены с единичным выходом, входами синхронизации и обнуления элемента памяти соответственно, а выходы группы предыдущих состояний - с соответствующими входами группы узла индикации, К-2-входы группы которого соединены с соответствующими входами третьей группы наборного поля.

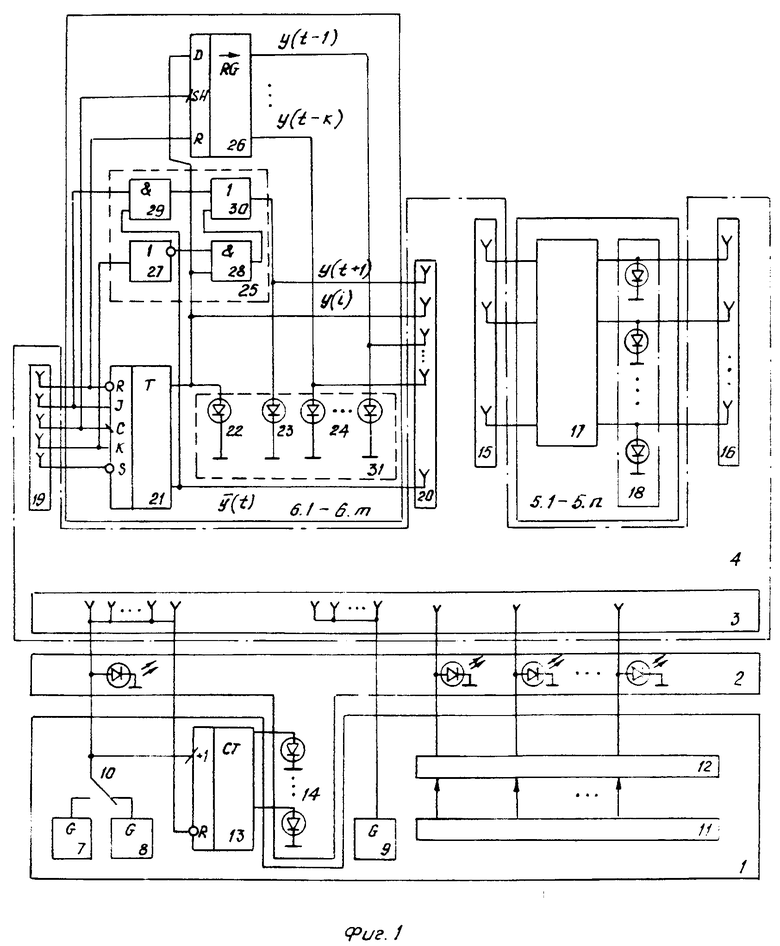

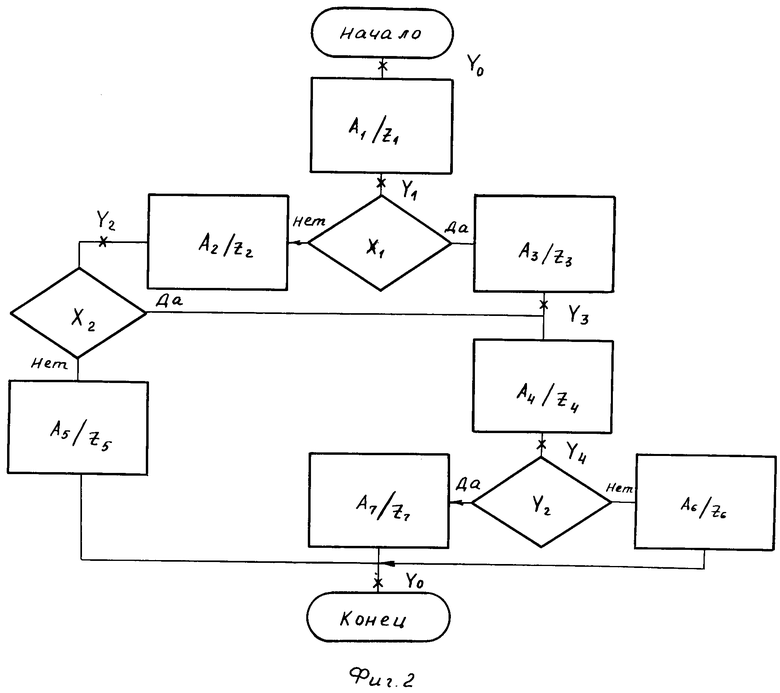

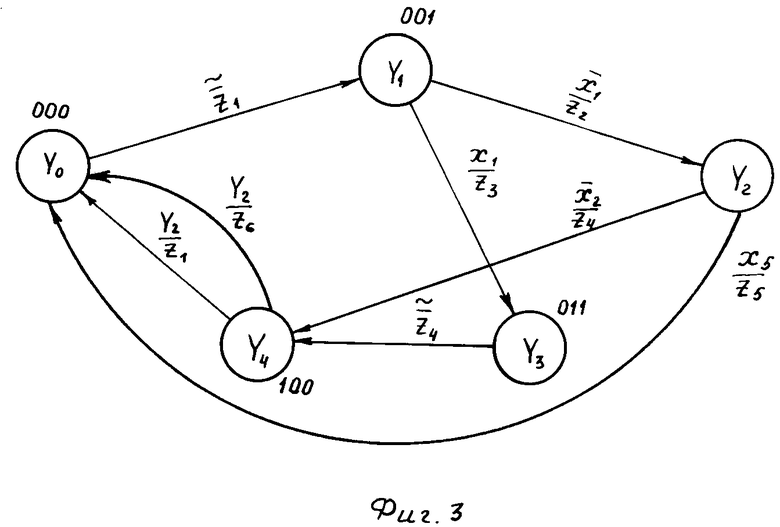

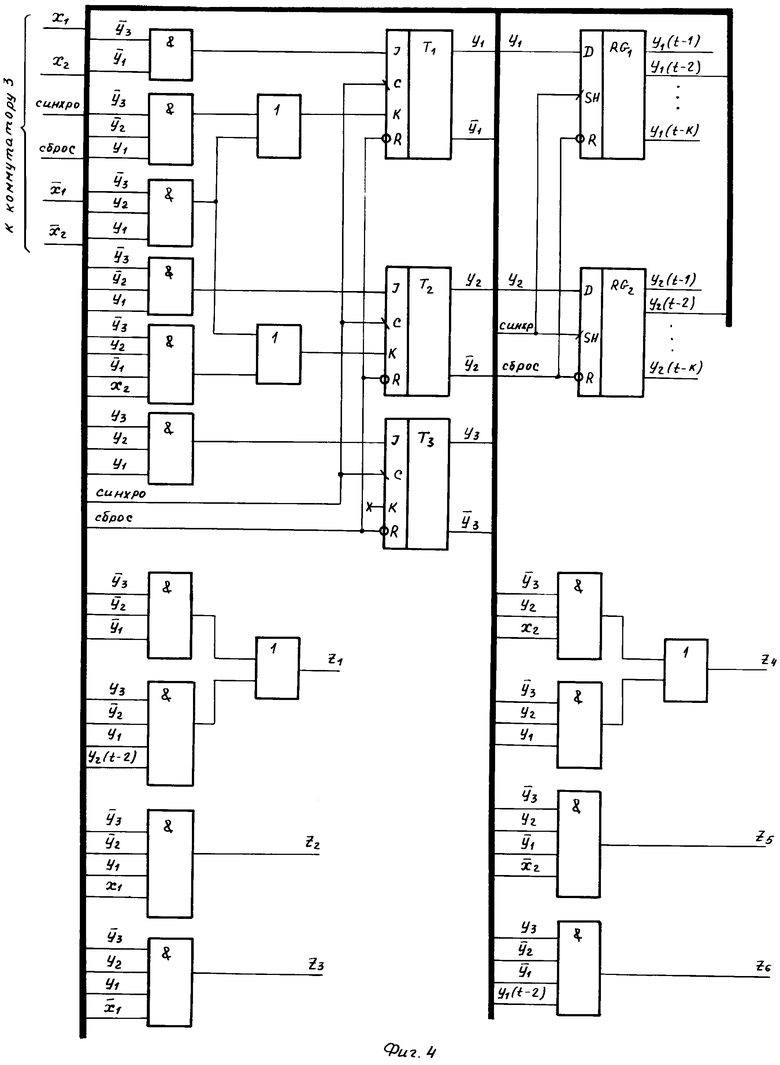

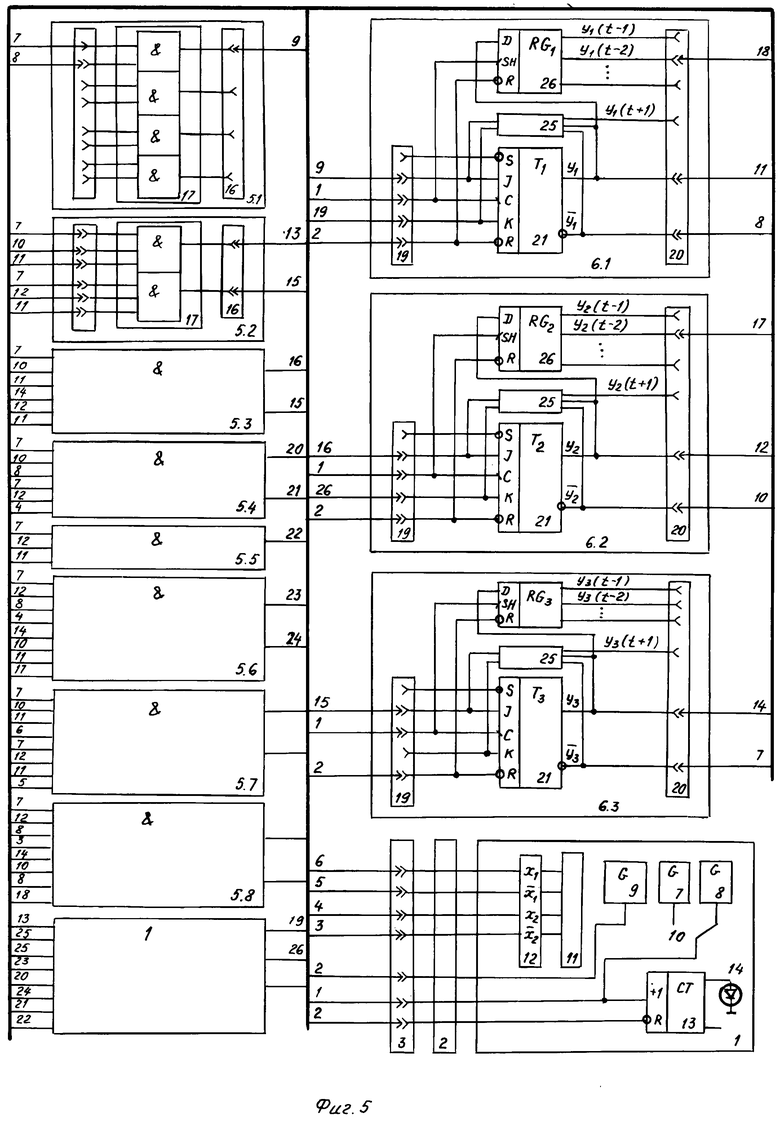

На фиг. 1 изображена функциональная схема предлагаемого устройства; на фиг. 2 - отмеченная граф-схема алгоритма работы синтезированного дискретного устройства, выходные сигналы которого зависят не только от текущих внутренних состояний и текущих состояний входных сигналов, но и от предыдущих состояний, т. е. от того каким путем автомат попал в это состояние; на фиг. 3 - граф автомата, по условиям задания которого описывается дискретное устройство, синтезированное обучаемым; на фиг. 4 - функциональная схема дискретного автомата, синтезированная обучаемым; на фиг. 5 - связи между отдельными узлами и блоками, необходимые для нормального функционирования устройства, объединяющие их в единое техническое решение.

Устройство для обучения основам вычислительной техники содержит пульт 1 оператора, блок 2 предъявления информации (внешних входных сигналов), коммутатор 3, наборное поле 4, логические элементы 5 и блоки 6 памяти.

Пульт 1 содержит генератор 7 одиночных импульсов, генератор 8 (непрерывной последовательности импульсов), генератор 9 (нуля), переключатель 10 рода работ, управляющую клавиатуру 11, регистр 12, счетчик 13 импульсов и группу индикаторов 14.

Логический элемент 5 содержит коммутаторы 15 и 16, логический узел 17 и индикатор 18.

Блок 6 содержит коммутатор 19 и 20, элемент 21 памяти, индикаторы 22 и 23, группу индикаторов 24, элемент 2И-ИЛИ 25 и регистр 26.

Элемент 25 содержит инвертор 27, элементы И 28 и 29 и элемент ИЛИ 30.

Индикаторы 22 и 23 и группа индикаторов 24 конструктивно объединены в узел 31 индикации. Группа индикаторов 14 объединена в блоке 2. Коммутаторы 3, 15, 16, 19 и 20 объединены в наборном поле 4.

Первый выход пульта 1 оператора соединен с соответствующими входами блока 2 предъявления информации и наборного поля 4, второй выход - с соответствующими входами наборного поля 4, а выходы группы - с соответствующими входами группы блока 2 и с соответствующими входами первой группы наборного поля 4, входы второй группы и выходы первой группы которого являются соответствующими входами и выходами устройства. Выход первого генератора 17 подключен к первому входу переключателя 10 рода работ, к второму входу которого подключен выход второго генератора 8. Выход переключателя 10 является первым выходом пульта 1 оператора. Выход третьего генератора 9 является вторым выходом пульта 1 оператора, выходами группы которого являются прямые выходы соответствующих разрядов регистра 12, входами которых являются выходы управляющей клавиатуры 11. Выходы второй группы наборного поля 4 соединены с соответствующими входами элемента 21 памяти, единичный выход которого соединен с первым входом узла 31 индикации и с третьим входом наборного поля 4, а нулевой выход подключен к четвертым входам наборного поля 4. Выход элемента 2И-ИЛИ 25 соединен с вторым входом узла 31 индикации и пятым входом наборного поля 4, а первый, второй, третий и четвертый входы - соответственно с единичным и нулевым выходами и I- и К-входами элемента 21 памяти. Первый и второй входы группы узла 31 индикации соединены с первым и вторым входами третьей группы входов наборного поля 4. Счетный вход счетчика 13 импульсов соединен с выходом переключателя 10 рода работ, а вход обнуления - с шестым входом наборного поля 4. Выходы счетчика 13 импульсов соединены с входами соответствующих индикаторов 14 первой группы. Информационный вход, входы сдвига вправо и обнуления регистра 26 соединены с единичным выходом, входами синхронизации и обнуления элемента 21 памяти соответственно, а выходы группы предыдущих состояний - с соответствующими входами группы 24 узла 31 индикации, К-2-входы группы которого соединены с соответствующими входами третьей группы наборного поля 4.

Пульт 1 оператора предназначен для управления работой устройства для обучения основам вычислительной техники и конструктивно выполнен в виде пластикового корпуса. Блок 2 предназначен для отображения только входных сигналов и сигналов синхронизации, т. е. внешних входных сигналов моделируемых конечных автоматов, и может быть выполнен, например, на светодиодах АЛС102. Коммутатор 3 предназначен для коммутации входных сигналов и сигналов синхронизации и может быть выполнен, например, на контактах штепсельных разъемах. Наборное поле 4 предназначено для размещения и подачи питания на элементы 5 и блоки 6 и может быть реализовано на контактах штепсельных разъемов, к которым подключаются вилки элемента 5 и блока 6. Логические элементы 5 предназначены для размещения коммутаторов, логических узлов и индикаторов и конструктивно выполнены в виде пластикового корпуса, снабженного, кроме контактов входного и выходного полей, клеммами подачи питания, с помощью которых и производится установка их на наборное поле 4, имеющее специальные гнезда. Количество и номенклатура элементов зависит от конкретных задач обучения. На верхней крышке модуля изображено изображение конкретной, размещенной в нем, микросхемы узла. Блоки 6 предназначены для размещения коммутаторов, элементов памяти, элемента 25, регистра 26 и узла 31 индикации и конструктивно выполнены аналогично логическим элементам 5.

Генератор 7 предназначен для формирования одиночных импульсов и их подачи на элементы 21 памяти и может быть реализован, например, в виде кнопки без фиксации, подключенной к шине "-", а выходным контактом - к входному контакту переключателя 10. Генератор 8 предназначен для формирования прямоугольных импульсов амплитудой, равной напряжению логической "1" и может быть реализован, например, на микросхеме 155ЛА3. Генератор 9 предназначен для установки элементов 19 по входам в состояние, соответствующее коду первой строки таблицы переходов-выходов, и может быть реализован на ограничительном резисторе, подсоединенном одним концом к шине "-", а другим - к выходу пульта 1 оператора.

Переключатель 10 предназначен для переключения режима проверки выполнения заданных условий работы синтезированного автомата с ручного на автоматический и обратно и может быть реализован, например, на микротумблере МТ 1. Управляющая клавиатура 11 предназначена для задания входного сигнала и представляет собой регистр кнопок с фиксацией. Регистр 12 предназначен для устранения дребезга контактов управляющей клавиатуры 11 и содержит триггеры по числу разрядов управляющей клавиатуры 11. Счетчик 13 импульсов предназначен для подсчета количества тактов синхронизации и может быть выполнен, например, на микросхеме 155ИЕ2. Группа индикаторов 14 предназначена для индикации количества поданных тактов синхронизации. Количество индикаторов должно быть не меньше ] log2K[, где К - максимально возможное количество тактов предыдущих состояний. Индикаторы могут быть реализованы, например, на светодиодах АЛС102.

Коммутатор 15 предназначен для коммутации логических элементов при решении задачи логического синтеза дискретных устройств и может быть реализован, например, на гнездах штепсельных разъемов. Коммутатор 16 предназначен для коммутации выходов логических узлов 15 при наборе функциональной схемы и может быть релиазован, например, на гнездах штепсельных разъемов.

Логический узел 15 предназначен для набора логического преобразователя исследуемого дискретного устройства, представляющего собой совокупность комбинационных бесконтактных дискретных элементов. Собранный логический преобразователь служит для управления элементами памяти дискретного устройства и формирования внешних выходных сигналов. Логический узел может быть реализован, например, на одной из интегральных микросхем 155ЛА1, 155ЛА2, 155ЛА3, 155ЛР1, 155ЛР2 и др.

Индикатор 18 предназначен для отображения выходного состояния каждого из узлов 17 и может быть реализован, например, на светодиодах АЛС102.

Коммутатор 19 предназначен для коммутации входов элементов памяти 21 при наборе разработанной функциональной схемы и может быть реализован, например, на гнездах штепсельных разъемов. Коммутатор 20 предназначен для коммутации выходов текущего, прогнозируемого и предыдущих состояний элементов 21 памяти и может быть реализован, например, на гнездах штепсельных разъемов. Коммутаторы 3, 15, 16, 19 и 20 конструктивно могут быть выполнены в виде гнезд штепсельных разъемов, например, типа 12РБ60-А, В и проводов линии связи, к концам которых припаяны штыри.

Элемент 21 памяти предназначен для реализации разработанной функциональной схемы. В качестве элемента памяти 21 можно использовать, например, IK-триггер 155ТВ1.

Индикатор 22 предназначен для отображения единичного состояния элементов 21 памяти в текущем такте и может быть реализован, например, на светодиоде АЛС102. Индикатор 23 предназначен для отображения единичного состояния элементов 21 памяти в прогнозируемом (следующем) такте и может быть реализован, например, на светодиоде АЛС102.

Группа индикаторов 24 предназначена для индикации предыдущих состояний элементов 21 памяти и может быть реализована, например, на светодиодах АЛС102. Количество индикаторов должно быть не менее К-максимально возможных тактов предыдущих состояний исследуемых дискретных автоматов.

Элемент 2И-ИЛИ 25 предназначен для прогнозирования состояния элементов 21 памяти. Регистр 26 предназначен для запоминания предыдущих состояний элемента 21 памяти и может быть реализован, например, на микросхемах типа 155ИР13. Инвертор 27 предназначен для инвертирования сигнала с входа элемента 21 памяти. Элемент И 28 предназначен для логического умножения сигналов, поступающих с выходов инвертора 27 и элемента 21 памяти. Элемент 29 предназначен для логического умножения сигналов, поступающих с выходов инвертора 27 и элемента 21 памяти. Элемент ИЛИ 30 предназначен для логического сложения сигналов, поступающих с выходов элементов И 28 и 29.

Узел 31 индикации конструктивно объединяет индикаторы 22. . . 24 отображающие состояния элемента 21 памяти в текущем, следующем и предыдущих тактах.

Связи между отдельными узлами и блоками устройства осуществляются гибкими проводниками, к концам которых припаяны штыри (ответная часть) от тех же разъемов, например, типа 12РБ60-А, В, которые вводятся в гнезда коммутаторов 3, 15, 16, 19 и 20 в соответствии с конкретной функциональной схемой, разработанной обучаемым. Например, обучаемый синтезировал функциональную схему дискретного автомата, приведенную на фиг. 3. Тогда связи между отдельными узлами и блоками, необходимые для нормального функционирования устройства и объединяющие их в единое техническое решение, принимают вид, представленный на фиг. 4. Все связи на фиг. 4 между коммутаторами представляют собой гибкие соединительные проводники.

Таким образом, после получения функциональной схемы моделируемого дискретного автомата устройство объединяется в единое техническое решение посредством соединения необходимых коммутаторов, необходимых элементов памяти и логических элементов гибкими проводниками.

Устройство для обучения основам вычислительной техники работает следующим образом:

Обычный режим работы.

Обучаемый, решая задачу логического синтеза функциональной схемы по заданным условиям работы, набирает ее на наборное поле 4 из элементов 5 и блоков 6 с помощью соединительных проводов, соединяющих коммутаторы 3, 15, 16, 19 и 20 в соответствии с полученной функциональной схемой.

Для построения математической модели синтезированного автомата обучаемый при помощи генератора 9 нуля устанавливает элементы 21 по входам в состояние, соответствующее коду первой строки таблицы переходов-выходов. Это состояние в двоичном коде отображается на индикаторах 22. После чего устанавливает счетчик 13 импульсов и элемента 21 памяти в нулевое (исходное) состояние посредством подачи импульса от генератора 9.

Затем обучаемый подает входные сигналы при помощи управляющей клавиатуры 11, при этом регистр 12 устраняет дребезг контактов клавиатуры и воздействует через блок 2, который отображает двоичный код входного сигнала, на внешние входы автомата, подключенные к коммутатору 3. При этом элементы 25 2И-ИЛИ воспринимают входные и выходные сигналы элементов 21. Инвертор 27 инвертирует сигнал с входа элемента 21, элемент 28 производит операцию логического умножения над сигналами, поступающими с выхода инвертора 27 и выхода элемента 21. Элемент 29 производит операцию логического умножения над сигналами элемента 21. Элемент 30 производит операцию логического сложения сигналов, поступающих с выходов элементов 28 и 29.

Реализованная функция принимает значение логического "0" в том случае, если элемент 21 в последующем такте устанавливается в нулевое состояние, при этом индикатор 23 не горит, а значение логической "1" - в противном случае, при этом индикатор 23 горит. Поэтому, считывая информацию по индикаторам 23, обучаемый получает двоичную информацию, отмечаемую в каждой клетке таблицы переходов-выходов без дополнительных операций, только путем изменения комбинации входных сигналов. Это позволяет получить математическую модель синтезированного автомата, во время построения которой обучаемый производит отладку автомата, используя дополнительно индикаторы 18, отображающие выходные состояния каждого из узлов 17. Затем производится проверка выполнения заданных условий работы синтезированного автомата в синхронном ручном и автоматическом режимах, используя генератор 7 одиночных импульсов, генератор 8 и переключатель 10, подавая сигналы синхронизации на входы синхронизации элементов 21 памяти с коммутатора 3.

Таким образом, работа устройства происходит аналогично работе прототипа, однако количество поданных сигналов синхронизации отображается в двоичном коде на индикаторах 14.

Режим определения предыдущих состояний элементов памяти.

Обучаемый, например, разрабатывает отмеченную граф-схему алгоритма (фиг. 2) работы дискретного устройства, выходные сигналы которого зависят не только от текущих внутренних состояний и текущих входных сигналов, но и от предыдущих состояний, т. е. от того, каким путем автомат попадает в это состояние, граф которого приведен на фиг. 3.

Решая задачу логического синтеза функциональной схемы по заданным условиям работы, набирает ее на наборном поле 4 из элемента 5 и блока 6 с помощью гибких соединительных проводов (фиг. 5), соединяющих коммутаторы 3, 15, 16, 19 и 20 в соответствии с полученной (фиг. 4) функциональной схемой. Затем переводит в исходное состояние элемент 21 памяти, регистры 26 и счетчик 13 импульсов посредством подачи на них импульса от генератора 9 и подает входные сигналы при помощи управляющей клавиатуры, при этом регистр 12 устраняет дребезг контактов клавиатуры 11 и воздействует через блок 2, который отображает двоичный код входного сигнала, на внешние входы автомата, подключенные к коммутатору 3. После подачи каждого синхроимпульса элемент 21 памяти дискретного автомата устанавливается в некоторое новое текущее состояние, которое оценивается по высвечиванию или погасанию индикатора 22 узла 31 индикации. При этом регистр 26 запоминает предыдущее t-1 состояние, которое соответствует некоторому сигналу g(t-1), снимаемому с первого выхода группы предыдущих состояний и, если этот сигнал единичный, то высвечивается первый индикатор группы 24. Подача i-го синхроимпульса приводит к тому, что на i-м выходе группы выходов предыдущих состояний регистра 26 появляется сигнал, соответствующий t-i состоянию элемента 21 памяти (т. е. состоянию элемента памяти i тактов назад) и по результатам подсчета количества импульсов счетчик 13 высвечивает комбинацию индикаторов 14, соответствующую i в двоичном коде. При этом состояния элемента 21 памяти во всех i тактах могут быть определены обучаемым по состоянию индикаторов группы 24.

Оценка положительного эффекта, получаемого от предлагаемого устройства для обучения основам вычислительной техники, следующая.

Для набора функциональной схемы, синтезированной обучаемым, в технических средствах прототипа необходимо затратить время

T1= 4 ˙S ˙K ˙ τ , где τ - время осуществления одной коммутации;

S - количество необходимых элементов памяти;

К - количество необходимых тактов синхронизации для реализации заданной функции.

В предлагаемом устройстве для набора той же схемы необходимо время

Т2= К τ .

Тогда во времени составляет δ =  =

=  = 4S

= 4S

Кроме того, в предлагаемом устройстве обучаемый наглядно по высвечиванию или погасанию индикаторов 22 и 23 и группы 24 определяет состояние элемента 21 памяти в t, t+1 и t-i, где i= I, K тактах дискретного автомата, количество которых определяется по высвечиванию индикаторов 14 группы, что способствует более качественному усвоению изучаемого материала, т. е. световая индикация повышает дидактические возможности устройства, поскольку индикаторы, отображающие состояния элементов памяти в предыдущих тактах, физически сгруппированы в одном корпусе исследуемых элементов памяти. (56) Авторское свидетельство СССР N 1394222, кл. G 09 B 23/18, 1988.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обучения основам вычислительной техники | 1990 |

|

SU1714660A1 |

| Устройство для обучения основам вычислительной техники | 1990 |

|

SU1775728A1 |

| Устройство для обучения основам вычислительной техники | 1988 |

|

SU1564682A1 |

| Устройство для обучения основам вычислительной техники | 1990 |

|

SU1781692A1 |

| Устройство для обучения операторов | 1990 |

|

SU1746393A1 |

| Устройство для обучения основам вычислительной техники | 1986 |

|

SU1394222A1 |

| УСТРОЙСТВО ДЛЯ ВВОДА В МИКРОЭВМ ДИСКРЕТНЫХ СИГНАЛОВ | 1990 |

|

RU2007751C1 |

| Устройство для обучения | 1987 |

|

SU1543438A1 |

| Устройство для ввода в микроЭВМ дискретных сигналов | 1990 |

|

SU1789975A1 |

| СТЕНД ДЛЯ ИЗУЧЕНИЯ СРЕДСТВ ВЫЧИСЛИТЕЛЬНОЙ ТЕХНИКИ | 2002 |

|

RU2237927C2 |

Использование: обучение и отладка дискретных устройств, построенных на интегральных микросхемах. Цель: повышение быстродействия и дидактических возможностей устройства. Сущность изобретения: устройство содержит пульт оператора, блок предъявления информации, коммутатор, наборное поле, группу логических элементов, группу блоков памяти. Пульт оператора содержит генератор одиночных импульсов, генератор непрерывной последовательности импульсов, генератор, переключатель рода работ, управляющую клавиатуру, регистр, счетчик импульсов, группу индикаторов, два коммутатора, элемент памяти, два индикатора, группу индикаторов, элемент 2И-ИЛИ, регистр. 5 ил.

УСТРОЙСТВО ДЛЯ ОБУЧЕНИЯ ОСНОВАМ ВЫЧИСЛИТЕЛЬНОЙ ТЕХНИКИ, содержащее блок предъявления информации, наборное поле, элемент памяти, узел индикации, элемент 2И - ИЛИ и пульт оператора, включающий три генератора импульсов, клавиатуру и переключатель режимов работы, входы которого соединены с выходами первого и второго генераторов импульсов, выходы клавиатуры, переключателя режимов работы и третьего генератора импульсов соединены с входами блока предъявления информации и входами первой группы наборного поля, входы второй группы которого соединены с R-, J-, C-, K- и S-входами триггера, выходы которого соединены с первым и вторым входами элемента 2И - ИЛИ, третий и четвертый входы которого соединены с J- и K-входами триггера, выходы которого и выход элемента 2И - ИЛИ соединены с входами узла индикации и входами третьей группы наборного поля, отличающееся тем, что, с целью расширения дидактических возможностей устройства, в него введен регистр, а пульт оператора дополнительно содержит счетчик, выходы которого соединены с дополнительными входами блока предъявления информации, счетный вход подключен к выходу переключателя режимов работы, а вход начальной установки соединен с дополнительным входом наборного поля, сдвиговый и установочный входы регистра соединены соответственно с C- и R-входами триггера, информационный вход соединен с одним из выходов элемента памяти, а выходы соединены с дополнительными входами узла индикации, третьей группы наборного поля.

Авторы

Даты

1994-04-15—Публикация

1991-05-05—Подача