(54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| СИНТЕЗАТОР ДРОБНЫХ КОГЕРЕНТНЫХ ЧАСТОТ С ФАЗОВОЙ СИНХРОНИЗАЦИЕЙ | 1998 |

|

RU2208904C2 |

| СПОСОБ ДЛЯ ЦИФРОВОЙ СУБСТРАКЦИОННОЙ АНГИОГРАФИИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1992 |

|

RU2043073C1 |

| Устройство компенсации нелинейных искажений радиосигналов | 1988 |

|

SU1626395A2 |

| Оперативное запоминающее устройство циркуляционного типа | 1989 |

|

SU1684811A1 |

| Управляемый высоковольтный источник питания | 1984 |

|

SU1269231A1 |

| Устройство для измерения давления и температуры | 1988 |

|

SU1812462A1 |

| Цифровой формирователь частотно-модулированных сигналов с низким уровнем искажений | 2021 |

|

RU2765273C1 |

| Способ озвучивания кинофильмов и устройство для его осуществления | 1989 |

|

SU1705793A1 |

| УСТРОЙСТВО для ОБРАБОТКИ ЗАПИСЕЙ НЕПРЕРЫВНЫХ . СЕЙСМИЧЕСКИХ КОЛЕБАНИЙ | 1971 |

|

SU312224A1 |

| Устройство записи видеоинформации | 1989 |

|

SU1721840A1 |

Изобретение относится к области дискретной техники и автоматики и может быть использовано П|р-и построении устройств, .предназначенных для затоминания аналоговых сигналов (уровней постоянного напряжения).

Известно аналоговое ЗУ, содержащее .последовательно совдвненные блоК ключевых элементов и накопитель, выполненный нч ;кондепсатО|рах, блок многозначной коррекции, состоящий из задающего генератора, делителя частоты, генератора шилообразного напряжения, фазового модулятора и фазового детектора, коммутатор. Выходы коммутатора соединены с . соответствующими конденсаторами на1К01П ителя.

Однако такое ЗУ недостаточно надежно.

Целью изобретения является повышение надежности работы устройства.

Эта цель дастигает1ся тем, что в уст|ройство введены триггерный делитель частоты, форми рователь и выходная Следящая схема. Вход TpHrrepiHoro делителя частоты соединен с выходом делителя частоты блока многозначной коррекции, а выход через формирователь соединен с управляющим входом выходной следящей схемы, сигнальный вход которой соединен с выходом блока многозначной коррекции.

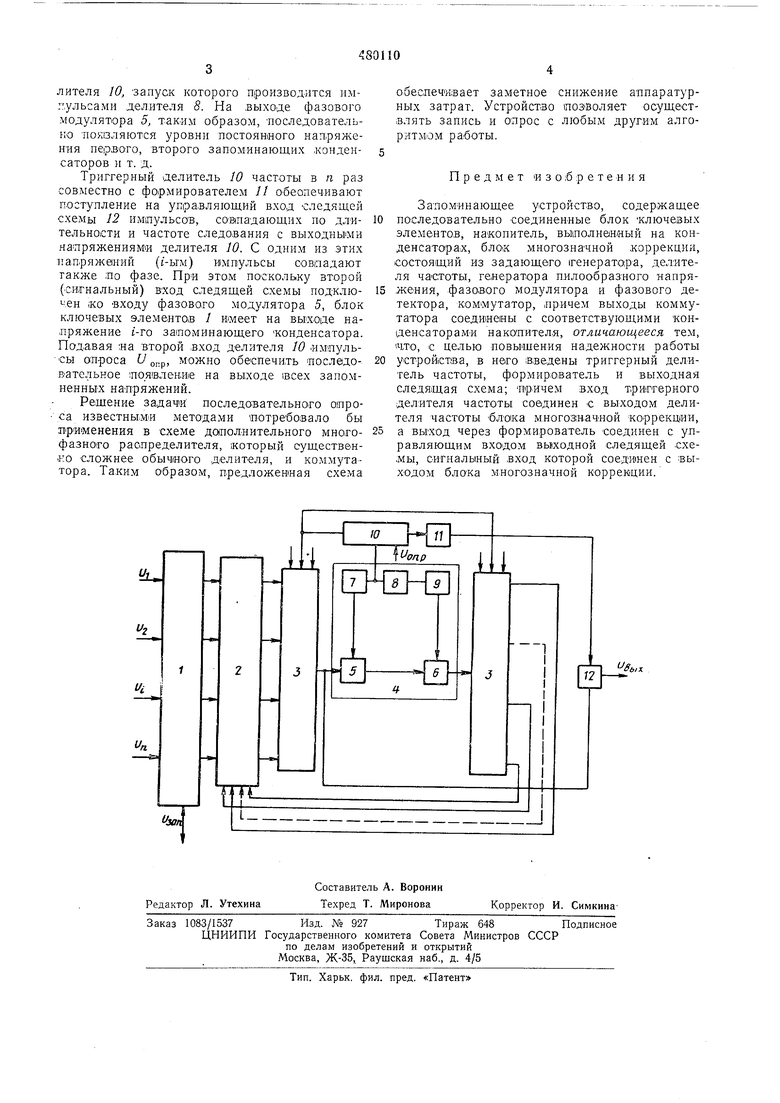

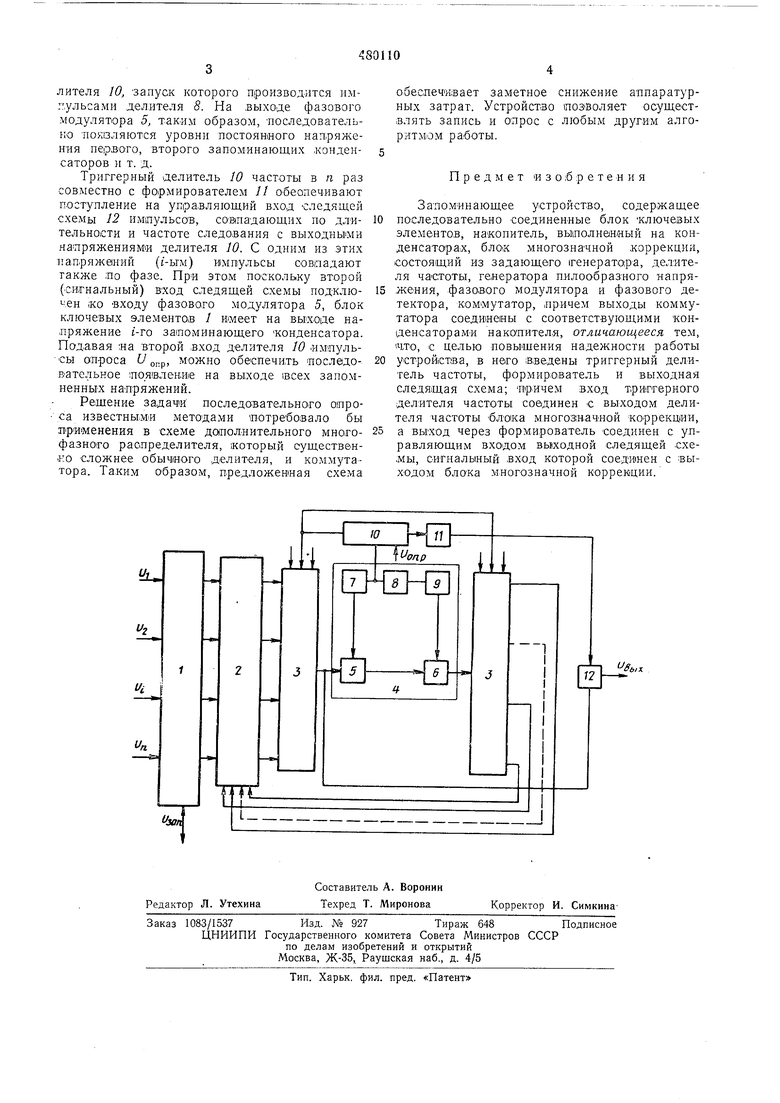

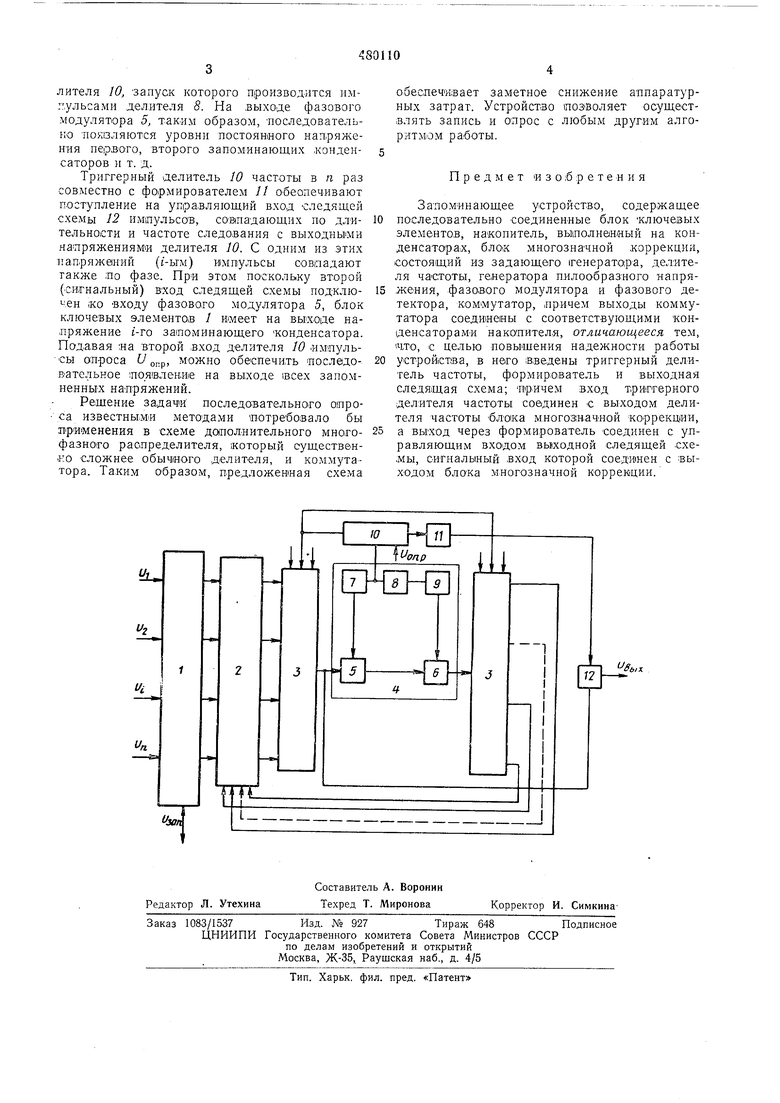

Иа чертеже представлена схема устройства. Оно содержит блок ключевых элементов /; :нако1питель 2; коммутатор 3; блок многозначной коррекции 4, содержащий фазовый МОдулятор 5, фазовый детектор б, генератор пилообразного на1пряжения 7, делитель частоты 8 и задающий генератор 9; триггерный делитель частоты 10; форМИро;ватель // и следящую схему 12.

ЗУ работает следующим образом. Запоминаемые сигналы (уровни постоянно го напряжения) Ui, f/,, поступают на п идентичных сле|дящих схем с .ключевыми элемента.ми /, к управляющим входам которых подключена шина записи. При поступлении сигнала за1писи на накопителе 2 запоминаются мгновенные значения входных напряжений. Затем сипнал заииси прекращается, и запомненная информация начпшает цир.кулировать по блоку многозначной .коррекции 4. Совместно с звеньями питания 7 и 9 J накопителем 2 этот блок образует многоустойчивые элементы с числом состояний, определяемым коэффициентом деления делителя частоты 8. Число состояний, в свою очередь, определяет точность, ic которой поддержпвается .неизменным дискретный уровень запОМненного напряжения на данном конденсаторе. Подключение блока многозначной коррекции к различным запоминающим конденсаторам на:копителя 2 осуществляется по приходе на кол мутатор 3 управляющих имлульсов от делите.тя 10, запуск которого производится им:г,ульсами делителя 8. На .выходе фазового модулятора 5, таким образом, последовательк-о появляются уровни постоянного нап.ряжения neipBOTo, второго запоминающих -конденсаторов и т. д.

Триггерный делитель 10 частоты в п раз совместно с фо1рмирователем 11 обеопечивают поступление на управляющий вход следящей схемы 12 импульсов, совпадающих по длительности и частоте следования с выходными напряжениям1И делителя 10. С одним из этих напряжений (г-ьгм) вмпульсы совпадают также ло фазе. При этом поскольку второй (сигнальный) вход следящей схемы подклю.ен ;ко входу фазового модулятора 5, блок ключевых элементов 1 иадеет на выходе налряжение i-ro заиоминающего конденсатора. Подавая на второй вход делителя 10 «моульсы олроса , можно обеспечить последеВательное .И1е на выходе всех запомненньгх напряжений.

Решение задачки последовательного oinpo са известны.М1И методами лотребовало бы применения в схеме дополнительного многофазного распределителя, который существен.но сложнее обычного делителя, и коммутатора. Таким образом, п.редложееная схема

обеспечивает заметное снижение аппаратурных затрат. Устройство позволяет осуществлять запись и олрос с любым другим алгоритмом работы.

Предмет изобретения

Запоминающее устройство, содержащее последовательно соединен ные блок ключевых элементов, накопитель, вьшолнанный на конденсаторах, блок многозначной .коррекции, состоящий из задающего 1генерато:ра, дел:ителя частоты, генератора пилообразного напряжения, фазового модулятора и фазового детектора, коммутатор, лричем выходы коммутатора соединены с соответствующими конденсатораМИ накопителя, отличающееся тем, что, с целью повышения надежности работы устройства, в него введены триггерный делитель частоты, формирователь и выходная следящая схема; причем вход триггерного делителя частоты соединен с выходом делителя частоты блока многозяачлой коррекции, а выход через формирователь соединен с управляющим входом выходной следящей схемы, сигналыный вход которой сое.димен с выходом блока многозначной коррекции.

Авторы

Даты

1975-08-05—Публикация

1972-02-23—Подача