Настоящее изобретение относится к синтезу частот, в частности к синтезаторам дробных частот с фазовой синхронизацией.

Во многих областях существует необходимость генерировать серии волн с разными частотами с сохранением фазовой когерентности между сериями волн одной и той же частоты, т.е. необходимость в сохранении одного и того же фазового сдвига относительно пилот-сигнала, что позволяет, например, отслеживать его изменения, связанные с доплеровским эффектом.

Синтезатор частот с фазовой синхронизацией состоит из ГУН (генератора, управляемого напряжением), который синхронизирован по фазе с генератором опорной частоты с помощью схемы фазовой автоподстройки частоты, которая сравнивает субгармонику выходного сигнала ГУН, полученную целочисленным или дробным делением, с сигналом генератора опорной частоты. Деление осуществляется с помощью счетчика-делителя с целочисленным коэффициентом деления, который корректируется при каждом переполнении. В результате этого начало серии волн всегда синхронизируется с переполнением счетчика-делителя, которое само происходит в течение периода сигнала генератора опорной частоты. При дробном коэффициенте деления происходит потеря когерентности, а между переполнениями счетчика-делителя и периодами сигнала генератора опорной частоты возникает фазовый сдвиг, который проявляется в течение времени, равного наименьшему общему кратному периодов сигнала ГУН и сигнала генератора опорной частоты.

В настоящее время в синтезаторах дробных частот с фазовой синхронизацией используется счетчик-делитель по крайней мере с двумя последовательными целочисленными коэффициентами деления N и N+1 и цифровой накопитель по модулю Р с целочисленным приращением K, которое меньше Р и может регулироваться. Этот цифровой накопитель, скорость которого задается выходным сигналом счетчика-делителя, используется для изменения коэффициента деления счетчика-делителя с N на N+1 и наоборот. В результате этого начало серии волн, которое совпадает с изменением приращения K, используемого для регулирования коэффициента дробного деления, может остаться незафиксированным в течение любого случайного и не уточненного переполнения счетчика-делителя в нескольких точках с разными значениями фазового сдвига в течение времени, соответствующего по крайней мере наименьшему общему кратному периодов двух сигналов. Появление такого рода случайностей ведет к потере когерентности между сериями волн одной и той же частоты, если при этом на синтезатор частоты воздействует частотный переключатель.

Один из таких синхронизаторов дробных частот с фазовой синхронизацией описан в заявке ЕР 0557799. Этот синхронизатор имеет генератор опорной частоты, генератор, управляемый напряжением, схему фазовой автоподстройки частоты, на вход которой подается сигнал от генератора, управляемого напряжением, и сигнал генератора опорной частоты и с выхода которой выдается напряжение управления генератором, управляемым напряжением, а также имеет фазовый компаратор, который соединен, во-первых, непосредственно с выходом генератора опорной частоты и, во-вторых, с выходом генератора, управляемого напряжением, через счетчик-делитель с регулируемым целочисленным коэффициентом деления, при этом этот счетчик-делитель имеет по меньшей мере два последовательных целочисленных коэффициента деления N и N+1 с возможностью переключения с одного из этих коэффициентов деления на другой, и имеет далее схему управления текущим значением коэффициента деления счетчика-делителя, осуществляющую по меньшей мере одну операцию цифрового накопления по модулю Р с целочисленным приращением K, величина которого может регулироваться и которое меньше Р, и изменяющую текущий коэффициент деления в зависимости от переполнений при выполнении операции цифрового накопления.

Задачей настоящего изобретения является создание синтезаторов дробных частот с фазовой синхронизацией, способных генерировать когерентные сигналы даже после ухода частоты.

Эта задача решается с помощью предлагаемого синтезатора дробных частот с фазовой синхронизацией, содержащего генератор опорной частоты, ГУН, схему фазовой автоподстройки частоты (ФАПЧ), на вход которой поступает сигнал ГУН и сигнал генератора опорной частоты, а на ее выходе вырабатывается сигнал управления напряжением для ГУН, и фазовый компаратор, который соединен, во-первых, непосредственно с выходом генератора опорной частоты, и, во-вторых, с выходом ГУН через счетчик-делитель с регулируемым целочисленным коэффициентом деления, причем этот счетчик-делитель имеет по крайней мере два последовательных целочисленных коэффициента деления N и N+1 и может переключаться с одного на другой, и схему для управления текущим коэффициентом деления счетчика-делителя.

Причем эта схема осуществляет по меньшей мере одно срабатывание цифрового накопителя по модулю Р с целочисленным приращением K, значение которого регулируется и меньше Р, и изменяет указанное текущее значение коэффициента деления как функцию переполнений при указанном срабатывании цифрового накопителя. Согласно изобретению синтезатор имеет схему управления текущим коэффициентом деления счетчика-делителя, содержащую по меньшей мере один счетчик по модулю Р с единичным приращением, скорость которого определяется частотой сигнала генератора опорной частоты и который используется в запоминающем устройстве для запоминания фазы для изменений в моменты синхронизации с генератором опорной частоты значения приращения K цифрового накопителя, сопровождающихся изменениями дробного коэффициента деления и одновременным сохранением для данной частоты одного и того же фазового сдвига по отношению к пилот-сигналу.

В соответствии с предпочтительным вариантом изобретения синтезатор дробных частот с фазовой синхронизацией имеет схему управления текущим коэффициентом деления его счетчика-делителя, содержащую, помимо счетчика по модулю Р с единичным приращением, умножитель по модулю Р для умножения значения, подсчитанного счетчиком по модулю Р с единичным приращением, на приращение K цифрового накопителя, компаратор, сравнивающий выходной сигнал умножителя по модулю Р с приращением K срабатывания цифрового накопителя и генерирующий в том случае, когда выходной сигнал умножителя по модулю Р окажется строго меньше значения приращения K срабатывания цифрового накопителя, сигнал переполнения, и устройство синхронизации, синхронизирующее сигнал переполнения компаратора с выходным сигналом счетчика-делителя до подачи его в счетчик-делитель в качестве команды на изменение коэффициента деления.

В одном из вариантов компаратор, сравнивающий выходной сигнал умножителя по модулю Р с приращением K цифрового накопителя, генерирует сигнал переполнения не тогда, когда выходной сигнал умножителя по модулю Р будет строго меньше значения приращения K цифрового накопителя, а тогда, когда выходной сигнал умножителя по модулю Р будет больше или равен значению модуля Р минус приращение K цифрового накопителя.

В соответствии с другим вариантом синтезатор дробных частот с фазовой синхронизацией имеет схему управления текущим коэффициентом деления его счетчика-делителя, которая в дополнение к счетчику по модулю Р с приращением, равным единице, содержит накопитель по модулю Р с приращением K, скорость которого определяется частотой генератора опорной частоты, запоминающее устройство для запоминания приращения K, на которое с выхода переполнения счетчика по модулю Р с приращением, равным единице, поступает команда на запись и которое имеет выход считывания данных, соединенный с входом приращения накопителя по модулю Р с приращением K, и устройство синхронизации, синхронизирующее сигнал переполнения накопителя с выходным сигналом счетчика-делителя до подачи его в счетчик-делитель в качестве команды на изменение коэффициента деления.

В соответствии с еще одним вариантом в предлагаемом синтезаторе осуществляется многократное разделение, когда частота и величина изменений коэффициента деления счетчика-делителя зависят от появления переполнений различных операций цифрового накопления по модулю относительно простых целых чисел Р1, Р2, ▪, Ps с различными переменными целочисленными приращениями, причем эти операции цифрового накопления проходят параллельно на частоте генератора опорной частоты, а схема управления текущим коэффициентом деления счетчика-делителя разделена на множество цепей, каждая из которых осуществляет одну из указанных операций цифрового накопления и вырабатывает отдельные сигналы переполнения, которые в неявном или явном виде добавляются к полученным ранее с помощью цифрового сумматора до подачи в счетчик-делитель в качестве команды на изменение коэффициента деления.

Другие особенности и преимущества изобретения более подробно описаны ниже на примерах его выполнения со ссылкой на прилагаемые чертежи, которые показывают:

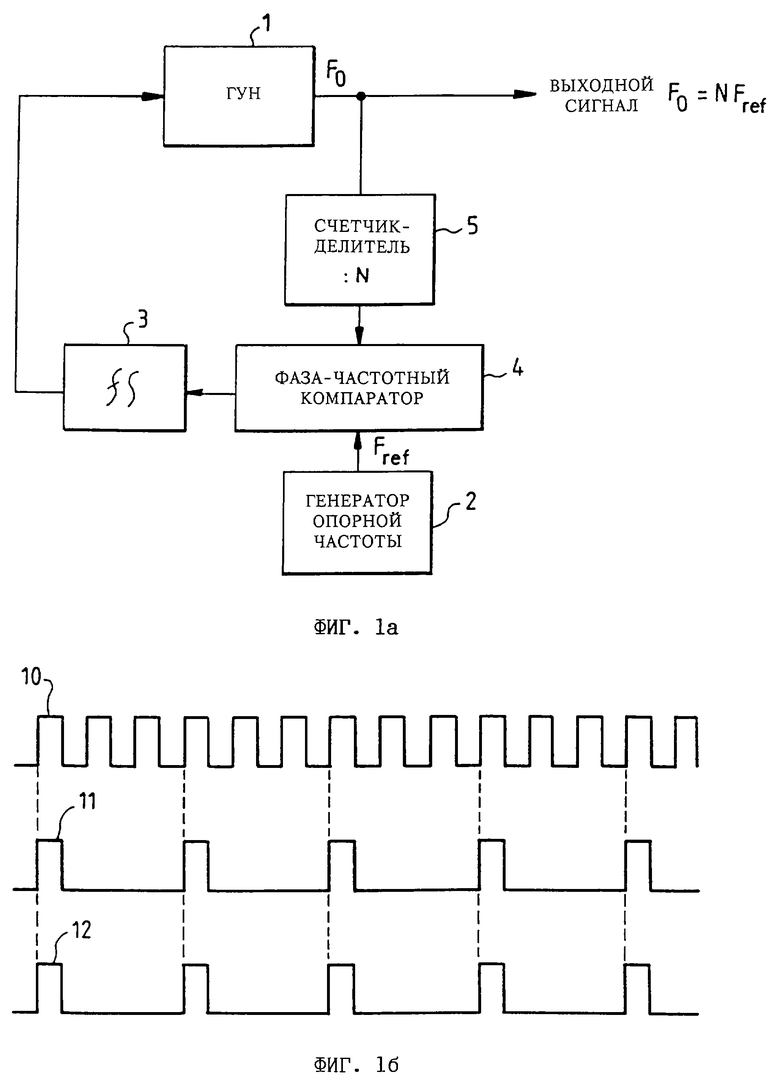

на фиг. 1a - схему синтезатора частот с фазовой синхронизацией и целочисленным делением,

на фиг.1б - графики кривых, иллюстрирующие работу синтезатора, изображенного на фиг.1а, и показывающие серии волн с фазовой когерентностью,

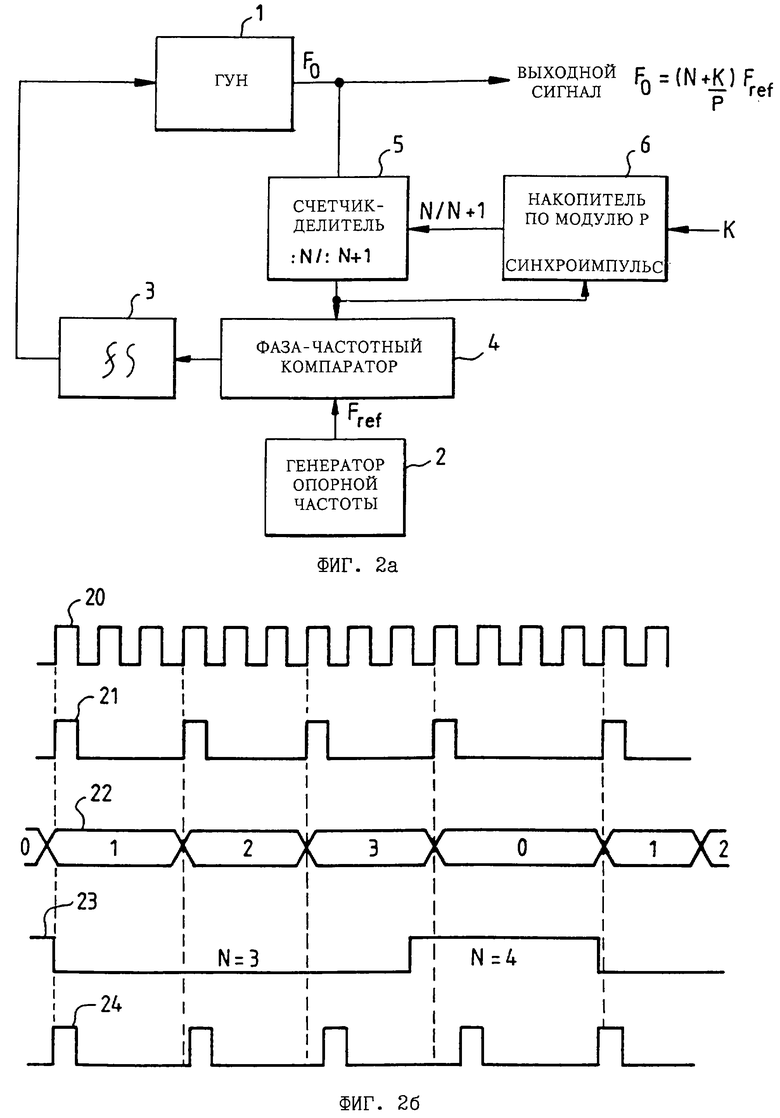

на фиг.2а - блок-схему синтезатора дробных частот, выполненного на базе обычного синтезатора частот с фазовой синхронизацией и целочисленным делением,

на фиг.2б - графики кривых, иллюстрирующие работу синтезатора, изображенного на фиг.2а, и объясняющие некогерентность показанных на графиках серий волн,

на фиг. 3 - блок-схему предлагаемой в изобретении схемы, позволяющей осуществлять операции разделения в синтезаторе частот с фазовой синхронизацией с одновременным сохранением фазовой когерентности получаемых в нем серий волн,

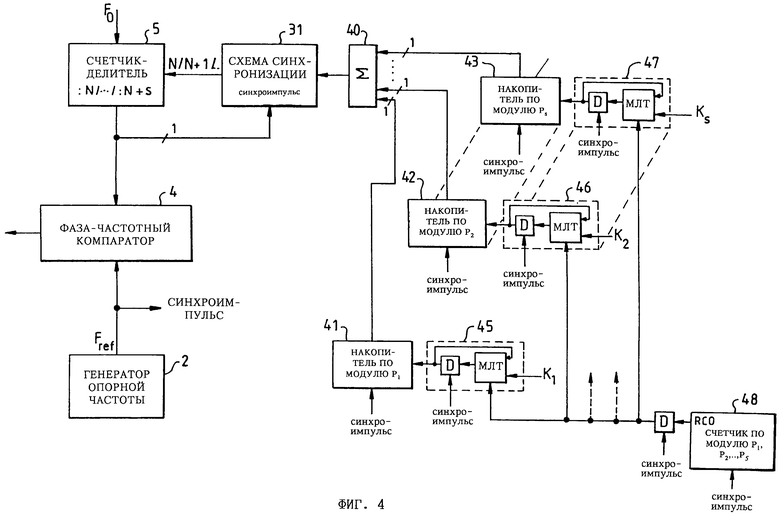

на фиг. 4 - блок-схему, являющуюся модификацией схемы, показанной на предыдущем чертеже, и позволяющую реализовать синтезатор частот с фазовой синхронизацией и с многократным дробным делением,

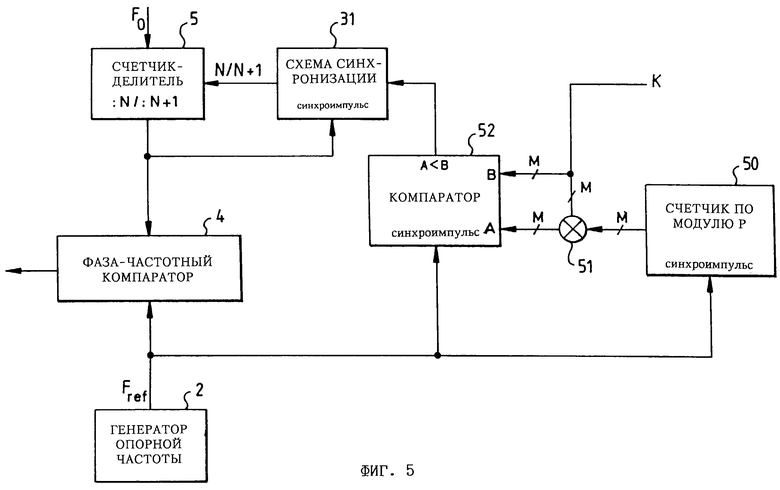

на фиг.5 - блок-схему другого варианта предлагаемой в изобретении схемы, обеспечивающую возможность выполнения операций дробного деления в синтезаторе частот с фазовой синхронизацией при одновременном сохранении когерентности получаемых в нем серий волн,

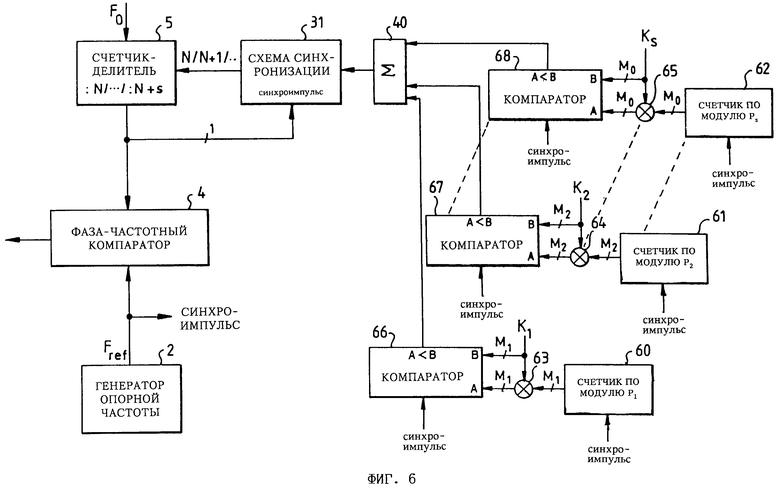

на фиг. 6 - блок-схему, являющуюся модификацией схемы, показанной на предыдущем чертеже, и позволяющую реализовать синтезатор частот с фазовой синхронизацией и многократным дробным делением, и

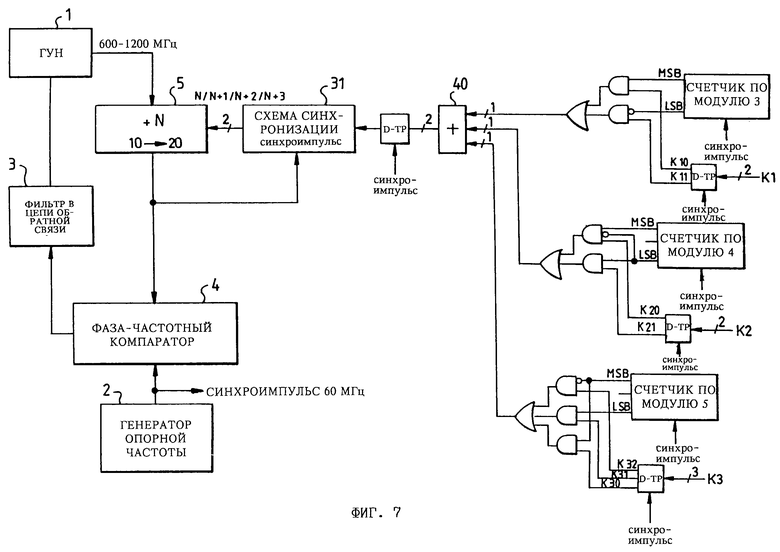

на фиг.7 - блок-схему упрощенного варианта практического выполнения схемы, показанной на предыдущем чертеже.

Показанный на фиг.1а целочисленный синтезатор частот с фазовой синхронизацией содержит генератор 1, управляемый напряжением, (ГУН), синхронизированный по фазе с генератором 2 опорной частоты с помощью схемы фазовой автоподстройки частоты (ФАПЧ). Схема ФАПЧ состоит из фильтра 3 в цепи обратной связи, фаза-частотного компаратора 4 и счетчика-делителя 5. Фильтр 3 включен между управляющим входом ГУН 1 и выходом фаза-частотного компаратора 4. Фаза-частотный компаратор 4 имеет два входа, один из которых непосредственно соединен с выходом генератора 2 опорной частоты, а другой через счетчик-делитель 5 соединен с выходом ГУН 1.

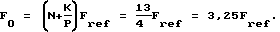

ГУН 1 вырабатывает на выходе выходной сигнал с частотой F0 синтезатора частот. Генератор 2 опорной частоты вырабатывает опорный сигнал с частотой Fref. Счетчик-делитель 5 осуществляет деление на целое число N частоты F0 сигнала, вырабатываемого ГУН 1, до его подачи в фаза-частотный компаратор 4, в результате чего схема ФАПЧ обеспечивает соблюдение следующей зависимости между частотами:

F0=N•Fref.

Наименьшее общее кратное периодов сигнала ГУН 1 и сигнала генератора 2 опорной частоты равно одному периоду генератора опорной частоты.

На фиг.1б показаны упрощенные графики временной зависимости между различными сигналами, появляющимися на выводах элементов схемы, показанной на фиг. 1а. Эти упрощенные графики не учитывают величину постоянных фазовых сдвигов, создаваемых фаза-частотным компаратором 4 и счетчиком-делителем 5.

Кривая 10 отражает характеристику выходного сигнала ГУН 1 с частотой F0, кривая 11 отражает характеристику выходного сигнала счетчика-делителя 5 после деления поступающего в него сигнала на N, где N в данном случае равно трем, а кривая 12 отражает характеристику сигнала генератора 2 опорной частоты, равной Fref.

Переполнение счетчика-делителя 5, которое обозначено на фиг.1б пунктирными линиями, всегда происходит в один и тот же момент периода сигнала генератора 2 опорной частоты. Когда начальные точки серий волн, поступающих с синтезатора, совпадают с переполнением счетчика-делителя 5, что происходит только при изменении целочисленного коэффициента счетчика-делителя, все серии волн, поступающих с синтезатора с заданной частотой, будут иметь вначале один и тот же сдвиг фазы относительно сигнала генератора 2 опорной частоты даже в том случае, если синтезатор осуществляет сдвиг фазы между этими сериями волн. Иначе говоря, все эти серии волн являются естественно когерентными.

Очевидно, что синтезатор частот с фазовой синхронизацией и целочисленным делением генерирует когерентные серии волн. Однако он имеет определенный недостаток, который связан с минимальным шагом изменения частоты, равным частоте Fref, которая часто оказывается слишком большой.

Для уменьшения минимального шага изменения частоты синтезатора частот с фазовой синхронизацией обычно используют так называемый дробный синтез, который позволяет осуществлять синтез частот с шагом, равным дробной части частоты генератора опорной частоты. Достигаемый с помощью дробного синтеза положительный эффект заключается в расширении частотного диапазона синтезатора с фазовой синхронизацией, не сопровождающегося искажениями в фазовом шуме.

При таком способе дробное деление получают путем динамического изменения величины коэффициента целочисленного деления счетчика-делителя схемы ФАПЧ между двумя последовательными значениями N и N+1. При этом для получения дробного коэффициента деления, равного N+K/P (K и Р являются целыми числами и K<Р) счетчик-делитель схемы ФАПЧ должен выполнять деление на коэффициент N в течение Р-K периодов генератора опорной частоты и на коэффициент N+1 в течение K периодов генератора опорной частоты.

Обычный способ получения такого динамического изменения коэффициента деления счетчика-делителя схемы ФАПЧ заключается в использовании цифрового накопителя по модулю Р с приращением K, работающего на частоте генератора опорной частоты, вследствие чего при его переполнениях он активирует управляющий вход для переключения коэффициента деления между значениями N и N+1. Схема работающего таким образом синтезатора показана на фиг.2а, на которой изображен добавленный в схему цифровой накопитель 6 по модулю Р с приращением K, тактовый вход которого соединен с выходом счетчика-делителя на N, обозначенного позицией 5, а выход переполнения соединен с управляющим входом счетчика-делителя 5 схемы ФАПЧ для переключения коэффициента деления между значениями N и N+1.

Счетчик-делитель 5 делит частоту F0 сигнала ГУН 1 в соответствии с дробным коэффициентом N+K/P до подачи его в фазовый компаратор 4, при этом схема ФАПЧ решает уравнение вида:

F0=(N+K/P)Fref,

которое можно также записать в виде:

PTref=(NP+K)Т0,

где Тref=1/Fref, а Т0=1/F0.

В этом случае наименьшее общее кратное периодов сигнала ГУН 1 и сигнала генератора опорной частоты уже не равно одному периоду сигнала генератора 2 опорной частоты, а равно Р периодам или полному делителю Р периодов при несократимом отношении K/P.

На фиг. 2б показаны временные зависимости различных сигналов, появляющихся на выводах отдельных элементов схемы, показанной на фиг.2а. Эти зависимости так же, как и показанные выше, носят упрощенный характер и не учитывают постоянных фазовых сдвигов, возникающих при работе различных элементов схемы, а именно, фаза-частотного компаратора, счетчика-делителя и цифрового накопителя.

Кривая 20 отражает характеристику сигнала с частотой F0 на выходе ГУН 1, кривая 21 отражает характеристику сигнала на выходе счетчика-делителя на N, обозначенного позицией 5, где N в данном случае равно трем, кривая 22 иллюстрирует содержимое цифрового накопителя 6 при Р равном четырем и K равном одному, кривая 23 отражает характеристику управляющего сигнала переполнения, а кривая 24 отражает характеристику сигнала генератора 2 опорной частоты Fref.

В этом примере, т.е. при N=3, K=1, Р=4, получают следующее значение:

Содержимое цифрового накопителя 6 изменяется при каждом изменении сигнала на выходе счетчика-делителя 5. Если принять, что содержимое цифрового накопителя в течение одного периода сигнала генератора 2 опорной частоты равно Сn, то в течение следующего периода его содержимое С+1 будет равно:

Сn+1=Сn+K=Сn+1.

В этом случае переполнение цифрового накопителя 6 будет происходить один раз после каждых четырех периодов сигнала генератора 2 опорной частоты, и после такого переполнения выходной сигнал ГУН будет делиться не на три, а на четыре. При этом для четырех периодов с частотой Fref генератора 2 опорной частоты на выходе ГУН 1 будет получено тринадцать периодов с частотой F0, что соответствует дробному коэффициенту деления, равному 3,25.

В рассматриваемом примере наименьшее общее кратное периодов сигнала ГУН с частотой F0 и сигнала генератора опорной частоты с частотой Fref равно тринадцати периодам сигнала ГУН для четырех периодов сигнала генератора опорной частоты. Переполнение счетчика-делителя 5 возникает на каждом периоде генератора 2 опорной частоты, однако переполнение происходит с переменной задержкой, которая зависит от положения периода генератора 2 опорной частоты в последовательности, соответствующей наименьшему общему кратному указанных выше периодов. Поскольку в данном случае наименьшее общее кратное периодов сохраняется в течение четырех периодов генератора 2 опорной частоты, переполнение счетчика-делителя 5 может происходить в течение периода генератора 2 опорной частоты при четырех явно выраженных значениях фазового сдвига. Так, например, синтезатор генерирует первую серию волн на частоте F1, затем другую серию волн с другой частотой F2, обусловленной изменением приращения цифрового накопителя, и в завершение вторую серию волн на частоте F1, при этом, однако, вторая серия волн с частотой F1 необязательно должна иметь такую же опорную фазу, что и первая. Фактически изменение частоты синтезатора, когда оно соответствует изменению приращения цифрового накопителя, происходит при неконтролируемом переполнении счетчика-делителя 5, а именно, со сдвигом по фазе, величина которого может иметь любое из четырех явно выраженных значений. Поэтому две серии волн с частотой F1 необязательно будут иметь один и тот же сдвиг фазы по отношению к сигналу генератора опорной частоты. Тем самым разрушается когерентность синтезируемых частот.

Отсутствие фазовой когерентности у известных синтезаторов дробных частот с фазовой синхронизацией связано с зависимостью фактического состояния используемого в них цифрового накопителя от изменения во времени различных управляющих заранее подаваемых в него величин приращений. Такое отсутствие фазовой когерентности известных синтезаторов ограничивает возможности использования их в определенных целях, например, в доплеровских радиолокационных станциях (РЛС), несмотря на их спектральную чистоту, благодаря которой их применение в этих целях могло бы оказаться очень полезным.

С целью обеспечить необходимую когерентность частот, генерируемых синтезаторами частот с фазовой синхронизацией, ранее предлагалось добавить к ним запоминающее устройство (ЗУ) для фазы, выполненное на базе счетчика по модулю Р с единичным приращением, скорость работы которого определяется частотой генератора опорной частоты. Такое ЗУ для фазы используется для выбора положения внутри последовательности Р следующих друг за другом периодов, которое зависит от наименьшего общего кратного периодов сигнала генератора опорной частоты и выходного сигнала синтезатора. При этом изменение приращения цифрового накопителя всегда происходит с одним и тем же сдвигом фазы по отношению к этому наименьшему общему кратному периодов. Необходимо отметить, что это общее кратное периодов равно Р периодам или полному делителю Р периодов генератора опорной частоты.

Для поддержания одной и той же опорной фазы относительно этого наименьшего общего кратного периодов сигнала ГУН и сигнала генератора опорной частоты можно использовать ЗУ для фазы, выполненное на основе счетчика по модулю Р с единичным приращением, работающего на частоте генератора опорной частоты, с тем, чтобы изменения приращения цифрового накопителя происходили только через каждые Р периодов генератора опорной частоты. Такая возможность предусмотрена в первом варианте выполнения изобретения. Однако изменение приращения цифрового накопителя только через каждые Р периодов генератора опорной частоты приводит к определенным временным ограничениям в процессе генерирования серий волн, что в ряде случаев создает определенные проблемы. Во избежание таких временных ограничений ЗУ для фазы, выполненное на основе счетчика по модулю Р с единичным приращением, работающего со скоростью генератора эталонной частоты, можно использовать для фиксации моментов переполнения цифрового накопителя, который включается в работу при запуске синтезатора; такое решение предусмотрено во втором варианте выполнения изобретения.

Первый вариант выполнения изобретения показан на фиг.3. Для упрощения на этом чертеже ГУН 1 и фильтр 3 в цепи обратной связи не показаны, а показаны генератор 2 опорной частоты, счетчик-делитель 5 и фаза-частотный компаратор 4 схемы ФАПЧ. Счетчик-делитель 5 имеет два последовательных целых коэффициента деления N и N+1 и один вход для управления переключением между этими двумя коэффициентами. Для управления изменением коэффициента деления счетчика-делителя 5 на его вход подается пилот-сигнал, как описано выше, с выхода переполнения работающего на частоте генератора 2 опорной частоты цифрового накопителя 30 по модулю Р с целочисленным приращением K, которое можно менять и которое меньше Р.

Однако цифровой накопитель 30 включен в схему иным образом. При таком включении его скорость уже более не задается выходным сигналом счетчика-делителя 5, частота которого совпадает с частотой генератора 2 опорной частоты только тогда, когда схема ФАПЧ достигает равновесия, а определяется непосредственно сигналом генератора 2 опорной частоты. С учетом этого выход переполнения цифрового накопителя уже не соединен непосредственно со схемой, управляющей переключением коэффициента счетчика-делителя 5. Более того, он соединен с этой схемой через схему (устройство) 31 синхронизации. Скорость этой схемы синхронизации задается выходным сигналом счетчика-делителя 5 таким образом, что состояние выхода переполнения цифрового накопителя 30 дискретизируется с частотой переполнений счетчика-делителя 5.

Вход цифрового накопителя 30 по модулю Р, на который подается приращение К, соединен с выходом задающего приращение цифрового ЗУ 32. Запись приращения начинается по сигналу переполнения ЗУ для фазы, выполненного на основе счетчика 33 по модулю с единичным приращением, причем скорость этого счетчика 33 задается сигналом генератора 2 опорной частоты. Задающее приращение цифровое ЗУ 32 содержит, например, во-первых, мультиплексор 320 с двумя информационными входами, одним выходом для вывода данных и одним адресным входом и, во-вторых, блок D-триггерных логических схем 321. Один из информационных входов мультиплексора 320 соединен с его выходом цепью обратной связи, которая образована блоком D-триггерных логических схем 321, скорость которых задается сигналом генератора 2 опорной частоты.

На другой информационный вход мультиплексора 320 подается заданное значение приращения K. Адресный вход мультиплексора 320 соединен с выходом переполнения счетчика 33 по модулю Р с единичным приращением через D-триггерную логическую схему 34, скорость которой задается генератором 2 опорной частоты. Адресация мультиплексора 320 такова, что при отсутствии переполнения счетчика 33 по модулю Р с единичным приращением его выход для вывода данных замыкается образованной блоком D-триггерных логических схем 321 цепью обратной связи сам на себя.

Тем самым обеспечивается запоминание приращения, которое корректируется только при переполнении счетчика 33 по модулю Р с единичным приращением, который выполняет функцию ЗУ для фазы и позволяет изменять приращение K цифрового накопителя 30 по модулю Р только через каждые Р периодов генератора 2 опорной частоты. Тем самым, как сказано выше, обеспечивается фазовая когерентность между всеми сериями волн, генерируемыми синтезатором частот с одной и той частотой, даже в том случае, если синтезатор частот осуществил мгновенную девиацию частоты в промежутках между моментами генерирования этих серий волн.

Возможен другой вариант схемы, когда выход D-триггерной логической схемы 34 соединен также с входом сброса, т.е. установки в первоначальное состояние, цифрового накопителя 30, что обеспечивает синхронизацию точек прохода через ноль цифрового накопителя 30 с соответствующими точками выполняющего функцию ЗУ для фазы счетчика 33 по модулю Р с единичным приращением. Такое соединение показано на фиг.3 пунктирной линией, соединяющей выход D-триггерной логической схемы 34 с входом сброса цифрового накопителя 30 по модулю Р.

На фиг.4 показан модифицированный вариант схемы, изображенной на фиг.3, применительно к синтезатору кратных дробных частот с фазовой синхронизацией. Синтезаторы кратных дробных частот с фазовой синхронизацией отличаются от синтезаторов одиночных дробных частот с фазовой синхронизацией тем, что в их схеме ФАПЧ используется счетчик-делитель, у которого количество возможных последовательных коэффициентов целочисленного деления (N, N+1, N+2, ▪, N+s) больше двух, а команда на переключение коэффициента деления управляется выходом цифрового сумматора 40, на который команды переполнения поступают от s отдельных цифровых накопителей 41, 42, ▪, 43 по явно выраженному сравнительно простыми целыми числами модулю P1, Р2, ▪, Ps. Причем все эти накопители работают на частоте генератора 2 опорной частоты с различными целочисленными приращениями K0, K1, ▪, Ks. В каждый из цифровых накопителей 41, 42, ▪, 43 его приращение K0, K1, ▪, Ks поступает от отдельного ЗУ 45, 46, ▪, 47 для приращений, которое корректируется только при каждом переполнении счетчика 48 по модулю произведения  с единичным приращением, который работает на частоте генератора 2 опорной частоты и служит общим ЗУ для фазы.

с единичным приращением, который работает на частоте генератора 2 опорной частоты и служит общим ЗУ для фазы.

Очевидно, что в такой схеме изменение частоты путем изменения приращения возможно только каждые  периодов генератора опорной частоты. Это может привести к определенным временным ограничениям в работе и затруднить использование синтезатора в тех случаях, когда частоту необходимо менять очень быстро, сохраняя при этом когерентность частот. Для решения этой проблемы, связанной с временными ограничениями на переключение синтезатора с одной частоты на другую, и сохранения когерентности можно использовать ЗУ для фазы, начиная отсчет фазы только с моментов переполнения цифрового накопителя, который систематически включается при запуске синтезатора.

периодов генератора опорной частоты. Это может привести к определенным временным ограничениям в работе и затруднить использование синтезатора в тех случаях, когда частоту необходимо менять очень быстро, сохраняя при этом когерентность частот. Для решения этой проблемы, связанной с временными ограничениями на переключение синтезатора с одной частоты на другую, и сохранения когерентности можно использовать ЗУ для фазы, начиная отсчет фазы только с моментов переполнения цифрового накопителя, который систематически включается при запуске синтезатора.

Ниже рассмотрен пример работы цифрового накопителя С по модулю Р с неопределенным целочисленным приращением K, меньшим Р, вводимым в схему со скоростью генератора опорной частоты в момент запуска синтезатора частот при нулевом периоде генератора опорной частоты:

C0=0.

При n-м периоде генератора опорной частоты получают следующее значение Сn:

Cn=(n•K) mod P (1)

Для получения зависимости Сn от содержимого ЗУ для фазы, которое представляет собой счетчик по модулю Р с единичным приращением, работающий на частоте генератора опорной частоты, необходимо, чтобы в приведенном выше уравнении присутствовал следующий член:

n mod P.

С этой целью можно принять, что

X=n-(n mod P) (2)

Если в уравнении (1) n заменить его значением из уравнения (2), то получают следующее выражение:

Cn=(X•K) mod P+[(n mod P)•K] mod P.

Поскольку Р делит X, можно записать:

(X•K) mod P=0.

Следовательно:

Cn=[(n mod P)•K] mod P.

Из последнего выражения следует, что содержимое цифрового накопителя с приращением K, работающего со скоростью генератора опорной частоты и включаемого при запуске синхронизатора, равно произведению по модулю Р приращения K на содержимое ЗУ для фазы, которое представляет собой счетчик по модулю Р с единичным приращением, работающий на частоте генератора опорной частоты. Тем самым создается возможность в любой момент времени узнать содержимое этого цифрового накопителя путем умножения по модулю Р приращения K на содержимое ЗУ для фазы.

Зная содержимое этого цифрового накопителя, включаемого при запуске синхронизатора, можно определить количество периодов генератора опорной частоты, в течение которых происходит переполнение этого известного содержимого цифрового накопителя. Очевидно, что если содержимое накопителя окажется явно меньше приращения K, то это будет означать, что переполнение содержимого произошло во время предыдущего периода генератора опорной частоты. Если содержимое будет больше или равно приращению K, то это будет означать, что во время предыдущего периода генератора опорной частоты переполнения содержимого накопителя не произошло. Следует отметить, что при правильном или ошибочном значениях выражение:

[(n mod P)•K] mod P<K

дает, плюс или минус временной сдвиг, соответственно величину 1 и 0 сигнала переполнения цифрового накопителя, который включается при запуске синтезатора. Такой временной сдвиг, поскольку он является постоянным, не оказывает влияния на когерентность синтезируемых частот.

В другом варианте содержимое цифрового накопителя, включаемого при запуске синтезатора, можно сравнивать со значением Р-K. Очевидно, что если содержимое цифрового накопителя будет больше или равно значению P-K, то на следующем периоде генератора опорной частоты произойдет переполнение накопителя. В противном случае переполнения не произойдет.

На фиг.5 показана схема синтезатора когерентных дробных частот с фазовой синхронизацией, основанная на неявном вычислении переполнений работы цифрового накопителя по модулю Р с целочисленным приращением K, работающего со скоростью генератора опорной частоты и включаемого при запуске синтезатора. Как и на фиг.3, на этом чертеже ГУН 1 и фильтр 3 в цепи обратной связи не показаны, а показаны только генератор 2 опорной частоты, счетчик-делитель 5 и фаза-частотный компаратор 4 схемы ФАПЧ. Счетчик-делитель 5, как и в первом варианте, имеет два возможных последовательных коэффициента целочисленного деления N и N +1 и один управляющий вход для переключения его между этими двумя значениями коэффициента деления, соединенный с выходом схемы (устройства) 31 синхронизации, скорость которой задается выходным сигналом счетчика-делителя 5. Эта схема 31 синхронизации дискретизирует состояние сигнала для управления переключением последовательных коэффициентов деления N и N +1 со скоростью переполнений счетчика-делителя 5.

Сигнал для переключения последовательных коэффициентов деления N и N +1 поступает на вход схемы 31 синхронизации со схемы, задающей текущее значение коэффициента деления. Эта схема управления в неявном виде осуществляет цифровое суммирование по модулю Р с приращением K, что инициируется при запуске синтезатора, и измеряет периоды генератора 2 опорной частоты, в течение которых происходит переполнение цифрового накопителя. Эта схема состоит из счетчика 50 по модулю Р с единичным приращением, скорость которого задается генератором 2 опорной частоты, цифрового умножителя 51 по модулю Р с двумя информационными входами и одного цифрового компаратора 52 с двумя параллельными информационными входами А и В, одним тактовым входом и одним выходом сравнения А<В.

На один из входов умножителя 51 поступают одиночные импульсы счета счетчика 50 по модулю Р, а на другой вход поступают цифровое значение приращения K накопителя. Выход умножителя соединен с информационным входом А цифрового компаратора 52. На другой информационный вход B цифрового компаратора 52 поступает цифровое значение приращения K накопителя, при этом его тактовый вход соединен с выходом генератора 2 опорной частоты, а его выход сравнения А<В служит выходом указанной схемы управления.

Счетчик 50 по модулю Р с единичным приращением, скорость которого задается генератором 2 опорной частоты, представляет собой ЗУ для фазы. Этот счетчик подсчитывает количество n mod Р периодов генератора опорной частоты с момента запуска синтезатора. Умножитель 51 по модулю Р выдает произведение по модулю Р величины этого подсчета на значение приращения K накопителя:

[(n mod P)•K] mod P,

а именно, как уже было описано выше, произведение значения цифрового суммирования, по модулю Р и приращения K, полученное при скорости генератора 2 опорной частоты с момента запуска синтезатора при любой динамике изменений значения приращения K. Компаратор 52, реализуя зависимость

[(n mod P)•K] P<K,

определяет периоды сигнала генератора 2 опорной частоты, при которых происходит переполнение цифрового накопителя. Этот процесс происходит с постоянной задержкой по времени, равной длительности одного периода генератора опорной частоты, которую можно не принимать во внимание, поскольку она является постоянной. Затем это определение указанных периодов сигнала генератора опорной частоты используется после повторной синхронизации переполнений счетчика-делителя 5 для временного переключения коэффициента деления счетчика-делителя 5 снова на значение N+1 с получением тем самым требуемой дробной частоты. Поскольку цифровой накопитель всегда начинает работать при запуске синхронизатора, все серии волн одной и той же частоты, которые генерируются синтезатором во время его работы, оказываются когерентными в фазе независимо от изменений во времени значения приращения K.

На фиг.6 показан модифицированный вариант показанной на фиг.5 схемы, позволяющий реализовать синтезатор кратных дробных частот с фазовой синхронизацией. Счетчик-делитель 5 схемы ФАПЧ имеет s последовательных целочисленных коэффициентов деления N, N+1, ▪, N+s и один управляющий вход для выбора одного из коэффициентов деления, соединенный с выходом схемы управления текущим коэффициентом деления через схему (устройство) 31 синхронизации, которая учитывает выбранный коэффициент деления синхронно с переполнениями счетчика-делителя 5.

Схема управления текущим коэффициентом деления содержит блок из s отдельных схем для неявного цифрового суммирования или накопления и для детектирования переполнений при вычисленном суммировании и цифровой сумматор 40, который осуществляет суммирование на выходе s сигналов детектирования переполнения, выдаваемых блоком из s отдельных схем. Для получения этих s сигналов переполнения s отдельных схем блока со скоростью генератора 2 опорной частоты выполняют параллельно s операций цифрового суммирования по модулю s сравнительно простых целых чисел Р1, P2, ▪, Рs с различными целочисленными приращениями K1, K2, ▪, Ks и детектируют периоды генератора 2 опорной частоты, в течение которых они переполняются.

Каждая из этих отдельных схем, аналогично предназначенной для управления текущим значением коэффициента деления схеме, показанной на фиг.5, содержит счетчик 60, 61, ▪, 62 соответственно с единичным приращением, скорость которого задается сигналом генератора 2 опорной частоты, цифровой умножитель 63, 64, ▪, 65, соответственно осуществляющий умножение приращения на вычисленное значение счетчика 60, 61, ▪, 62, и цифровой компаратор 66, 67, ▪, 68, соответственно детектирующий периоды генератора 2 опорной частоты, при которых полученное в умножителе произведение оказывается явно меньше приращения.

Каждая отдельная схема для неявного суммирования и детектирования отличается от других схем значением пересчета по модулю, с которым она подсчитывает периоды генератора опорной частоты и выдает произведение этого рассчитанного значения на величину приращения. При этом i-я схема имеет счетчик и умножитель по модулю Рi, а значения пересчета по модулю P1, Р2, ▪, Pi, ▪, Ps отличаются друг от друга и являются относительно простыми числами.

Показанная на фиг.6 схема только кажется сложной и в большинстве случаев компаратор и умножитель каждой отдельной схемы управления текущим значением коэффициента деления можно выполнить в виде сравнительно простого набора логических элементов.

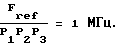

В качестве примера можно рассмотреть синтезатор когерентных частот, который перекрывает диапазон частот от 600 до 1200 МГц при частоте генератора опорной частоты, равной 60 МГц и схема многократного дробления частот которого со значениями пересчета по модулю 3, 4 и 5 обладает следующим разрешением:

Такой синтезатор, имеющий показанную на фиг.6 конфигурацию, содержит три отдельных схемы для неявного цифрового суммирования и локализации переполнений вычисленных числовых сумм, которые осуществляют параллельно три операции цифрового суммирования по модулю 3, 4 и 5 с различными приращениями со скоростью генератора опорной частоты и детектируют соответствующие переполнения. Двоичные выходные сигналы этих отдельных схем суммируются таким образом, что после повторной синхронизации они используются для управления выбором текущего коэффициента деления счетчика-делителя схемы ФАПЧ. Как описано выше, эти три отдельные счетные и локализующие схемы должны выдавать выходной двоичный сигнал, соответствующий достоверности или недостоверности неравенства:

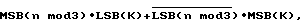

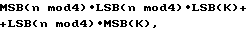

[(n mod P)•K] mod P<K.

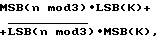

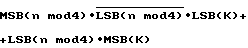

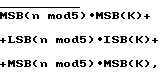

полученного для значений пересчета по модулю 3, 4 и 5 и для выбранных значений приращений K. Анализ логических состояний выходных сигналов этих отдельных схем равнозначен анализу таблиц действительных или ложных логических состояний, определенных этим неравенством для каждого значения пересчета по модулю 3, 4 и 5 в виде функции, во-первых, значений, сканированных счетчиком по модулю ЗУ для фазы и, во-вторых, возможных значений приращений. Эти таблицы показывают, что действительные или ложные логические состояния, определенные неравенством, удовлетворяют трем логическим уравнениям, зависящим от значения пересчета по модулю:

- первое логическое уравнение для пересчета по модулю 3:

- второе логическое уравнение для пересчета по модулю 4:

- третье логическое уравнение для пересчета по модулю 5:

где MSB(x) представляет собой старший разряд х, ISB(x) представляет собой промежуточный разряд х, в предположении, что он закодирован тремя разрядами, a LSB (х) представляет собой младший разряд х.

Эти три логических уравнения показывают, что в данном случае умножители и компараторы отдельных счетных и локализующих схем в варианте, показанном на фиг.6, можно выполнить в виде нескольких логических элементов.

Выполненный таким образом сравнительно простой вариант показан на фиг.7.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой синтезатор частоты | 1987 |

|

SU1515364A1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ | 2002 |

|

RU2223597C1 |

| СИНТЕЗАТОР СЕТКИ ЧАСТОТ НА БАЗЕ КОНТУРА ФАПЧ С КОМПЕНСАЦИЕЙ ПОМЕХ ДРОБНОСТИ | 2012 |

|

RU2491713C1 |

| Цифровой синтезатор изменяющейся частоты | 1982 |

|

SU1107262A1 |

| Цифровой синтезатор изменяющейся частоты | 1985 |

|

SU1298836A1 |

| Цифровой синтезатор частот | 1982 |

|

SU1125733A1 |

| СИНТЕЗАТОР ЧАСТОТ | 2010 |

|

RU2434322C1 |

| Синтезатор частот | 1988 |

|

SU1656680A1 |

| СИНТЕЗАТОР ЧАСТОТ | 2009 |

|

RU2395899C1 |

| Широкодиапазонный синтезатор с фазовой автоподстройкой частоты управляемого генератора с переключаемыми резонаторами | 2023 |

|

RU2804407C1 |

Изобретение относится к области синтеза частот. Синтезатор дробных когерентных частот с фазовой синхронизацией содержит генератор опорной частоты, генератор, управляемый напряжением, схему фазовой автоподстройки частоты, фазовый компаратор, счетчик-делитель с регулируемым целочисленным коэффициентом деления, схему управления текущим значением коэффициента деления счетчика-делителя, которая содержит по меньшей мере один счетчик по модулю Р с единичным приращением, используемый в качестве запоминающего устройства для фазы и инициирующего изменения значения приращения К при выполнении операции цифрового накопления. Достигаемый технический результат-создание синтезаторов дробных частот с фазовой синхронизацией, способных генерировать когерентные сигналы даже после мгновенной девиации частоты. 8 з.п. ф-лы, 7 ил.

для пересчета по модулю 4 логическому уравнению

и для пересчета по модулю 5 логическому уравнению

где n - количество периодов генератора опорной частоты, начиная с произвольного момента;

К - приращение накопления;

MSB(x) - старший разряд х;

ISB(x) - промежуточный разряд х в предположении, что он закодирован тремя разрядами;

LSB(x) - младший разряд х. значений пересчета по модулю, и каждая из указанных схем имеет собственный накопитель, работающий с конкретным значением пересчета по модулю Pi с конкретным приращением на частоте генератора опорной частоты, а также собственное запоминающее устройство для приращения, на которое подается команда записи с выхода переполнения общего счетчика, и предназначенный для вывода данных, выход которого соединен со входом приращения ее собственного накопителя.

значений пересчета по модулю, и каждая из указанных схем имеет собственный накопитель, работающий с конкретным значением пересчета по модулю Pi с конкретным приращением на частоте генератора опорной частоты, а также собственное запоминающее устройство для приращения, на которое подается команда записи с выхода переполнения общего счетчика, и предназначенный для вывода данных, выход которого соединен со входом приращения ее собственного накопителя.

| Переточное устройство | 1973 |

|

SU557799A1 |

| Синтезатор частот | 1983 |

|

SU1202054A1 |

| US 4816774, 28.03.1989 | |||

| US 5122762 A, 16.06.1992 | |||

| US 5128632 A, 07.07.1982 | |||

| US 5394106 A, 28.02.1995 | |||

| СТЕНД ДЛЯ ОБКАТКИ И ИСПЫТАНИЙ ГИДРАВЛИЧЕСКИХ ЗАБОЙНЫХ ДВИГАТЕЛЕЙ | 2003 |

|

RU2253752C2 |

Авторы

Даты

2003-07-20—Публикация

1998-05-06—Подача