1

Известны нересчетные схемы на фазоимпульсных .многоустойчивых элементах, содержан1,11е генератор тактовых нмнульсов, синхронизатор и логические схемы «ИЛИ.

Предлагаемая схема отличается тем, что в iieii выход генератора тактов 1х нмиульсов подсоеллиен ко всем нерв1 1м входам схем «ИЛИ, второй вход первой схемы «ИЛИ соедииен с выходом синхроннзатора, а второй выход генератора тактовых имнульсов подключей ко входу опорной ячейки. Выход носледней соедннен с снихропизатором, второй вход i;oTOporo нодключеи к тине пересчета ;1Мнульсов.

Это 1 озвол;гет Л1|)остнть схему н попглсить се надежность.

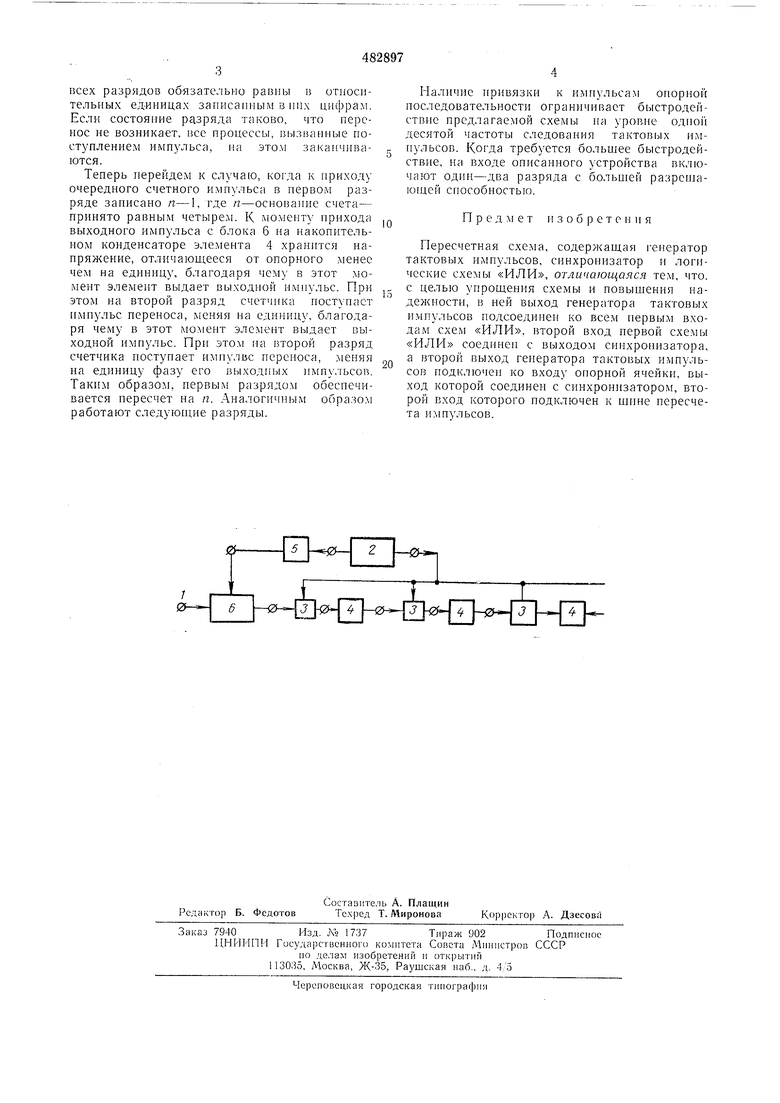

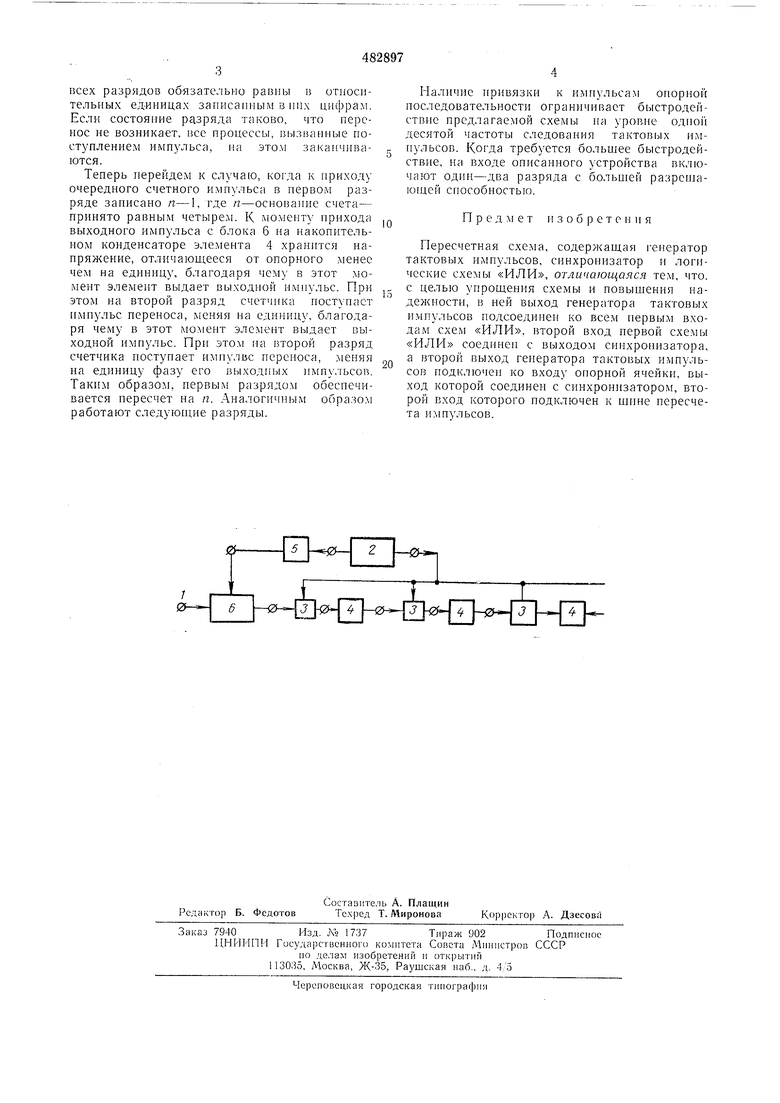

Па чертеже нредставлена блок-схема иредлагяемого устройства.

При отсутствии счетных } М1 ульсон на вхо.1,е 1 имнульсы с одного из выходов генератора 2 через схемы 3 «ИЛИ ноступают па фазонмнульсн1ле элементы 4 всех разрядов счетчика. Иа онорилй злемег.т 5 нодаются тактовые нлшульсы со второго выхода генератора 2.

Чтобы состояние фазонмпульсного элемента I не л.енялось, иа его вход л,олж110 ностурл.ть такое же количество имнульсов, которое нодаеня на вход онорного элемента 5. При отсутствии счетных импульсов это условие выполняется в первом разряде счетчика. Однако на вход элеменга 4 второго разряда через схему 3 гюлгимо тактовых поступают выходные нмнульсы riepBoro разряда. Благодаря совпаденню во временн на схеме 3 два нмпульса сливаются и на вход эле гента 4 второго разряда поступают как один имнульс. То же самое происходит па входах всех остальных разря.чо.

Таким образолг, при отсутетвин счетпых импульсов песмотря па иаличие связей между разрядами на Г5ход фазоимпульсиого элел ента 4 каждого разряда действуют только тактовые импульсы. В результате элементы ра:;рядов хранят заннеанную ; них пнфо1)ма1ино. представлеиную фазой выходных импульсов каждого элемента относительно опорной носледовательиости с В1 1хода элемеита 5.

Счетные импульсы привязываются синхронизатором б к выходиым импульсам опорпого элемента. Тем самыл исключаются просчеты в случае, Kor;ui счетш и импульс ирнходпт одповременио с очередным тактовым. 11мпулье с выхода синхронизатора 6 через схему 3 поступасг па э;1е.мепг - первого разряда счетчика и увелич1П ает па едишщу иаП()яжение на его иакогиггельпом конденсаторе. В момепт-прнхода нмпульса с Р.ыхода сппхронпзатора, прпвязанного к очередному онорному, нанряжеьню па копдепсаторах элементов -1

всех разрядов обязательно равны в относительных ед-иницах записанным з ннх цифрам. Если состояние разряда таково, что перенос не возникает, все процессы, вызванные поступлением импульса, на этом заканчиваются.

Теперь перейдем к случаю, когда к приходу очередного счетного импульса в первом разряде записано п-1, где п-основание счета- принято равным четырем. К моменту прихода выходного импульса с блока 6 на накопительном конденеаторе элемента 4 хранится напряжение, отличающееся от опорного менее чем на единицу, благодаря чему в этот момент элемент выдает выходной имнульс. При этом на второй разряд счетчика поступает мпульс переноса, меняя на единицу, благодаря чему в этот момент элемент выдает выходной имнульс. При этом на второй разряд счетчика иостунает имнулвс переноса, . на единицу фазу его выходных импульсов. Таким образом, первым разрядом обеспечивается пересчет на п. Аналогичным образом работают следующие разряды.

Наличие привязки к импульса.м опорной последовательноети ограничивает быстродействие предлагаемой схемы на уровпе одно) десятой частоты следования тактовых импульсов. Когда требуется большее быстродействие, иа входе оппсанного устройства включают один-два разряда с большей разрешающей способиостыо.

Предмет изобретения

Пересчетная схема, содержащая генератор тактовых импульсов, синхронизатор и логические схемы «ИЛИ, отличающаяся тем, что. с целью упрощения схемы и повышения надежности, в ней выход генератора тактовых п.мпульсов подсоединен ко все.м иервы.м входам схем «ИЛИ, второй вход первой схемы «ИЛИ соединен с выходом синхронизатора, а второй выход, генератора тактовых импульсов подключен ко входу опорной ячейки, выход которой соединен с синхронизатором, второй вход которого подключен к шине пересчета импульсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| РЕВЕРСИВНЫЙ СЧЕТЧИК ИМПУЛЬСОВ | 1970 |

|

SU275132A1 |

| ФАЗОИМПУЛЬСНЫЙ СЧЕТЧИК ИМПУЛЬСОВ | 1971 |

|

SU304709A1 |

| Устройство для задания точек квантования периодических электрических сигналов | 1973 |

|

SU488148A1 |

| Преобразователь коротких интервалов времени в цифровой код | 1975 |

|

SU526852A1 |

| Счетчик импульсов | 1978 |

|

SU736384A1 |

| Электронные часы с коррекцией показаний | 1978 |

|

SU731414A1 |

| ИМПУЛЬСНЫЙ СИНХРОНИЗАТОР | 1970 |

|

SU275121A1 |

| Аналого-цифровой преобразователь | 1976 |

|

SU563713A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕХОДА С ОДНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ ИМПУЛЬСОВ НА ДРУГУЮ | 1970 |

|

SU277020A1 |

| УПРАВЛЯЕМЫЙ СИНТЕЗАТОР ЧАСТОТЫ | 1971 |

|

SU290393A1 |

0

Авторы

Даты

1975-08-30—Публикация

1965-12-15—Подача