1

Изобретение относится к устройствам преобразования информации в цифровой код и может быть использовано в цифровой и электроизмерительной и вычислительной технике.

Известен ряд преобразователей коротких интервалов в код, в которых временной интервал предварительно преобразуется, «растягивается, а затем заполняется счетными импульсами 1.

В частности, известен ;преобразОВатель коротких интер|Валов в цифровой код, содержащий управляющий триггер, первый вход которого соединен с шиной «Сброс, а выход - с управляющим входом вентиля, генератор импульсов, сдвигающий регистр, схему растяжки интервалов времени, дешифратор, первый управляющий вход которого соединен с выходом вентиля, а выходы подключены ко входам счетчиков импульсов первого, второго и третьего разрядов 2.

Недостатком такого преобразователя является сравнительно низкая точность за Счет возможной потери имнульсов счета при одновременном нриходе их с пepeднн фронтом измеряемого интервала времени.

Целью изобретения является повышение точности преобразования.

Для этого в преобразователь коротких интервалов времени в цифровой код введены блок управления, формирователь, два ключа

и две схемы ИЛИ, причем выход счетчика второго разряда соединен со входом счетчика первого разряда, выход блока управления подключен ко входу схемы растяжки интервалов времени, выход которой подключен к первым входам схем ИЛИ и к первому входу блока управления, второй вход первой схемы ИЛИ соединен с шиной «Сброс и с запрещающим входом первого ключа, входами

«Сброс блока управленпя, схемы растяжки, счетчиков и сдвигающего регистра, разрешаюЩИ11 вход первого ключа соединен со вторым входом блока управленпя и с первым выходом формирователя, третий вход блока уиравления подключен ко второму выходу формирователя, ко второму входу управляющего триггера, к третьему входу первой схемы ИЛИ и к первому входу второй схемы ИЛИ, выход которой соединен со входом сдвигающего регистра, выход генератора импульсов подключен к информационным входам ключей и к четвертому входу блока управления, .каждый н-ый выход сдвигающего регистра подключен к (1-|-1) управляющему входу дешифратора, выход первого ключа соединен с разрешающим входом второго ключа, запрещающий вход которого соединен с выходом первой схемы ИЛИ, а выход второго ключа подключен ко входам дешифратора и

к пятому входу блока управления.

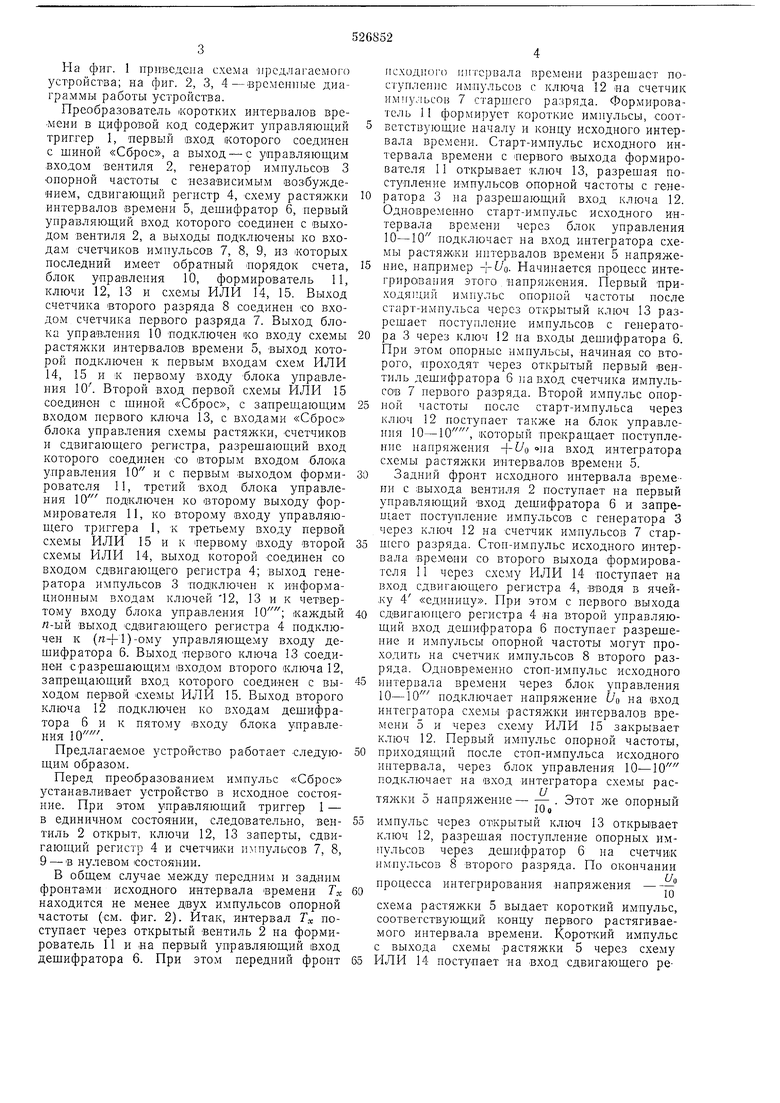

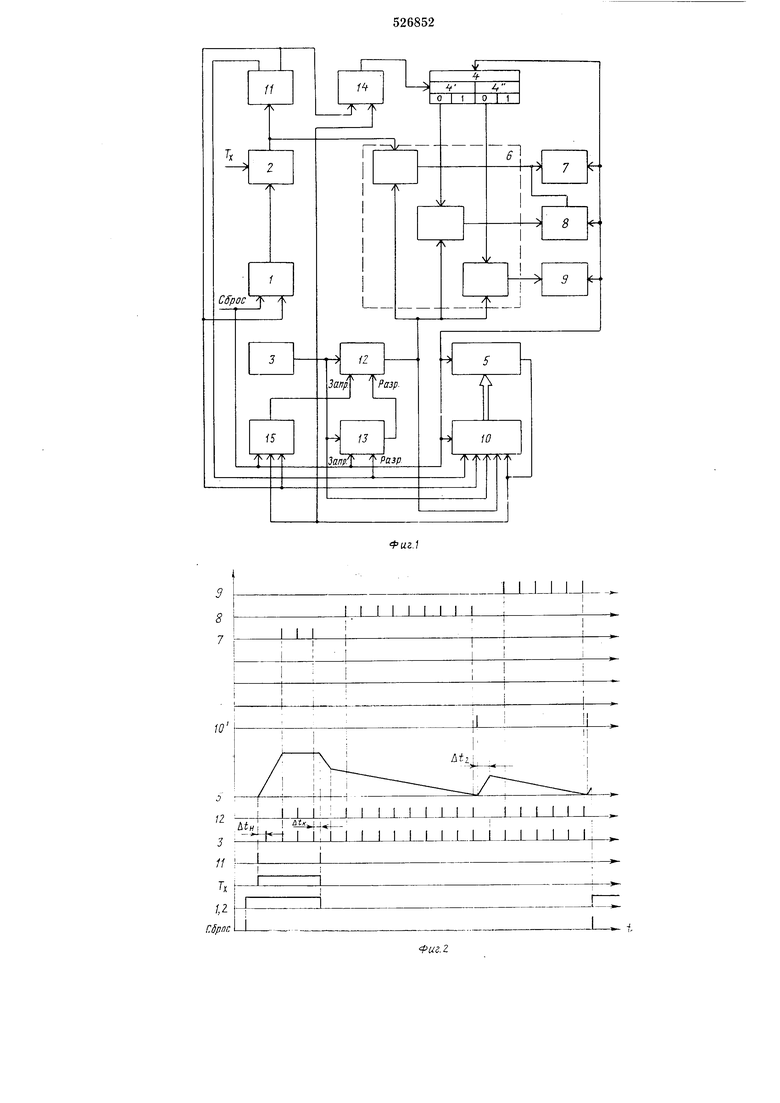

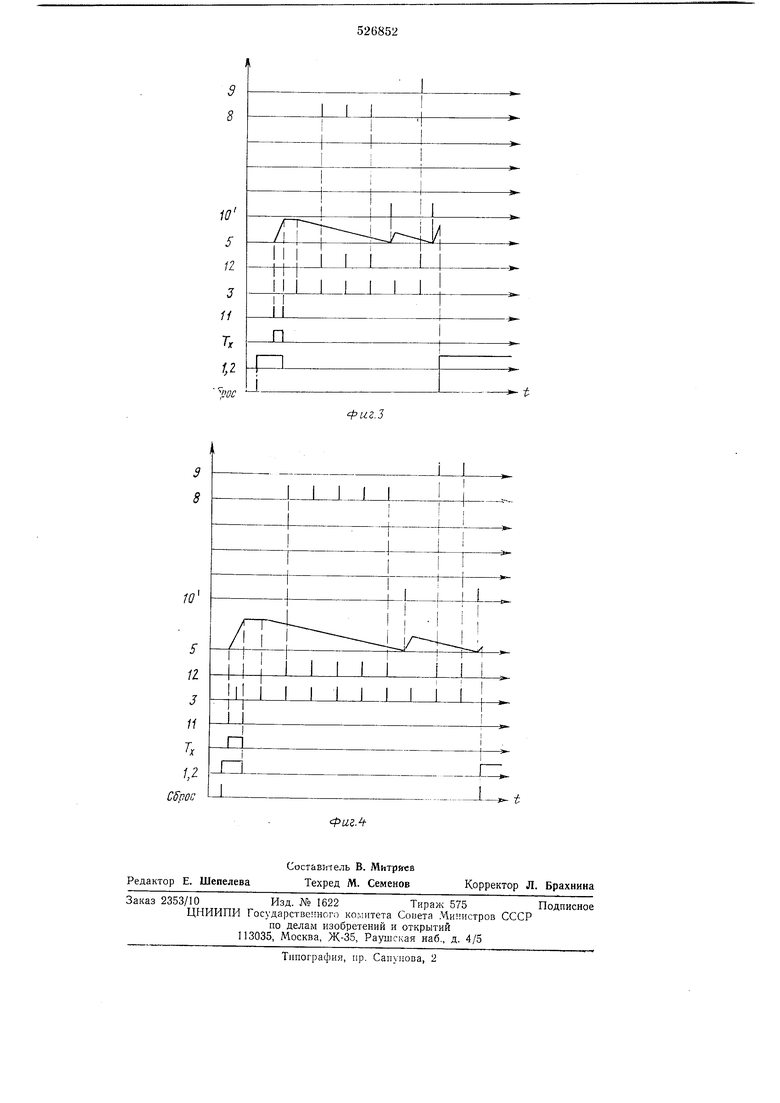

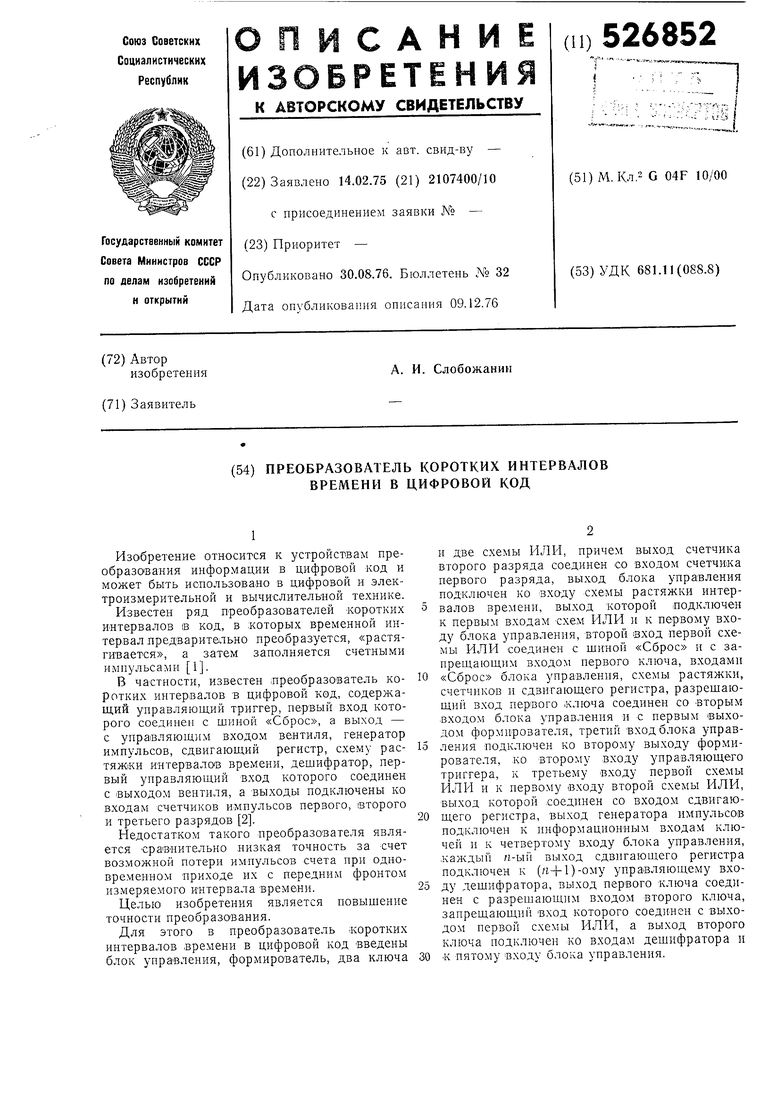

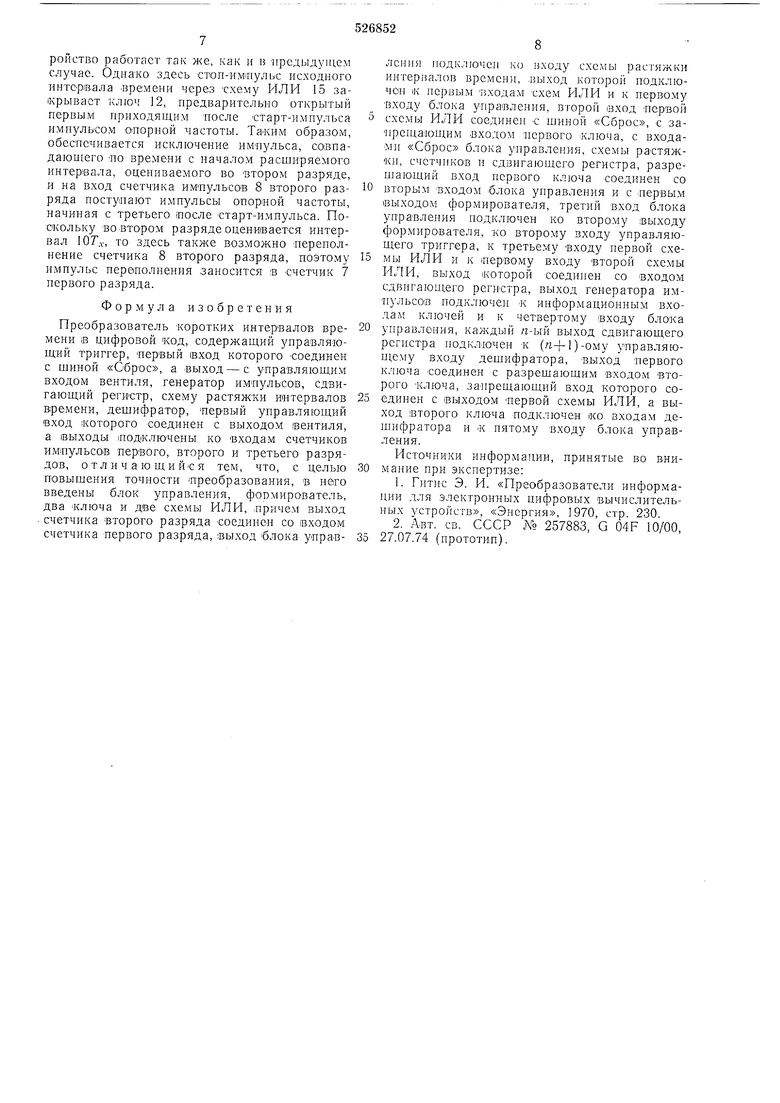

На фиг. 1 приведе1 а схема предлагаемого усрройства; на фиг. 2, 3, 4-временные диаграммы работы уетройетва.

Преобразователь коротких иитервалов вречмени в цифровой код еодержит управляющий триггер 1, первый 1вход которого соединен е шиной «Сброс, а выход - с управляющим входом веитиля 2, генератор имиульсов 3 опорной частоты с независимым возбужде«ием, сдвигающий регистр 4, схему растяжки интервалов времени 5, дешифратор 6, первый управляющий вход которого соединен с выходом вентиля 2, а выходы подключены ко входам счетчиков импульсов 7, 8, 9, нз которых последний имеет обратный порядок счета, блок управления 10, формирователь 11, ключи 12, 13 и схемы ИЛИ 14, 15. Выход счетчика второго разряда 8 соединен со входом счетчика первого разряда 7. Выход блока управления 10 подключен ко входу схемы растяжки интервалов времени 5, выход которой подключен к первым входам схем ИЛИ 14, 15 и к первому входу блока управления 10. Второй вход первой схемы ИЛИ 15 соедиисн с шиной «Сброс, с запрещающим входом первого ключа 13, с входами «Сброс блока управления схемы растяжки, -счетчиков и сдвигающего регистра, разрешаюпшй вход которого соедииен со вторым входом блочка управления 10 и с первым выходом формирователя 11, третий вход блока управления 10 подключен ко второму выходу формирователя 11, ко второму 1входу управляющего триггера 1, к третьему входу первой схемы ИЛИ 15 и к первому входу второй схемы ИЛИ 14, выход которой соединен со входом сдвигающего регистра 4; выход генератора импульсов 3 подключен к информационным входам ключей 12, 13 и к четвертому входу блока управления каждый rt-ый выход сдвигающего регистра 4 подключен к (л+1)-ому управляющему входу дешифратора 6. Выход первого ключа 13 соединен сразрешающим входом второго ключа 12, запрещающий вход которого соединен с выходом первой схемы ИЛИ 15. Выход второго ключа 12 подключен ко входам дешифратора 6 и к пятому входу блока управления .

Предлагаемое устройство работает следующим образом.

Перед преобразованием импульс «Сброс устанавливает устройство в исходное состояние. При этом управляющий триггер 1 - в единичном состоянии, следовательно, вентиль 2 открыт, ключи 12, 13 заперты, сдвигающий регистр 4 и счетчики импульсов 7, 8, 9 - в нулевом состоянии.

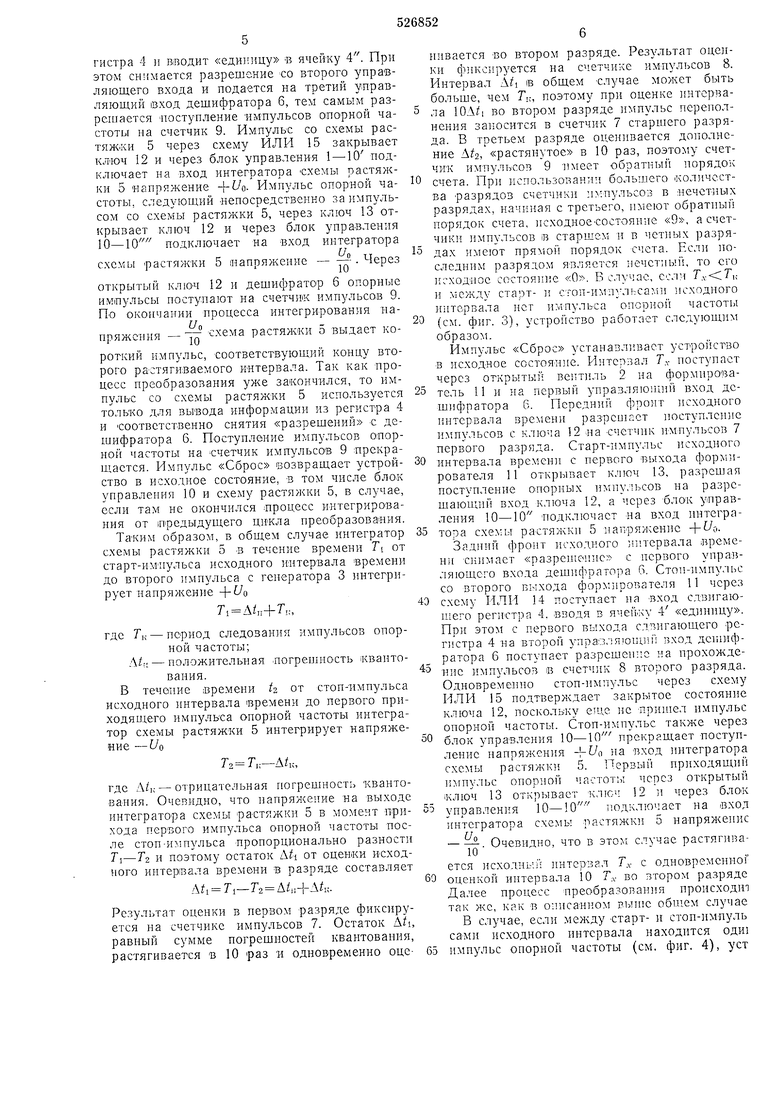

В общем случае между передним и задним фронта-ми исходного интервала времени Тх находится не менее двух импульсов опорной частоты (см. фиг. 2). Итак, интервал Тх поступает через открытый вентиль 2 на формирователь И и на первый управляющий вход дещифратора 6. При этом передний фронт

ПСХОД1101Ч) 1мггсрвала времени разрешает поступление импульсов с ключа 12 на счетчик импульсов 7 старшего разряда. Формирователь 11 формирует короткие импульсы, соответствующие началу и концу исходного инте-рвала времени. Старт-импульс исходного интервала времени с первого выхода формирователя 11 открывает ключ 13, разрешая поступление импульсов опорной частоты с генератора 3 на разрешающий вход ключа 12. Одновремен-но старт-импульс исходного интервала времени через блок управления 10-10 подключает на вход интегратора схемы растяжки интервалов времени 5 напряжение, например . Начинается процесс интегрир01вапия этого напряжения. Первый приходящий импульс опорной частоты после старт-импульса через открытый ключ 13 разрешает поступление импульсов с генератора 3 через ключ 12 па входы дешифратора 6. При этом опорные импульсы, начиная со второго, проходят через открытый первый вентиль дешифратора 6 па вход счетчика импульсов 7 первого разряда. Второй импульс опорной частоты после старт-импульса через ключ 12 поступает также на блок управления 10-10 , который прекращает поступление напряжения +f/o °па вход интегратора схемы растяжки интервалов времени 5.

Задний фронт исходного интервала времени с выхода вентиля 2 поступает на первый управляющий вход дешифратора 6 и запреп ает поступление импульсов с генератора 3 через ключ 12 на счетчик импульсов 7 старшсго разряда. Стон-импульс исходного интервала времени со второго выхода формирователя 11 через схему ИЛИ 14 поступает на вход сдвигающего регистра 4, -вводя в ячейку 4 «единицу. При этом с первого выхода

сдвигаюп;его регистра 4 на второй управляющий вход дешифратора 6 поступает разрешение и имп)льсы опорной частоты могут проходить на счетчик имиульсов 8 второго разряда. Одновременно стоп-импульс исходного

интервала времени через блок управлепия 10-10 подключает напряжение Uo на вход интегратора схемы -растяжки интервалов времени 5 п через схему ИЛИ 15 закрывает ключ 12. Первый импульс опорной частоты,

приходящий после стоп-импульса исходного интервала, через блок управлепия 10-10 подключает на вход интегратора схемы растяжки 5 напряжение - :;- . Этот же опорный

Юо

импульс через открытый ключ 13 открывает ключ 12, разрешая поступление опорных импульсов через дешифратор 6 на счетчик ИМПУЛЬСОВ 8 второго разряда. По окончании

f/o

процесса интегрирования напряжения-

схема растяжки 5 выдает короткий импульс, соответствующий концу первого растягиваемого интервала времени. Короткий импульс с выхода схемы -растяжки 5 через схему ИЛИ 14 поступает на вход сдвигающего регистра 4 и Вйодит в ячейку 4. При это снимается разрешение со второго управляющего входа и подается на третий управляющий вход дещифратора 6, тем самым разрешается поступлеиие импульсов опорной частоты и а счетчик 9. Импульс со схемы растяжки 5 через схему ИЛИ 15 закрывает ключ 12 и через блок управления 1 -10 подключает на вход интегратора схемы растяжки 5 напряжение . Имиульс опорной частоты, следующий непосредственно за импульсом со схемы растяжки 5, через ключ 13 открывает ключ 12 и через блок управления 10-10 подключает на вход интегратора

схемы растяжки 5 напряжение - -° . Через

открытый ключ 12 и дешифратор 6 опорные импульсы поступают на счетчик импульсов 9. По окончании процесса интегрирования напряжения схема растяжки 5 выдает корот1сий импульс, соответствующ.ий концу второго растягиваемого интервала. Так как процесс преобразования уже закончнлся, то импульс со схемы растяжки 5 используется только для вывода информации из регистра 4 и Соответственно снятия «разрешений с дешифратора 6. Поступление импульсов опорной частоты на -счетчик импульсов 9 прекращается. Импульс «Сброс возвращает устройство в исходное состояние, в том числе блок управления 10 и схему растяжки 5, в случае, если там не окончнлся процесс интегрирования от предыдущего цикла преобразовапия. Таким образом, в общем случае интегратор схемы растяжки 5 в течение времени Ti от старт-импульса исходного интервала времени до второго шшульса с геператора 3 интегрирует напряжение -{-Но

Т, А/п+Т„

где Гк - период следования импульсов опорной частоты;

- положительная погреппюсть квантования.

В течение времени tz от стон-импульса исходного интервала времени до первого приходящего импульса опорной частоты интегратор схемы растяжки 5 интегрирует напряжение - Uo

,

где A/I: - отрицательная г огрешность квантования. Очевидно, что напряжение на выходе интегратора схемы растяжки 5 в момент прихода первого импульса опорной частоты после стоп-И1шульса нропорнионально разности и поэтому остаток от оценки исходного интервала времени в разряде составляет

7,-Г2 А/„+А к.

Результат оценки в нервом разряде фиксируется на счетчике импульсов 7. Остаток , равный сумме погрешностей квантования, растягивается в 10 раз и одновременно оценивается во втором разряде. Результат оценки фиксируется на счетчике импульсов 8. Интервал в общем случае может быть больше, чем Г,;, поэтому при оценке интервала во втором разряде импульс переполнения заносится в счетчик 7 старшего разряда. В третьем разряде оценивается донолнение , «растянутое в 10 раз, поэтому счетчик импульсов 9 имеет обратный порядок

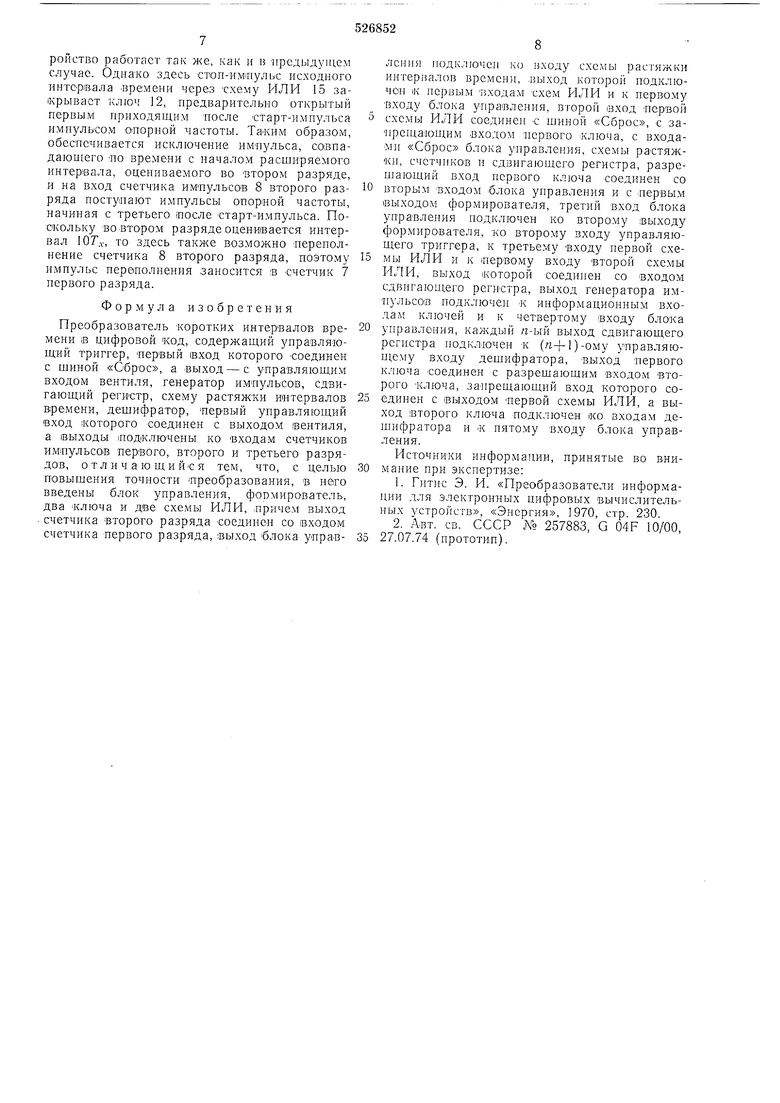

0 счета. Прн использовании большего количества разрядов счетчики ммпульсоз в нечетных разрядах, начиная с третьего, имеют обратный порядок счета, нсходноесостояние «9, а счетчики импульсов в старшем и в четных разря5дах имеют прямой порядок счета. Если последним разрядом является нечетный, то его исходное состояние «О. Б случае, если Тх,Т,; и между старт- н стоп-импульсамн исходного интервала нет импульса onopiioii частоты

0 (см. фиг. 3), устроГгство работает следующим образом.

Импульс «Сброс устанавливает устройсгво в исходное состояние. Интервал Г.у поступает через открытый вентиль 2 на формнрова5тель 11 и на первый управляющий вход дешифратора 6. Передннй фронт исходного интервала времени разрешает поступление нмиульсов с ключа 12 па счетчнк нмнульсов 7 первого разряда. Старт-нмнульс исходного интервала временн с первого выхода формирователя 11 открывает ключ 13, разрешая ноступленне опорных импульсов на разрешающнй вход ключа 12, а через блок управления 10-10 подключает на вход интегратора схемы растяжкн 5 напряжение ,.

5

Задний фронт исходного интервала времени ciiiiMaeT «разрен1енне с нервого управляющего входа дешифратора G. Стон-нмнульс со второго выхода .rфoвaтeля 11 через схему ИЛИ 14 поступает на вход сдвигаю0Hiero регистра 4. вводя в ячейку 4 «единицу. При этом с первого выхода сдвнгающего регистра 4 на второй упра:;з, Я}о1ДГ И вход деншфратора 6 поступает разрешение на прохожде5ние импульсов в счетчнк 8 второго разряда. Одновременно стоп-имнульс через схему ИЛИ 15 подтверждает закрытое состояние ключа 12, поскольку не приплел импульс опорной частоты. Стоп-импульс также через

0 блок управлення 10-10 прекращает постуцленне напряження Ч-Уо на вход интегратора схемы растяжкн 5. Первый приходящий нмнульс онорной частоты через открытый ключ 13 открывает клю-ч 2 и через блок управления 10-10 ;1одключает на вход интегратора схемы растяжкн 5 напряжение

-. Очевидно, что в этом случае растягивается исходный интервал Гд- с одновременно

0 оценкой интервала 10 Тх во втором разряде Далее процесс преобразования происходит так же, как в описанном вьпне обш.ем случае В случае, если между старт- и стон-импуль сами исходного интервала находится оди1 5 нмнульс опорной частоты (см. фиг. 4), уст

роиство раоотает так же, как и в предыдущем случае. Одиако здесь стоп-имтульс исходного интервала Времени через схему ИЛИ 15 заiKpbiBaeT ключ 12, иредварительно открытый первым нрнходящим после старт-импульса имнульсом опорной частоты. образом, обеспечивается исключение импульса, совпадающего ПО времени с началом расширяемого интервала, оцениваемого во втором разряде, и на вход счетчика импульсов 8 второго разряда поступают импульсы опорной частоты, начиная с третьего после Старт-импульса. Поскольку во втором разряде оценивается интервал lOr.v, то здесь также возможно переполнение счетчика 8 второго разряда, поэтому импульс переполнения заносится в счетчик 7 первого разряда.

Формула изобретения

Преобразователь коротких интервалов времени в цифровой код, содержащий управляющий триггер, первый вход которого €оедннен с щиной «Оброс, а выход - с управляющим входом вентиля, генератор импульсов, сдвигающий регистр, схему растяжки интервалов времени, дешифратор, первый управляющий вход которого соединен с выходом вентиля, а выходы (подключены ко входам счетчиков нмпульсов первого, второго и третьего разрядов, отличающийся тем, что, с целью повышения точности преобразования, в него введены блок управления, формирователь, два ключа и две схемы ИЛИ, .причем выход . счетчика второго разряда Соединен со входом счетчика первого разряда, выход блока управления подключен ко входу схсл1ы растяжки интервалов врел1ени, выход которой подключен 1К первым входам схем ИЛИ п к первому входу блока управления, второй вход первой схемы ИЛИ соединен с щпной «Сброс, с занрещаюЩим входом -первого ключа, с входаМи «Сброс блока управления, схемы растяжки, счетчиков и сдвигающего регистра, разрешающий вход первого ключа соединен со

вторым входом блока управления и с первым выходом формирователя, третий вход блока управления подключен ко второму выходу формирователя, ко второму входу управляющего триггера, к третьему входу первой схемы ИЛИ и к 1первому входу второй схемы ИЛИ, выход 1которой соедииен со входом сдвигающего регистра, выход генератора импульсов подключен К информациоппым входа.м ключей и к четвертому входу блока

управления, каждый /г-ый выход сдвигающего регистра подключен к (/г+1)-ому управляющему входу дешифратора, выход первого ключа соединен с разрешающим входом второго Ключа, зяПрещающий вход которого соединен с выходом -первой схемы ИЛИ, а выход второго ключа подключеН IKO входам дещифратора и к пятому входу блока управления.

Источники информации, принятые во внимание при экспертизе:

1.Гитпс Э. И. «Преобразователи информации для электронных цифровых вычислительных устройств, «Энергия, 1970, стр. 230.

2.Авт. св. СССР ЛЬ 257883, G 04F 10/00, 27.07.74 (прототнл).

..

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой частотомер | 2019 |

|

RU2730047C1 |

| Устройство для приема сигналов, закодированных с избыточностью | 1988 |

|

SU1605275A2 |

| Устройство для воспроизведения запаздывающих функций | 1983 |

|

SU1173424A1 |

| Преобразователь угла поворота вала в код | 1983 |

|

SU1121691A1 |

| Панорамный измеритель частоты | 1984 |

|

SU1267273A1 |

| УСТРОЙСТВО ИЗБИРАТЕЛЬНОГО ВЫЗОВА | 2005 |

|

RU2299525C1 |

| Устройство для поверки электрических секундомеров | 1986 |

|

SU1392543A1 |

| Интегрирующий аналого-цифровой преобразователь | 1989 |

|

SU1633493A1 |

| Цифровой измеритель временных интервалов | 1975 |

|

SU520563A1 |

| Многоканальный преобразователь угол-временной интервал | 1989 |

|

SU1716603A1 |

Авторы

Даты

1976-08-30—Публикация

1975-02-14—Подача