1

Изобретение относится к вычислительной технике и может использоваться в те.хнике аналого-цифровых преобразователей (АЦП).

Известен преобразователь аналог - код, содержащий АЦП, регистры тактов, тактовый генератор, дешифратор и устройство управления 1. Однако он обладает .малым быстродействием.

Известен аналого-цифровой преобразователь, содержащий трехфазный генератор тактовых и.мцульсов, регистр тактов, устройство сравнения, регистр результата, дешифратор, блок коррекции результата и декодирующий преобразователь, выход последнего соединен с первым входом схемы сравнения, к второ.му входу которой подключен выход источника преобразуемого напряжения, а выход ее соединен с первым входом регистра результата и с первым входом дешифратора, выход которого подключены к первому входу блока коррекции результата, выход последнего соединен с вторым входом регистра результата и вторы.м входом регистра тактов, выход которого цодключен к второму входу дешифратора, с третьим входом которого соединены выход регистра результата и вход декодирующего преобразователя, первый, второй и третий выходы генератора тактовых импульсов подключены соответственно к третьему входу схемы сравнения, к второму входу блока коррекции результата 2. При возникновении в цепях измерения кодируемой величины импульсных помех конечный результат преобразования может значительно отличаться от истинного результата.

Целью изобретения является повышение помехозащищенности аналого-цифрового преобразователя относительно импульсных помех, возникающих в цепях измерения кодир}емой

величины.

Это достигается тем, что в аналого-цифровой преобразователь, содержащий устройство управления, соединенное с блоком коррекции результата, регистром результата,

генератором тактовых импульсов и регистром тактов, выход которого подключен к одному из входов дешифратора, к другому входу которого подключен выход регистра результата, выход дешифратора соединен через блок коррекции результата с кoppeктиpyющи и входами регистра тактов и регистра результата, выход регистра результата через декодирующий преобразователь соединен с первым входом элемента сравнения, к второ.му входу которого подключен выход источника преобразуемого иаиряжения, а с третьим в.чодом элемента сравнения соединен первый выход генератора тактовых импульсов, введены счетчик числа импульсов опроса элемента сравнения,

счетчик числа срабатываний элемента сравнеПИЯ, блок логических элементов, вентили, триггеры, причем к едниичиому входу первого триггера иодключен выход элемента еравнепня, выход нервого триггера соединен с уиравляюгцим входом первого вентиля, к другому входу которого нодключен первый выход генератора тактовв1х нмпульсов, выход нервого вентн.чя нодк.иочен к счетному входу счетчика числа имнульсов опроса элемента сравнения, выход которого соединен с уиравля101ЦИМ входом второго вентиля, через втоpoii вход которого второй выход генератора тактоввьх нмпульсов подключен к установочному входу счетчика числа импульсов опроса элемента сравнения, к «нулевому входу первого трнггера и к установочному входу счетчика чнсла срабатываний элемента сравнения, к счетному входу которого нодключен выход элемента сравнения, первый выход счетчика чис.та срабатываний э;1емента сравнепня соедннен с уиравляюгцим входом третьего ве1ггпля, через второй вход которого третий выход генератора тактовых имиульсов подключен к тактовому входу регистра тактов, а к ч1)авляюпгему входу регистра тактов и первому входу блока логических элементов подк;1Ючеп выход второго трнггера, «едипичный вход которого соединен с вторым выходом счетчика числа срабатываппй элемепта сравнения, «нулевой вход второго триггера соедннен с первым выходом генератора тактов, выход ycrpoiicTBa унравленпя соединен с установочными входами счетчиков числа имиульсов опроса элемента сравнения, счетчика числа срабатываний элемента сравнения и нервого триггера, второй вход блока логических элементов соединен с выходом регистра тактов, а выход блока логических элементов подключен к соответствуюп1,ему входу регистра результата.

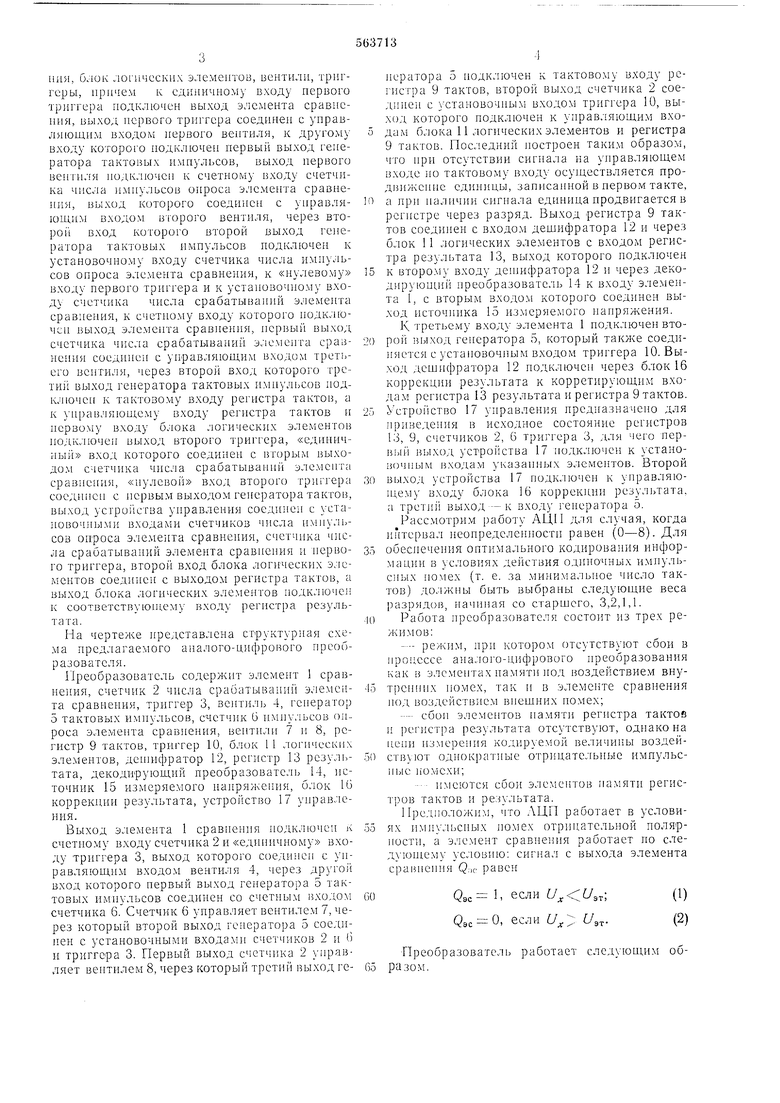

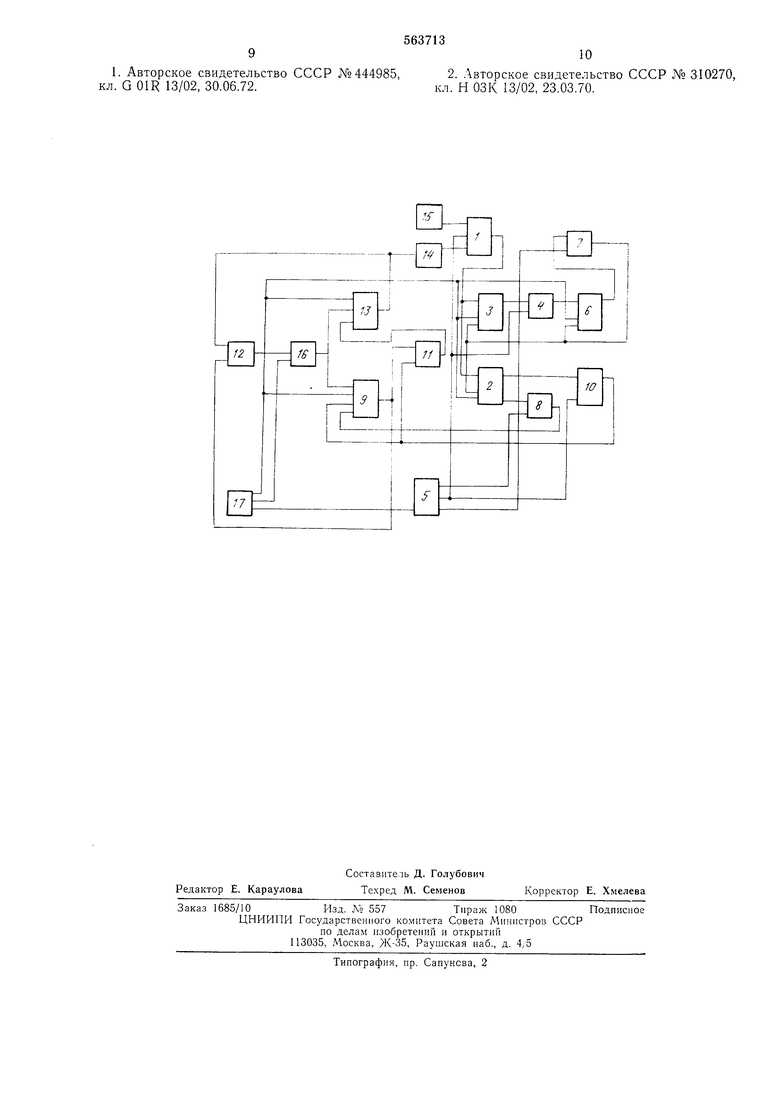

На чертеже представлена структурная схема предлагаемого аналого-ппфрового преобразователя.

Преобразователь содержит элемент 1 сравнения, счетчик 2 числа срабатывапнй элемента сравиеиия, триггер 3, ве1ггнль 4, геиератор 5 тактовых имиульсов, счетчик 6 нмнульсов f)nроса элемепта сравпения, вептплп 7 п 8, регистр 9 тактов, триггер 10, блок 11 логпческпх элементов, ден1ифратор 12, регпстр 13 результата, декодирующий преобразователь 14, нсточник 15 измеряемого напряжения, блок 16 коррекпии результата, устройство 17 унравления.

Выход элемепта 1 сравнения нодключеп к счетпому входу счетчика 2 и «единичпому входу триггера 3, выход которого соединен с управляющнм входо.м вентиля 4, через другой вход которого первый выход геператора 5 тактовых импульсов соединен со счетным входом счетчика 6. Счетчик 6 управляет вентилем 7, через который второй выход геператора 5 соеднпеп с устаповочпыми входами счетчиков 2 и fi и триггера 3. Первый выход счетчика 2 управляет вептилем 8, через который третий выход генератора о подключен к тактовому входу регистра 9 тактов, второй выход счетчика 2 соедппен с устаповочпым входом триггера 10, выход которого подключен к управляющим входам блока 11 логических элементов и регистра 9 тактов. Последний построен таки.м образом, что прп отсутствии сигпала па управляющем входе по тактовому входу осуществляется продвнженпе единицы, записанной в первом такте, а прп палпчни сигнала едиппна продвигается в регистре через разряд. Выход регистра 9 тактов соединен с входом дешифратора 12 и через блок 11 логических элементов с входом регистра результата 13, выход которого иодключен к второму входу деи1ифратора 12 и через декоднруюпип преобразователь 14 к входу элемепта 1, с вторым входом которого соедннеп выход источннка 15 из.меряемого иапряжепия.

К третьему входу элемепта 1 нодк.тючеп второй выход геператора 5, который также соединяется с установочным входом триггера 10. Выход дешифратора 12 иодключеп через блок 16 коррекции результата к корретирующим входа.м регистра 13 результата и регистра 9 тактов. Устро |ство 17 уиравлепия предпазначепо для приведенпя в исходное состояние регистров 13, 9, счетчиков 2, 6 триггера 3, для чего перBbui выход ycTpoiicTBa 17 подключеп к установочным входам указапных элементов. Второй выход устройства 17 подключеп к управляюпгему входу блока 16 коррекпии результата, а третий выход --к входу геператора 5.

Рассмотрим работу АЦП для случая, когда интервал иеоиределепиости равен (О-8). Для обеспечения оптимального кодировапия информации в условпях действия одипочных импульспых помех (т. е. за мипимальиое число тактов) должны быть выбрапы следующие веса разряде), начппая со старшего, 3,2,1,1.

Работа преобразователя состоит из трех режимов:

--- режим, прп котором отсутствуют сбои в процессе апалого-цпфрового преобразования как в эле.мептах памятп под воздействием виутрсппнх помех, так и в элементе сравнения под воздействием внешних иомех;

-- сбон элементов намяти регистра тактой п регистра результата отсутствуют, однако на цепи пзмерепня кодпруемой величипы воздействуют одпократпые отрицате.тьные импульсные помехи;

--- пмеются сбои элеме1ггов памятн регистров тактов и результата.

Предположим, что ЛЦП работает в условиях импульсных помех отрицательной полярности, а элемент сравнения работает по следуюпгему условию: сигнал с выхода элемепта сравнення Q;,c равен

Qge 1, если

(1) (2) Q,e 0, если и/- и,,.

Преобразователь работает следуюшим образом.

Устройство 17 управления вырабатывает две команды на начало кодирования: по первой устанавливаются в исходные «нулевые состояния триггер 3, счетчики 2 и 6, регистры 13 и 9, а по второй осуществляется запуск генератора 5, каждый такт которого включает три микротакта. На первом микротакте через вентиль 8 производится продвижение «единицы в соответствующих (/С-г1)-й или (/(-|-2)-й разряд регистра 9, который через блок 11 логических элементов устанавливает в «единичное состояние ()-й или (/(-г2)-й триггер в регистре 13 результата, унравляющий соответствующим разрядом декодирующего преобразователя 14, что соответствует добавке (Х+1)го или (/(4-2)-го эталона к ранее существовавшему эталонному напряжению. На втором микротакте осуществляется опрос элемента 1 сравнения, запись информации в счетчике 2 и 6 и устанавливается в «нулевое состояние триггер 10, а на третьем микротакте устанавливаются Б нулевое состояние триггер 3 и счетчики 2 и 6.

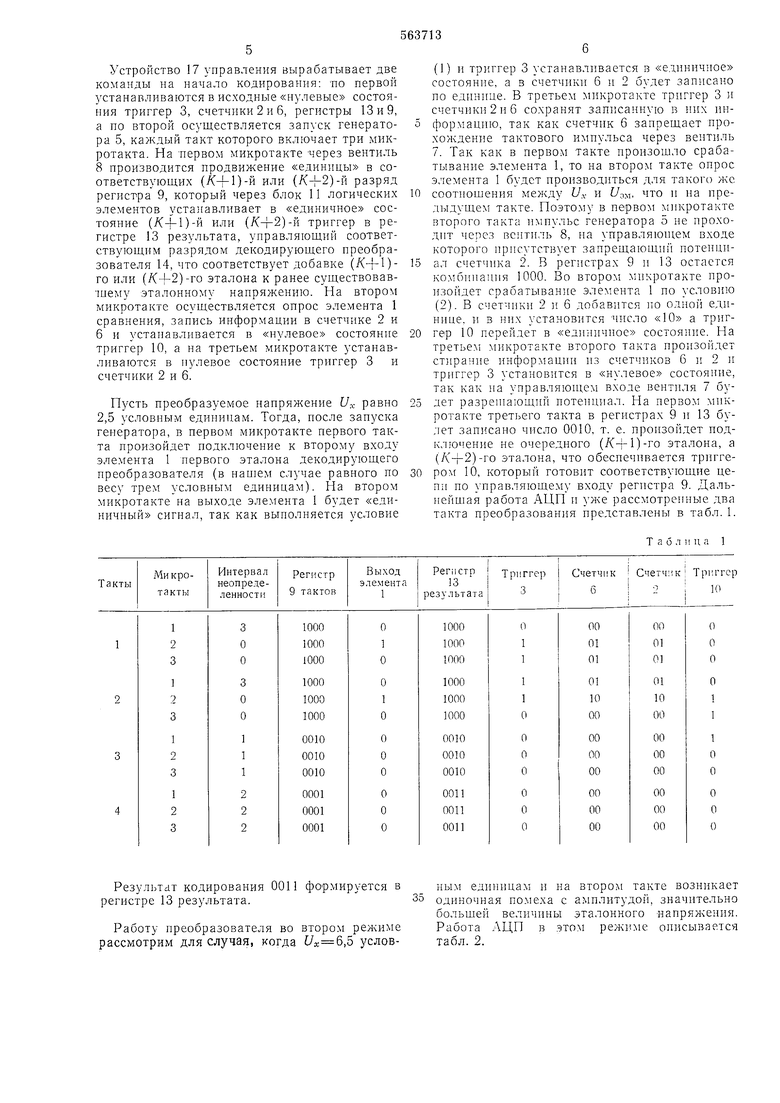

Нусть преобразуемое напряжение U равно 2,5 условным единицам. Тогда, после запуска генератора, в первом микротакте первого такта произойдет подключение к второму входу элемента 1 первого эталона декодирующего преобразователя (в напшм случае равного по весу трем условным единицам). На втором микротакте на выходе элемента I будет «единичный сигнал, так как выполпяется условие

(1) и триггер 3 устанавливается в «единичное состояние, а в счетчики 6 и 2 будет записано по единице. В третьем микротакте триггер 3 и счетчики 2и 6 сохранят записанную в них информацию, так как счетчик б запрещает црохождение тактового имиульса через вентиль 7. Так как в первом такте произощло срабатывание элемента 1, то на втором такте опрос элемента 1 будет производиться для такого же

соотношения между U и U, что и на предыдущем такте. Поэтому в первом микротакте второго такта импульс генератора 5 не проходцт через вентпль 8, ца управляющем входе которого присутствует запрещающцй потенццал счетчика 2. В регцстрах 9 ц 13 остается комбинация 1000. Во втором микротакте произойдет срабатывание элемента 1 по условию (2). В счетчики 2 ц 6 добавится по одцой единице, и в них установится число «10 а триггер 10 перейдет в «единичное состояние. На третьем микротакте второго такта произойдет стирание информаццц из счетчиков 6 и 2 и триггер 3 установится в «нулевое состояние, так как на управляюн1ем входе вентиля 7 будет разрешающий потенциал. На первом мнкротакте третьего такта в регистрах 9 ц 13 будет записано число 0010, т. е. произойдет подключение не очередного ()-го эталона, а ()-го эталона, что обеспечивается трпггером 10, который готовит соответствующие цепи цо управляющему входу регистра 9. Дальнейшая работа АЦН ц уже рассмотрецные два такта преобразования представлены в табл.1.

Т а б л II ц а 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1976 |

|

SU650077A1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ И ПЕРЕДАЧИ ПОСЛЕДОВАТЕЛЬНОСТИ СИГНАЛОВ | 2005 |

|

RU2299474C2 |

| Генератор случайных чисел | 1981 |

|

SU991421A1 |

| МОДУЛЬ ВВОДА-ВЫВОДА СИСТЕМЫ ЦИФРОВОГО УПРАВЛЕНИЯ | 1991 |

|

RU2032201C1 |

| Микропрограммное устройство управления | 1981 |

|

SU1005049A1 |

| УСТРОЙСТВО КОДИРОВАНИЯ И ПЕРЕДАЧИ СИГНАЛОВ | 2004 |

|

RU2282246C2 |

| Управляемый генератор случайных чисел | 1981 |

|

SU960812A1 |

| Цифровой генератор сигналов | 1984 |

|

SU1176442A1 |

| ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ АНАЛОГ - КОД | 1991 |

|

RU2027303C1 |

| Устройство для тестового контроля и диагностики цифровых модулей | 1989 |

|

SU1700557A1 |

Результат кодирования ООП формируется в регистре 13 результата.

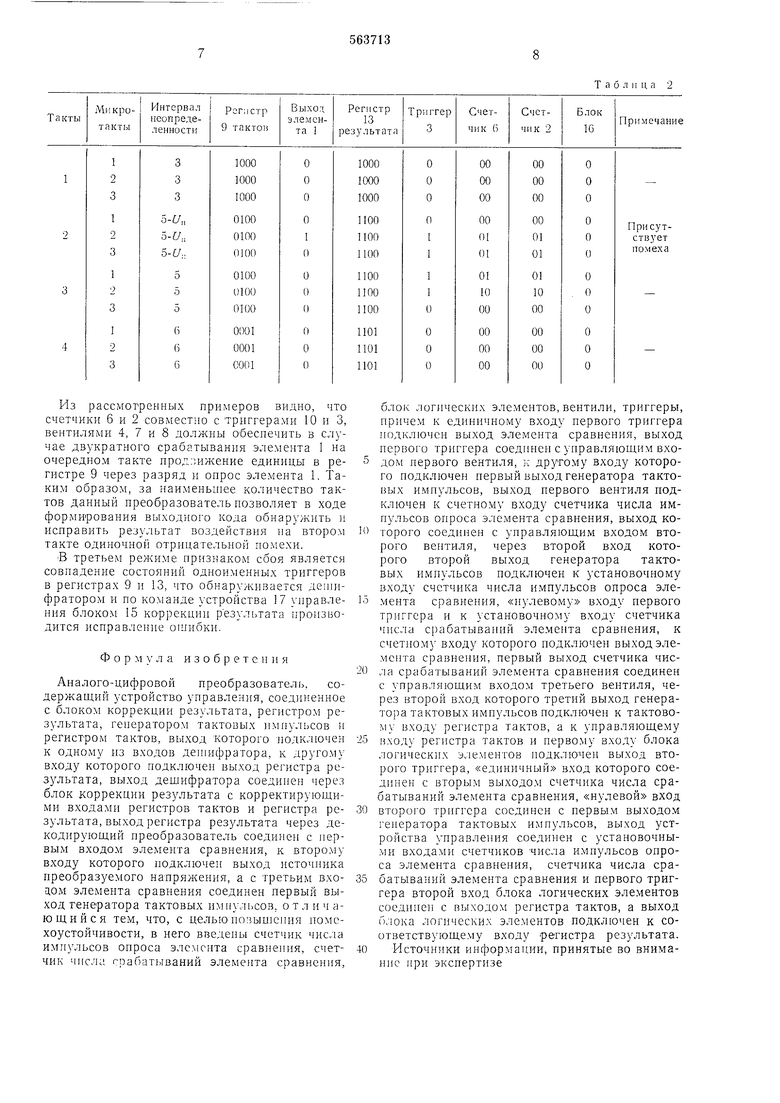

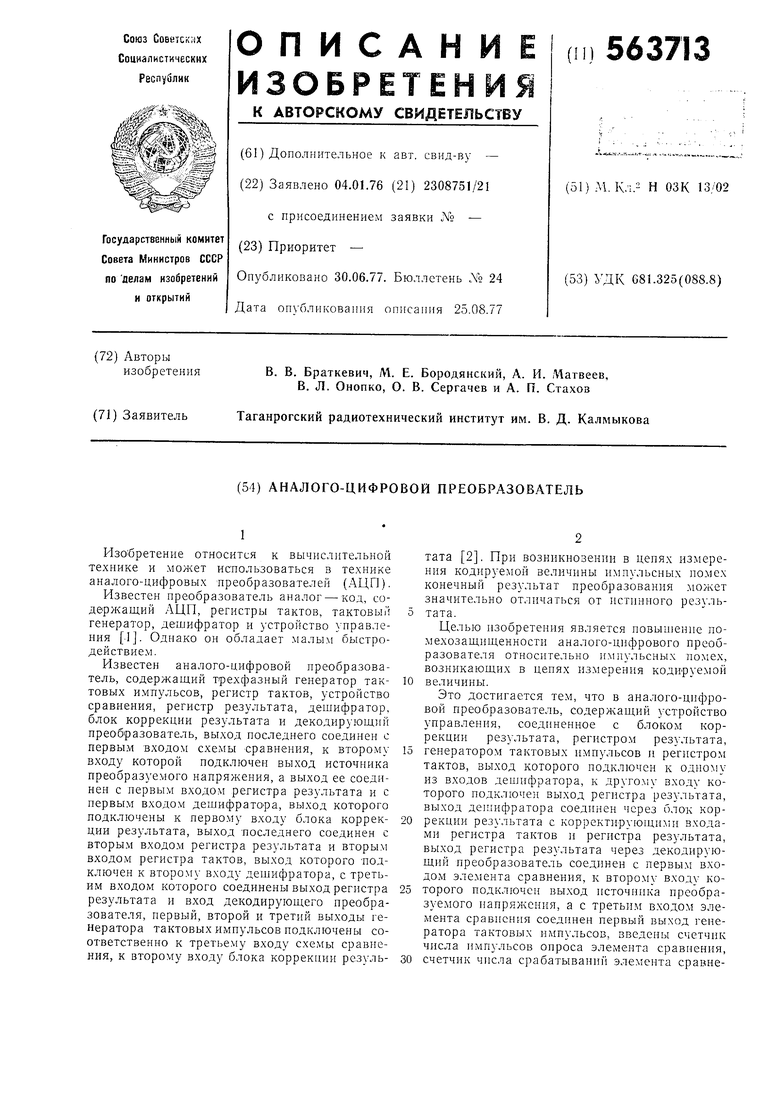

Работу преобразователя во втором режиме рассмотрим для случая, когда ,5 условным единицам и на втором такте возникает одиночная помеха с амплитудой, значительно большей величииы эталонного напряжения. Работа АЦН в чтом режиме описывается табл. 2.

Из рассмотренных примеров видно, что счетчики 6 и 2 совместно с триггерами 10 и 3, вентилями 4, 7 и 8 должны обеспечить в случае двукратного срабатывания элемента 1 на очередном такте нрод:;ижение единицы в регистре 9 через разряд и оирос элемента 1. Таким образом, за наименьшее количество тактов данный нреобразовательпозволяет в ходе формирования выходного кода обнаружить и исправить результат воздействия на втором такте одиночной отрицательной помехи.

В третьем режиме признаком сбоя является совпадение состояний одноименных триггеров в регистрах 9 и 13, что обнаруживается дешифратором и по команде устройства 17 управления блоком 15 коррекции результата производится исправленпе ошибки.

Формула и 3 о б р е т е и и я

Аналого-цифровой преобразователь, содержащий устройство управления, соединенное с блоком коррекции результата, регистром результата, генераторо.м тактовых импульсов п регистром тактов, выход которого цодключен к одному из входов деп1ифратора, к другому входу которого подключеп вы.код регистра результата, выход дешифратора соединен через блок коррекции результата с корректирующими входами регистров тактов и регистра результата, выход регистра результата через декодирующий преобразователь соединен с первы.м входом элемента сравнения, к второму входу которого подключен выход источника преобразуемого напряжения, а с третьим вхоцом элемента сравнения соединен первый выход генератора тактовых импульсов, от л ц ч ающийся тем, что, с целью иозыпшпия помехоустойчивости, в него введепы счетчик числа импульсов опроса элемента сравнения, счетчик числа срабатываний элеме}1та сравненпя.

блок логических элемептов, вентили, триггеры, причем к единичному входу иервого триггера подключен выход элемента сравнения, выход иервого триггера соедпнеи с уиравляющим входом первого вентиля, }: другому входу которого подключен первый выход генератора тактовых и.мпульсов, выход первого вентиля цодключен к счетному входу счетчика числа импульсов опроса элемента сравнения, выход которого соединен с управляющим входом второго вентиля, через второй вход которого второй выход генератора тактовых импульсов подключен к установочному входу счетчика числа и.мпульсов опроса элемента сравнения, «нулевому входу первого триггера и к установочному входу счетчика числа срабатываний элемента сравнения, к счетному входу которого подключен выход элемента сравнения, первый выход счетчика числа срабатываний элемента сравнения соединен с управляющим входом третьего вентиля, через второй вход которого третий выход генератора тактовых импульсов подключен к тактовому входу регистра тактов, а к управляющему

входу регистра тактов и иерво.му входу блока логических э.те.ментов нодключен выход второго триггера, «единичный вход которого соединен с вторым выходом счетчика числа срабатываний элемента сравнения, «нулевой вход

второго триггера соединен с первым выходом генератора тактовых импульсов, выход устройства управления соединен с установочны.ми входами счетчиков числа импульсов опроса элемента сравнения, счетчика числа срабатываний элемента сравнения и первого триггера второй вход блока логических элементов соединен с выходом регистра тактов, а выход блока логических элементов цодключен к соответствующе.му входу регистра результата.

Источники информации, принятые во внимание ири экспертизе

9 1. Авторское свидетельство СССР №444985, кл. G 01R 13/02, 30.06.72.

10 2. Авторское свидетельство СССР № 310270, кл. Н ОЗК 13/02, 23.03.70.

Авторы

Даты

1977-06-30—Публикация

1976-01-04—Подача