1

Изобретение относится к области полупроводниковых интегральных схем памяти и может быть использовано в оперативных ЗУ ЦВМ среднего и высокого быстродействия.

Известны ячейки памяти, представляющие собой триггер с нагрузочными и развязывающими транзисторами, выполненными в структуре с совмещенными диффузионными областями. Такая ячейка памяти изготовляется в одном изолированном кармане в эпитаксиальной пленке «-типа со скрытым сильно легированным «+-слоем, расположенной на подложке р-типа проводимости. В энитаксиальной пленке созданы базовые и инжектирующая области р-типа, причем каждая базовая область содержит по две коллекторные области. Скрытый п+-слой расположен под всей структурой и служит сильно легированным эмиттером п - р - «-транзисторов, которые в этом случае работают в инверсном режиме. Низкая Помехоустойчивость известной структуры обусловлена наличием больщих паразитных токов iB разрядных щинах.

Целью изобретения является разработка структуры ячейки памяти, совмещающей триггерные транзисторы с высокими инверсными коэффициентами усиления по току и развязывающие транзистор с низкими коэффициентами усиления. Это позволяет исключить паразитные токи и повысить помехоустойчивость.

Эта цель достигается за счет расположения сильно легированного скрытого слоя под инжектирующей областью и теми коллекторными областями, которые соединены с противоположными базовыми областями.

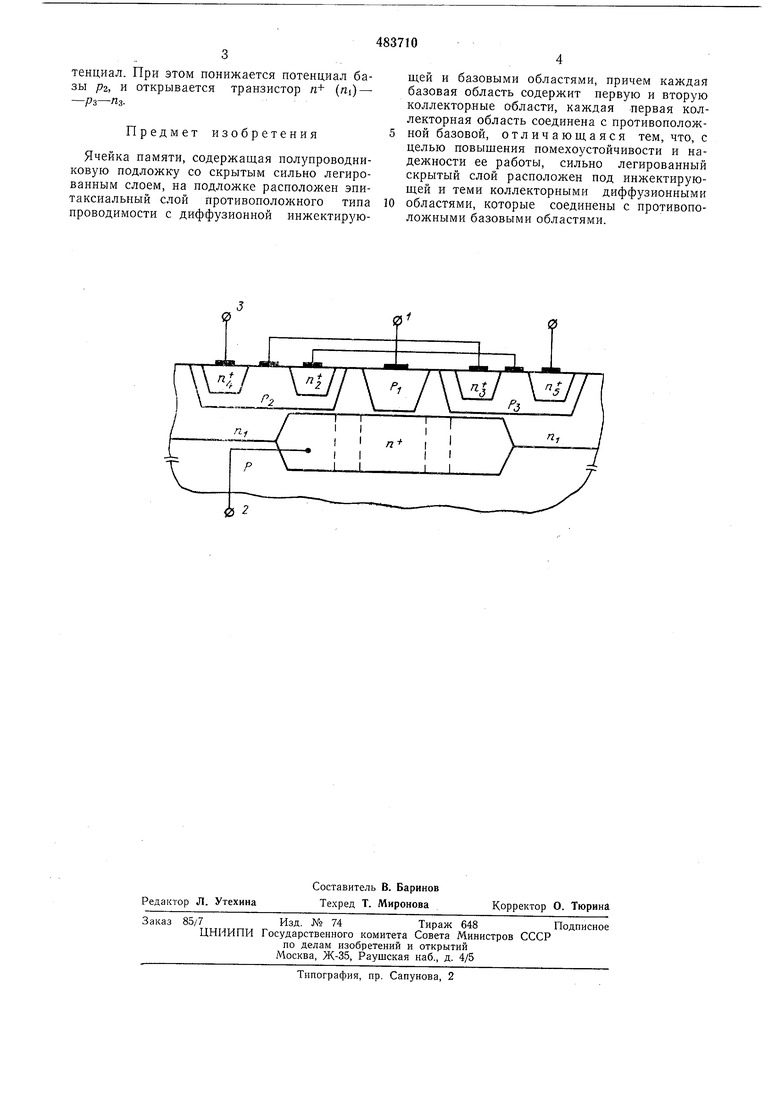

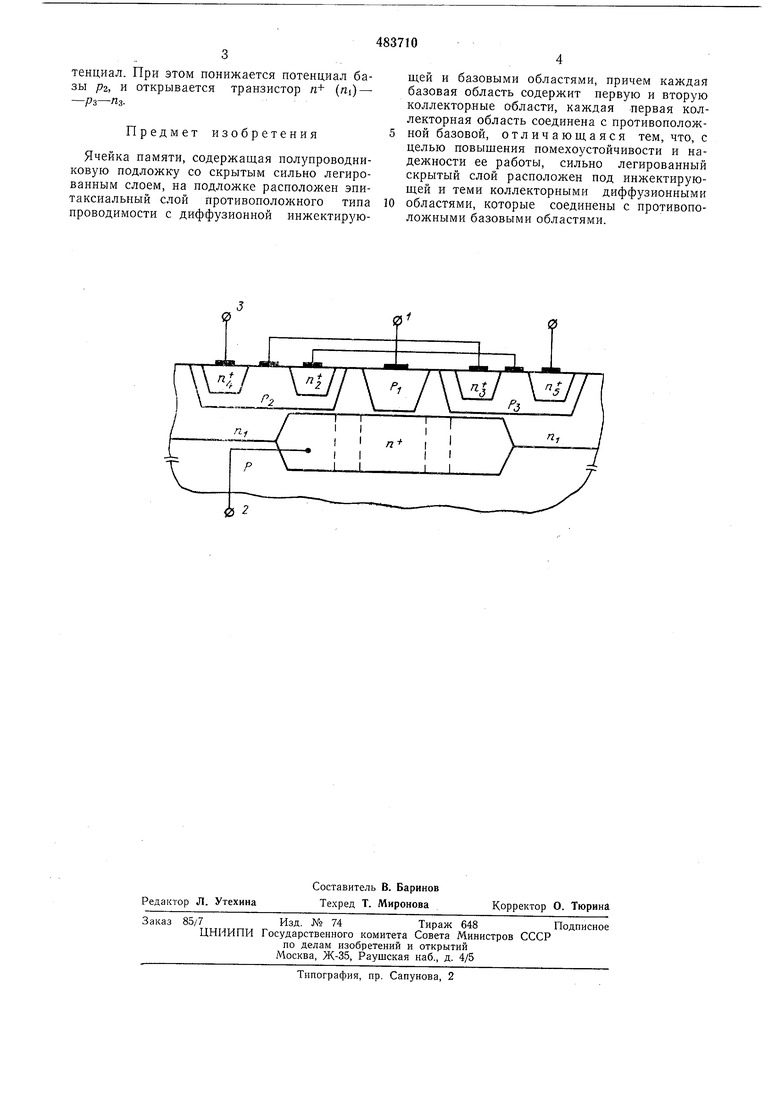

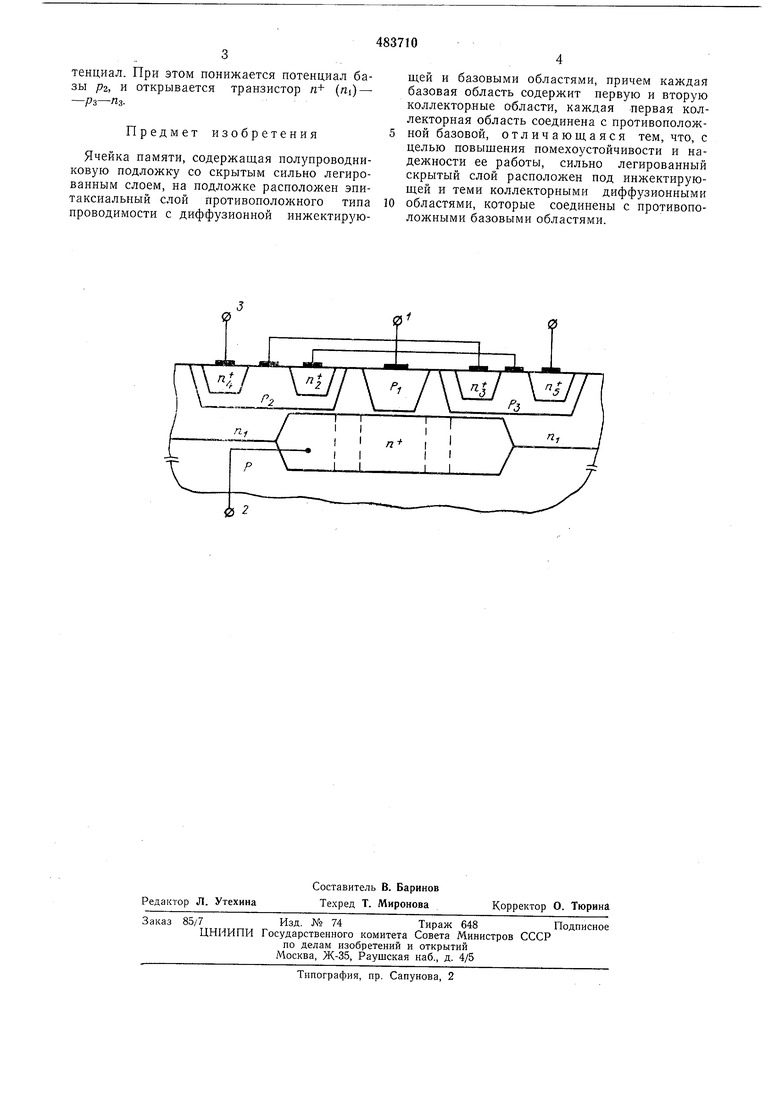

Структура ячейки памяти представлена на чертеже.

Ячейка содержнт полупроводниковую подложку р, эпитаксиальный слой «i со скрытым сильно легированным слоем п+, инжектирующую область р1, базовые области pz и рз, коллекторные области «2, Пз, «-„ «5, вывод инн ектора 1, шину адреса 2 и разрядные щины 3 и 4.

Ячейка памяти работает следующим образом.

В режиме хранения на щину 1 подается положительный потенциал, определяющий токовый режим работы схемы. Один из триггерных транзисторов «+(«0-Р2-«2 или «+(«) включен и насыщен, а другой (предполож-им, последний) выключен. Ири

считывании повышается потенциал на щине 1. При этом с включенного плеча триггера (на щине 3) снимается сигнал, определяющий хранимую информацию. Для записи информации на шину 4 подается открывающий потенциал. При этом понижается потенциал базы PZ, и открывается транзистор п+ (п) - -рз-пз.

Предмет изобретения

Ячейка памяти, содержащая полупроводниковую подложку со скрытым сильно легированным слоем, на подложке расположен эпитаксиальный слой противоположного типа проводимости с диффузионной инжектирующей и базовыми областями, причем каждая базовая область содержит первую и вторую коллекторные области, каждая первая коллекторная область соединена с противоположной базовой, отличающаяся тем, что, с целью повышения помехоустойчивости и надежности ее работы, сильно легированный скрытый слой расположен под инжектирующей и теми коллекторными диффузионными областями, которые соединены с противоположными базовыми областями.

| название | год | авторы | номер документа |

|---|---|---|---|

| Полупроводниковый прибор | 1974 |

|

SU626713A3 |

| КОМПЛЕМЕНТАРНАЯ БИПОЛЯРНАЯ СХЕМА И - НЕ (ВАРИАНТЫ) | 1993 |

|

RU2094910C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ САМОСОВМЕЩЕННОГО ВЫСОКОВОЛЬТНОГО ИНТЕГРАЛЬНОГО ТРАНЗИСТОРА | 2012 |

|

RU2492546C1 |

| ПОЛУПРОВОДНИКОВАЯ СТРУКТУРА | 1990 |

|

RU1699313C |

| Матричный накопитель для постоянного запоминающего устройства | 1977 |

|

SU734807A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ГОРИЗОНТАЛЬНЫХ БИПОЛЯРНЫХ ТРАНЗИСТОРОВ | 1988 |

|

SU1537071A1 |

| Способ изготовления высокочастотных транзисторных структур | 1983 |

|

SU1114242A1 |

| ЭЛЕМЕНТ ПАМЯТИ | 1992 |

|

RU2018994C1 |

| Полупроводниковое устройство | 1974 |

|

SU640686A3 |

| БиКМОП-ПРИБОР И СПОСОБ ЕГО ИЗГОТОВЛЕНИЯ | 2003 |

|

RU2282268C2 |

Авторы

Даты

1975-09-05—Публикация

1973-05-29—Подача