1

Изобретение относится к вычислитель:ной техиике.

КзЕестен интегратор, содержащий гход ной, Еыходной и два разрядных ключа, интегрирующий и суммирующий усилители, формирователь управляющих сигналов, цифро-аналоговый преобразователь, интегрирующий усилитель и двоичный счетчик.

Первый и второй выходы входного ключа соединены соответственно с входами первого и второго интегрирующих усилителей, а выходы последних через первый и второй входы выходного ключа подключены

к одному из входов суммирующего УСИЛИТ&ля и. одновременно к двоичному счетчику через первый и второй управляющие входы формирователя управляющих сигналов, два управляющих выхода которого подсоединенык входному и выходному ключам, а два другие через, разрядные ключи к управляюuuiM входам интегрир.ощих усилителей. Два выхода двоичного счетчика подключены через соответствующие входы цифро-аналогового преобразователя к входам суммируюuiero усилителя. Выход суммирующего усилителя является выходом устройства в аналоговой форме.

Цель изобретения - упрощение устройства и повышение его надежности, благодаря устранению аналого-ци4ровых узлов.

Достигается это благодаря тому, что интегратор содержит интегрирующий усилитель, в цепь обратной связи которого последова- телыю с конденсатором включен ключ, ди4 ференциальный усилитель, выход которюго через ключ соевинен с входом первого интегрирующего блок$, а его выход подклю чен к одному входу сумматора, второй вход сумматора подключен к пороговому устройству, выход которого соединен с входом управления. Выходы блока управления подключены к входу интегрирующего уситштеля и к управляющему входу второго интегрирующего блока, другой вход которого соедикан с источником входного сигнала.

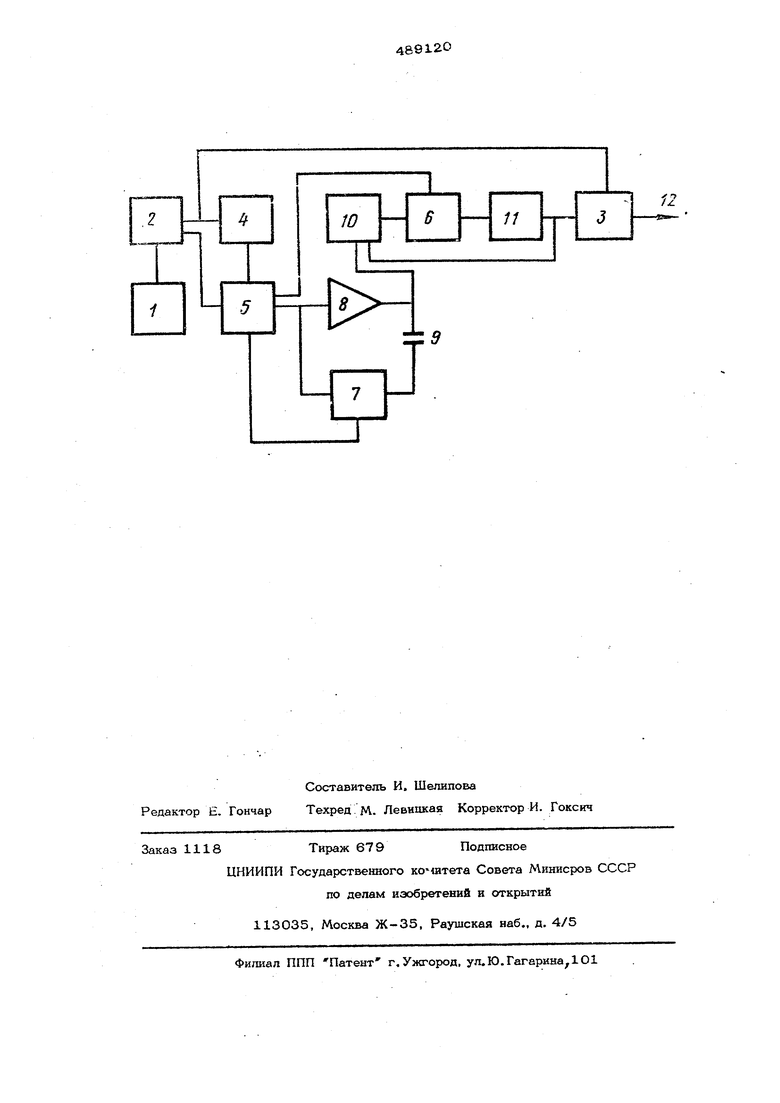

На чертеже приведена блок-схема оредлагаемого интегратора. Источник входного сигнала 1 через интегрирующий блок 2 соединен с одним входом сумматора 3 и пороговым устройством 4, выход которого

подключен к блоку управления 5, связанного о управляющим входом интегрирующего блока 2, а также с управляющими входами ключей 6, 7. Один из выходов блока управления 5 соединен с входом интегрирующего усилителя 8, в цепь обратной связи которого включены последовательно соединенные конденсатор 9 и ключ 7, выход усилителя В подключен к рдному входу дифференциального усилителя 1О, соединенного через ключ 6 с интегрирующим блоком 11, выход последнего соединен с вторыми входами диЬференциального усилителя 10 и сумматора 3, с клеммы 12 которого снимается выходной сигнал.

Устройство работает следующим образом. Интегрирующий блок 2 интегрирует входной сигнал источника 1. В момент,когда напряжение на выходе интегрирующего блока 2 достигает згщанного уровня, срабатывает пороговое устройство 4. В результате с порогового устройства 4 задается импульс на запуск блока управления 5, который замыкает ключи 6, 7 с. на вход усилителя 8 поступает импульс заданной амперсекундной площади, в результате чего конденсатор 9 заряжается. Полярность имYIyльca зависит от полярности выходного напряжения блока 2.

Напряжение с выхода усилителя 8 сравнивается с помощью дифференциального усилителя 10 с напряжением на выходе интегрирующего блока 11. При наличии разницы разностный сигнал, усиленный усилителем 1О, интегрируется блоком 11 до достижения момента равенства, при этом напряжение на входе интегрирующего блока 11 становится равным нулю.

Одновременно с замыканием ключей 6,

7и подачей импульса на вход усилителя 8 блок управления 5 переводит интегрирующий блок 2 на новый цикл интегрирования.

8этот момент напряжение на выходе интегрирующего блока 2 скачком падает до нуля, а на выходе интегрирующего блока 11 практически скачком возрастает так, что сигнал на выходе сумматора 3 оказывает ся все время пропорциональным интегралу от входного напряжения.

В следующий момент ключи 6, 7 размыкаются. Напряжения на блоке 11 и конденсаторе 9 запоминаются. Вследствие ареАфа и утечек входныг каскадов напряжение на интегрирующем блоке изменится. Для введения поправки блок 5 на короткое время замкнет ключи 6, 7 и усилитель 1 устранит рассогласование, после чего ключи вновь разомкнутся.

При новом переполнении интегрирующего блока 2 вновь замыкаются ключи 6, 7, подает я импульс на вход усилителя 8, осуществляется переход интегрирующего блока 2 на очередной цикл, после чего ключи 6, 7 замыкаются, Чероз определенные интервалы осуществляется коррекция напряжения на выходе блока 11 и т.д.

Если суммарное время, необходимое для корректировки интегрирующего блока 11, сделать достаточно малым по сравнению с временем интегрирования входного сигнала, то практически максимальное время интегрирования будет определяться емкостью конденсатора 9, а также сопротивлениями утечки ключа 7 и конденсатора 9. Данная схема может успещно применяться для точного интегрирования как быстро, так и медленно протекающих процессов. Максимальное время интегрирования более Ю /сек.

Предмет изобретения 0-.;

Интегратор, содержащий интегрирующие блоки, сумматор; блок управлениг:, пороговое устройство, ключи, управляющие входЬт которых подключены к выходу блока ynpafe 5тления, отличающийсятем, что, с цепью по %ыщения надежности и упрощения конструкции интегратора, он содержит интегрирующий усилитель, в цепь обратной связи которого последовательно с конденсатором включен ключ, дифференциальный усилитель, выход которого через ключ соединен с входом первого интегрирующего блока, выход которого подключен к одному входу сумматора, второй вход сумматора подключен к пороговому устройству, выход которого соединен с входом блика управления, выходы блока управления подключены к входу интегрирующего усилителя и к управляющему вхоау второго интегрирующего блока, другой вход которого соединен с источни- . ком входного сигнала.

11

| название | год | авторы | номер документа |

|---|---|---|---|

| I ВСГГСО'ЭЗНЛЯ I ДИСКРЕТНО-АНАЛОГОВЫЙ ИНТЕГРАТОР]|]ДТГ[{Т! Л :'Тк;^;Г v-^:^ | 1973 |

|

SU370614A1 |

| Дискретно-аналоговый интегратор | 1986 |

|

SU1372337A1 |

| КУЛОНОМЕТРИЧЕСКАЯ УСТАНОВКА | 1997 |

|

RU2120625C1 |

| АНАЛОГОВЫЙ ИНТЕГРАТОР | 2014 |

|

RU2571618C1 |

| Дискретно-аналоговый интегратор | 1976 |

|

SU611218A1 |

| Аналоговый интегратор | 1983 |

|

SU1128271A1 |

| ИНТЕГРАТОР | 1990 |

|

RU2020580C1 |

| Устройство для автоматической компенсации емкостного тока однофазного замыкания на землю | 1982 |

|

SU1107215A1 |

| Функциональное интегрирующее устройство | 1977 |

|

SU732903A1 |

| Компенсационный акселерометр | 2020 |

|

RU2738877C1 |

.9

Авторы

Даты

1975-10-25—Публикация

1974-04-26—Подача