tlft) V 1Г3

Изобретение относится к аналоговой Н1,1чис.пительно11 технике и может быть иснольтопано для интегрирования сиг- )a:ioii в широком временном диапазоне.

Цель изобретения - новьпиение точности интегрирования.

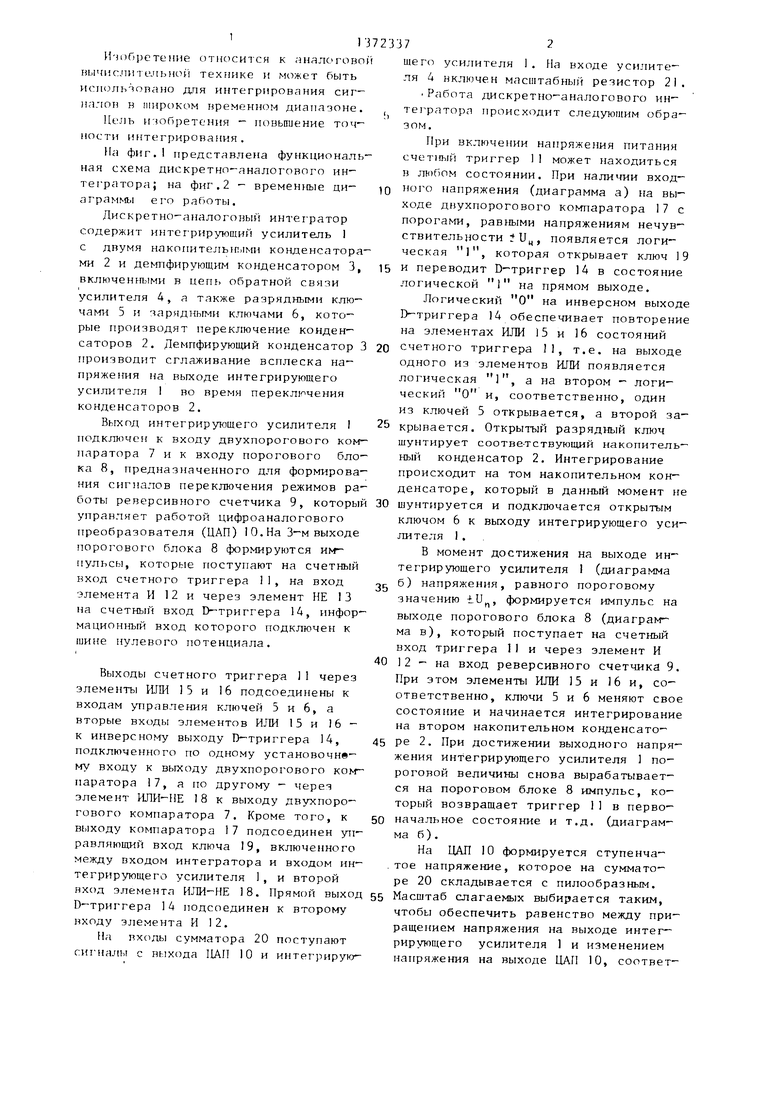

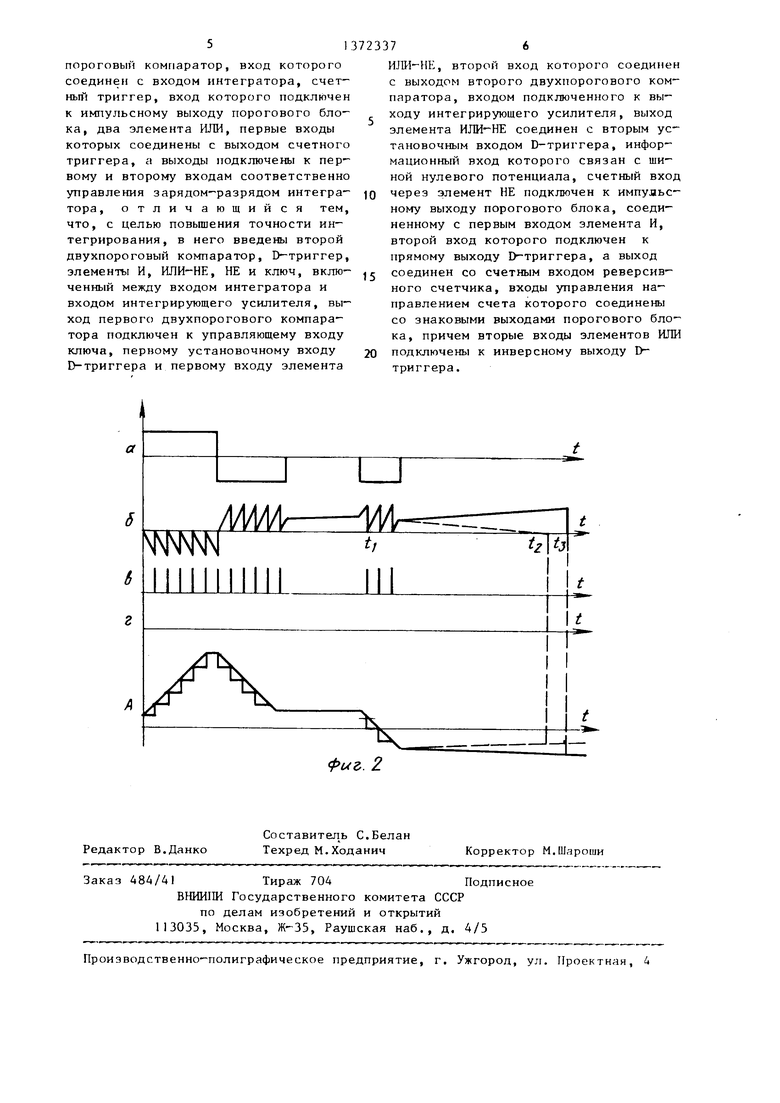

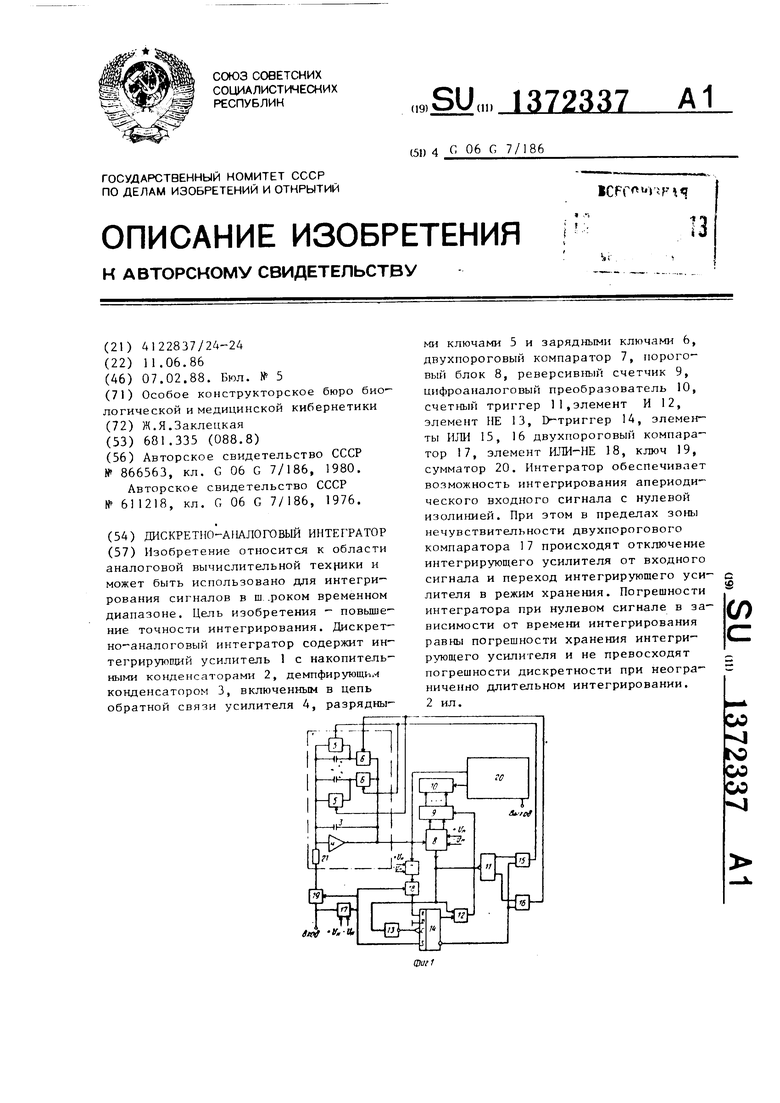

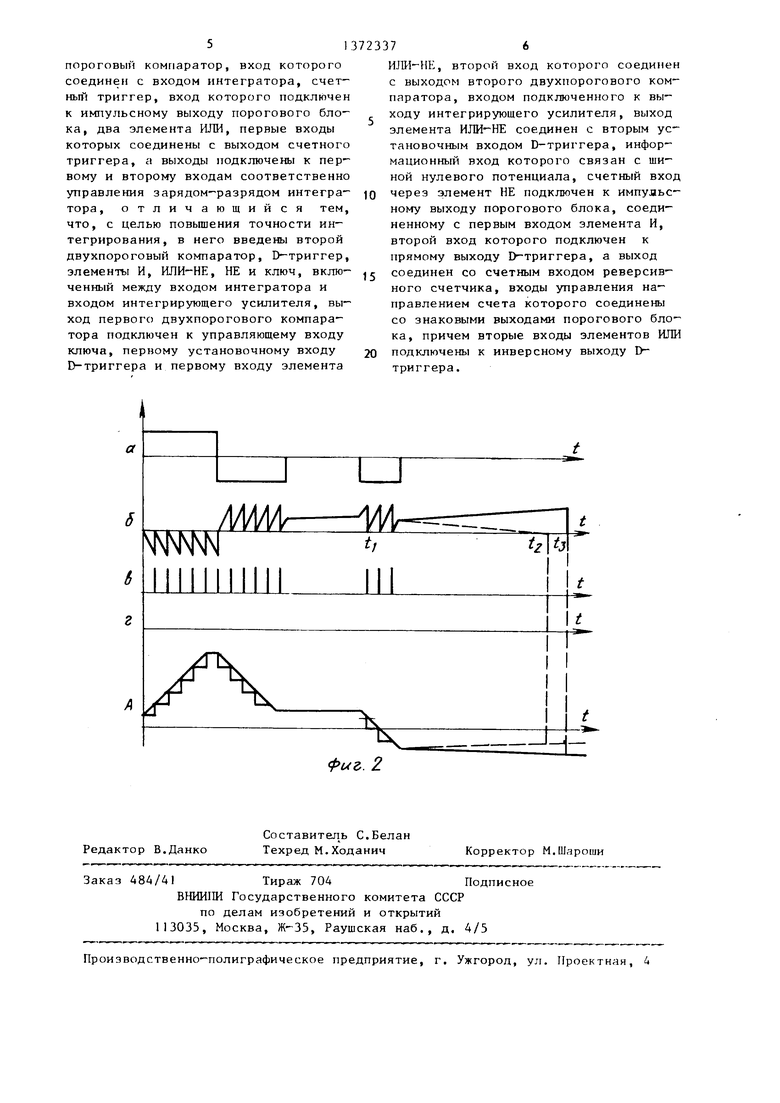

На фиг.1 гтредставлена функциональная схема дискретно-аналогового интегратора; на фиг.2 - временные диаграммы его работы.

Дискретно-аналоговый интегратор содержит интегрирующий усилитель I с двумя накопительн)1ми конденсаторами 2 и демпфирующим конденсатором 3, включенными в цеп1 обратной связи усилителя 4, а также разрядными ключами 5 и зарядными ключами 6, которые производят переключение конденсаторов 2. Демпфирующий конденсатор 3 производит сглаживание всплеска напряжения на выходе интегрирующего усилителя I во время переключения конденсаторов 2.

Выход интегрирующего усилителя I подключен к входу двухпорогового компаратора 7 и к входу порогового блока 8, предназначенного для формирования сигналов переключения режимов работы реверсивного счетчика 9, который управляет работой цифроаналогового преобразователя (ЦАП) I 0.На 3-м выходе порогового блока 8 формируются импульсы, которые поступают на счетный вход счетного триггера 11, на вход элемента И 12 и через элемент НЕ 13 на счетный вход D-триггера 14, информационный вход которого подключен к шине нулевого потенциала.

Выходы счетного триггер-а 1 1 через элементы ИГШ 15 и 16 подсоединень к входам управления ключей 5 и 6, а вторые входы элементов ИЛИ 15 и 16 - к инверсному выходу D-триггера 14, подключенного по одному установочнв- му входу к выходу двухпорогового компаратора 17, а по другому - через элемент ИЛИ-НЕ 18 к выходу двухпоро- гового компаратора 7. Кроме того, к выходу компаратора 17 подсоединен управляющий вход ключа 19, включенного между входом интегратора и входом интегрирующего усилителя 1, и второй нход элемента ИЛИ-НЕ 18. Нрямой выход D-триггера 14 подсоединен к второму входу элемента И 12.

Fla входы сумматора 20 поступают сигналы с вых(зда ЦАН 10 и интегрирую-

72

щего усилителя 1. На входе усилителя 4 включен масштабный резистор 21. Работа дискретно-аналогового интет ратора происходит следующим образом.

Нри включении напряжения питания счетный триггер 11 может находиться в любом состоянии. При наличии вход-

ного напряжения (диаграмма а) на выходе двухпорогового компаратора 17 с порогами, равными напряжениям нечувствительности и„ , появляется логическая 1, которая открывает ключ 19

и переводит D-триггер 14 в состояние логической 1 на прямом выходе.

Логический О на инверсном выходе D-триггера 14 обеспечивает повторение на элементах ИЛИ 15 и 16 состояний

счетного триггера 11, т.е. на выходе одного из элементов ИЛИ появляется логическая 1, а на втором - логический О и, соответственно, один из ключей 5 открывается, а второй закрывается. Открытый разрядный ключ шунтирует соотве-тствующий накопительный конденсатор 2. Интегрирование происходит на том накопительном конденсаторе, который в данный момент не

шунтируется и подключается открытым ключом 6 к выходу интегрирующего усилителя I .

В момент достижения на выходе интегрирующего усилителя I (диаграмма

б) напряжения, равного пороговому значению iU, формируется импульс на выходе порогового блока В (диаграмма в), который поступает на счетный вход триггера 11 и через элемент И

12 - на вход реверсивного счетчика 9. При этом элементы ИЛИ 15 и 16 и, соответственно, ключи 5 и 6 меняют свое состояние и начинается интегрирование на втором накопительном конденсатоPS 2. При достижении выходного напряжения интегрирующего усилителя 1 пороговой величины снова вырабатывается на пороговом блоке 8 импульс, который возвращает триггер 11 в перво-

начальное состояние и т.д. (диаграмма б).

На ЦАП 10 формируется ступенча- тое напряжение, которое на сумматоре 20 складывается с пилообразным.

Масштаб слагаемых выбирается таким, чтобы обеспечить равенство между приращением напряжения на выходе интегрирующего усилителя 1 и изменением напряжения на выходе ЦАП 10, соответствующего приращению кода на выходе счетчика на единицу младшего разряда При этом погрешность дискретности практически равна нулю (диаграмма д)

Если полярность в-ходного сигнала положительна, то пороговый блок 8 пе реключает реверсивный счетчик 9 на режим вычитания, если же входное напряжение отрицательной полярности, то реверсивный счетчик 9 переходит на режим сложения.

Если входное напряжение близко к нулевому, то срабатывает компаратор 17, закрывает ключ 19 и отключа- ет вход интегрирующего усилителя, обеспечивая режим хранения в интегрирующем усилителе на том значении напряжения, которое соответствовало моменту срабатывания компаратора 17, а выходное на11ряже ше суммирующего усилителя также сохраняет значение, предшеств: тощее появлению входного нулевого напряжения. При этом напряжении снимается установочный сигнал S на D-триггере 14, что обеспечивает возможность его срабатывания при появлении на его счетном входе импульса. Такой импульс может появиться тогда, когда напряжение на выходе ин тегрируюи1его усилителя за счет напряжения и тока смещения достигает пороговой величины порогового блока 8 - момент времени t (диаграмма б).

Импульс с порогового блока обеспечивает прохождение информационного сигнала О на прямой выход D-тригге- ра 14. Момент времени срабатывани} D-триггера 14 соответствует заднему фронту импульса порогового блока 8, так как при поступлении на счетный вход триггера импульс инвертируется на элементе НЕ. Появление логического О на выходе D-триггера после окончания импульса на пороговом блоке запрещает прохождение импульсов через элемент И 12, пропустив на его выход один импульс.

Одновременно после окончания импульса элементы ИЛИ 15 и 16 сигналом с выхода триггера 14 переведутся в одинаковое положение ,при котором откроются все ключи , запрещая дальнейшее интегрирование на интегрирующем усилителе j . Лальнейшее изменение напряжения на выходе суммирующего усилителя при входном нулевом сигнале запрещается и на нем поддерживается состоя-

10

15

20

25

30

35

0

5

0

5

ние, соответствующее коду реверсивного счетчика, равному N 1 , где N - код в срабатывания порогового блока 8.

При неограниченно долгом значении входного напряжения в пределах зоны нечувствительности ±UH порогового блока 8 напряжение на выходе суммирующего усилителя не изменится.

Если значение напряжения и тока смещения таково, что величина напряжения интегрирующего усилителя 1 изменяется в сторону отрицательных напряжений (пунктирная линия на диаграмме б), то в момент достижения значения порога нечувствительности на компараторе 7 последний срабатывает, вырабатывая значение, соответствующее логическому О, а на выходе элемента ИЛИ-ПЕ 18 появится сигнал, устанавливающий триггер 14 по входу R в положение логического О, действуя далее аналог: чно на элементы ИЛИ 15 и 16 и далее на ключи интегрирующего усилителя. При этом на ЦАП 10 сохраняется значение кода, равное N. Это значение сохраняется и на суммирующем усилителе.

Если время появления высокого входного сигнала меньще времени дозаряда накопительных конденсаторов до пороговой величины или перезаряда до достижения нулевого значения за счет напряжения и тока смещения, то на D-триггере 14 вновь появляется сигнал установочного входа и обеспечивается нормальный режим функционирования (момент времени t., диаграмма б). Таким образом, погрещность на выходе сумматора при нулевом входном сигнале соответствует погрешности интегрирующего усилителя в процессе хранения и не превосходит значения одного - кванта ЦАП 10 при неограниченно длительном хранении.

Формула изобретения

Дискретно-аналоговый интегратор, содержащий интегрирующий усилитель, выход которого подключен к входу порогового блока и первому входу сутч- матора, выход которого является выходом интегратора, реверсивный счетчик, выход которого через цифроанало- говый преобразователь подключен к второму входу сумматора, первый двух-

пороговый компаратор, вход которого соединен с входом интегратора, счетный триггер, вход которого нодключен к импульсному выходу порогового блока, два элемента ИЛИ, первые входы которых соединены с выходом счетного триггера, а выходы подключены к первому и второму входам соответственно управления зарядом-разрядом интегра- тора, отличающийся тем, что, с целью повышения точности интегрирования, в него введены второй двухпороговый компаратор, D-триггер, элементы И, ИЛИ-НЕ, НЕ и ключ, вклю- ченный между входом интегратора и входом интегрирующего усилителя, выход первого двухпорогового компаратора подключен к управляющему входу ключа, первому установочному входу D-триггера и первому входу элемента

ШВ-1-НЕ, второй вход которого соединен с выходом второго двухпорогового компаратора, входом подключенного к выходу интегрирующего усилителя, выход элемента ИЛИ-НЕ соединен с вторым установочным входом D-триггера, информационный вход которого связан с шиной нулевого потенциала, счетный вход через элемент НЕ подключен к импульсному выходу порогового блока, соединенному с первым входом элемента И, второй вход которого подключен к прямому выходу D-триггера, а выход соединен со счетным входом реверсивного счетчика, входы управления направлением счета которого соединены со знаковыми выходами порогового блока, причем вторые входы элементов ИЛИ подключены к инверсному выходу триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ измерения времени установления выходного сигнала цифроаналоговых преобразователей и устройство для его осуществления | 1987 |

|

SU1494216A1 |

| Дискретно-аналоговый интегратор | 1976 |

|

SU611218A1 |

| Интегратор | 1988 |

|

SU1728871A1 |

| Цифровой измеритель температуры | 1988 |

|

SU1583757A1 |

| Гибридное интегрирующее устройство | 1985 |

|

SU1316008A1 |

| Аналого-цифровой преобразователь | 1987 |

|

SU1481887A1 |

| Устройство для определения степени затухания измерительных магнитоэлектрических преобразователей | 1988 |

|

SU1628028A1 |

| I ВСГГСО'ЭЗНЛЯ I ДИСКРЕТНО-АНАЛОГОВЫЙ ИНТЕГРАТОР]|]ДТГ[{Т! Л :'Тк;^;Г v-^:^ | 1973 |

|

SU370614A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ СОВМЕЩЕННОГО ИНТЕГРИРОВАНИЯ | 1992 |

|

RU2036559C1 |

| Аналого-дискретное интегрирующее устройство | 1975 |

|

SU556463A1 |

Изобретение относится к области аналоговой вычислительной техники и может быть использовано для интегрирования сигналов в ш .роком временном диапазоне. Цель изобретения - повыше ние точности интегрирования. Дискрет- но-аналоговый интегратор содержит ин- тегрирутопщй усилитель 1 с накопитепь ными конденсаторами 2, демпфирующим конденсатором 3, включенным в цепь обратной связи усилителя 4, разрядными ключами 5 и зарядными ключами 6, двухпороговый компаратор 7, пороговый блок 8, реверсивный счетчик 9, цифроаналоговый преобразователь 10, счетный триггер 11,элемент И 12, элемент НЕ 13, D-триггер 14, элементы ИЛИ 15, 16 двухпороговый компаратор 17, элемент ИЛИ-НЕ 18, ключ 19, сумматор 20. Интегратор обеспечивает возможность интегрирования апериодического входного сигнала с нулевой изолинией. При этом в пределах зоны нечувствительности двухпорогового компаратора 17 происходят отключение интегрирующего усилителя от входного сигнала и переход интегрирующего уси- Ci лителя в режим хранения. Погрешности интегратора при нулевом сигнале в зависимости от времени интегрирования равны погрешности хранения интегрирующего усилителя и не превосходят погрешности дискретности при неограниченно длительном интегрировании. 2 ил. И (Л

фиг. 2

| Аналого-цифровой интегратор | 1980 |

|

SU866563A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Дискретно-аналоговый интегратор | 1976 |

|

SU611218A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-02-07—Публикация

1986-06-11—Подача