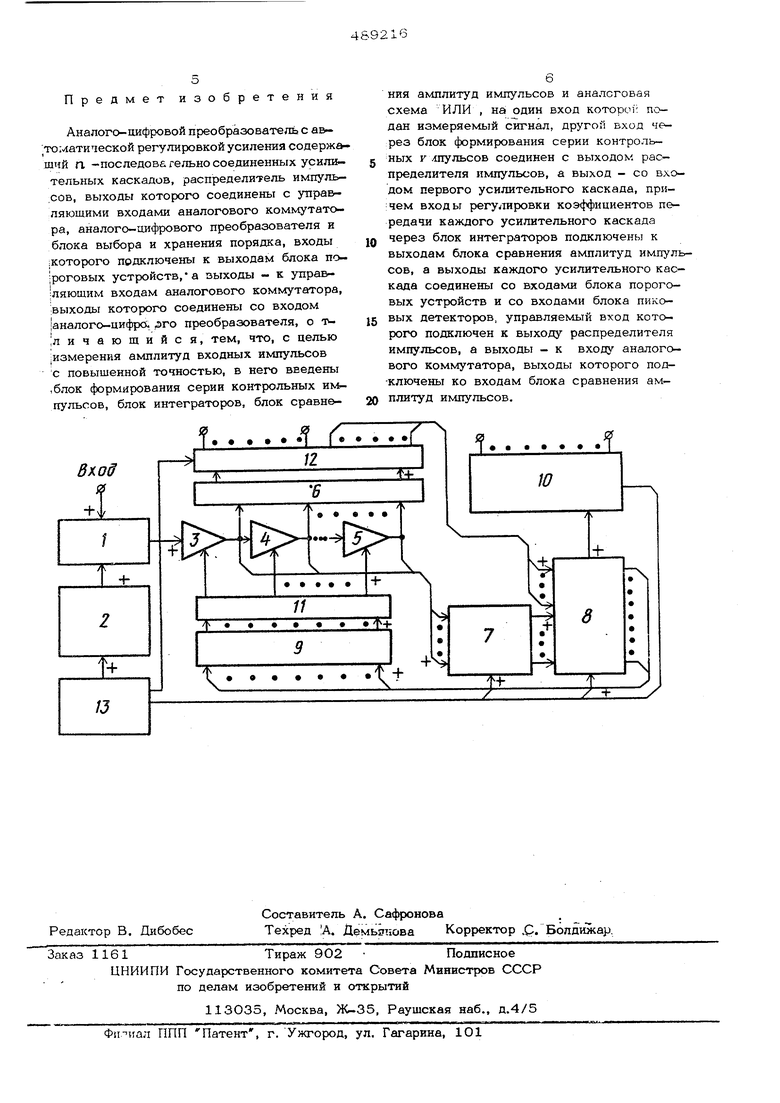

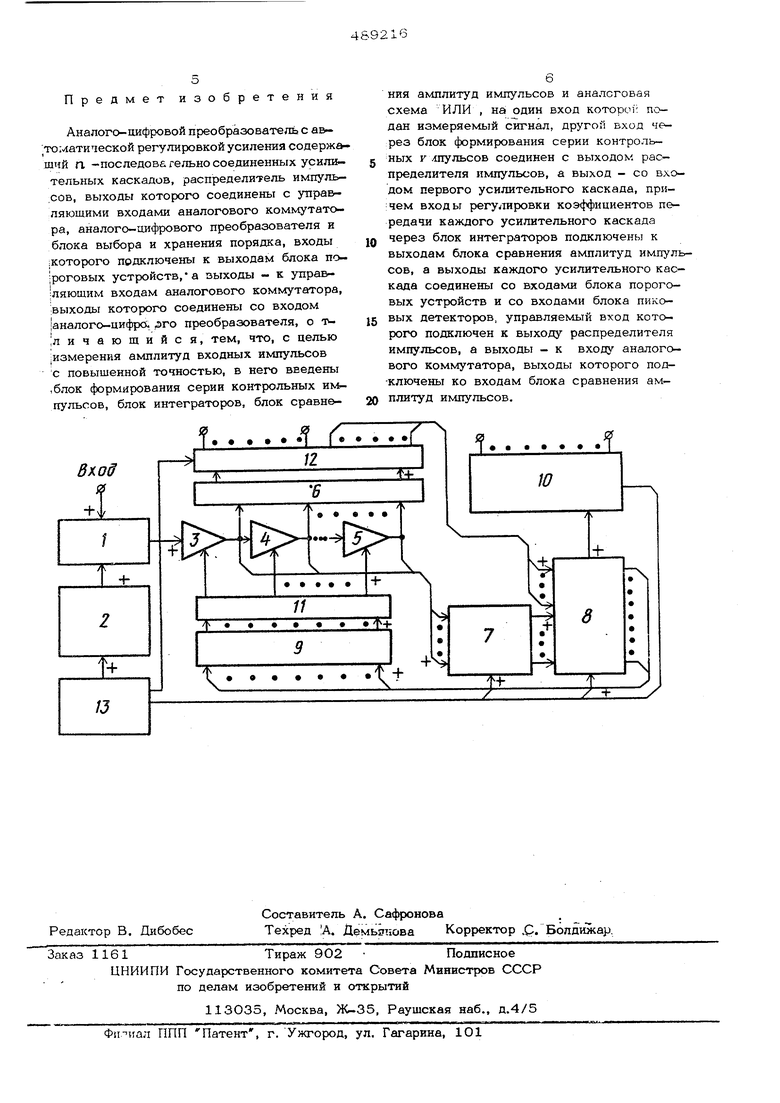

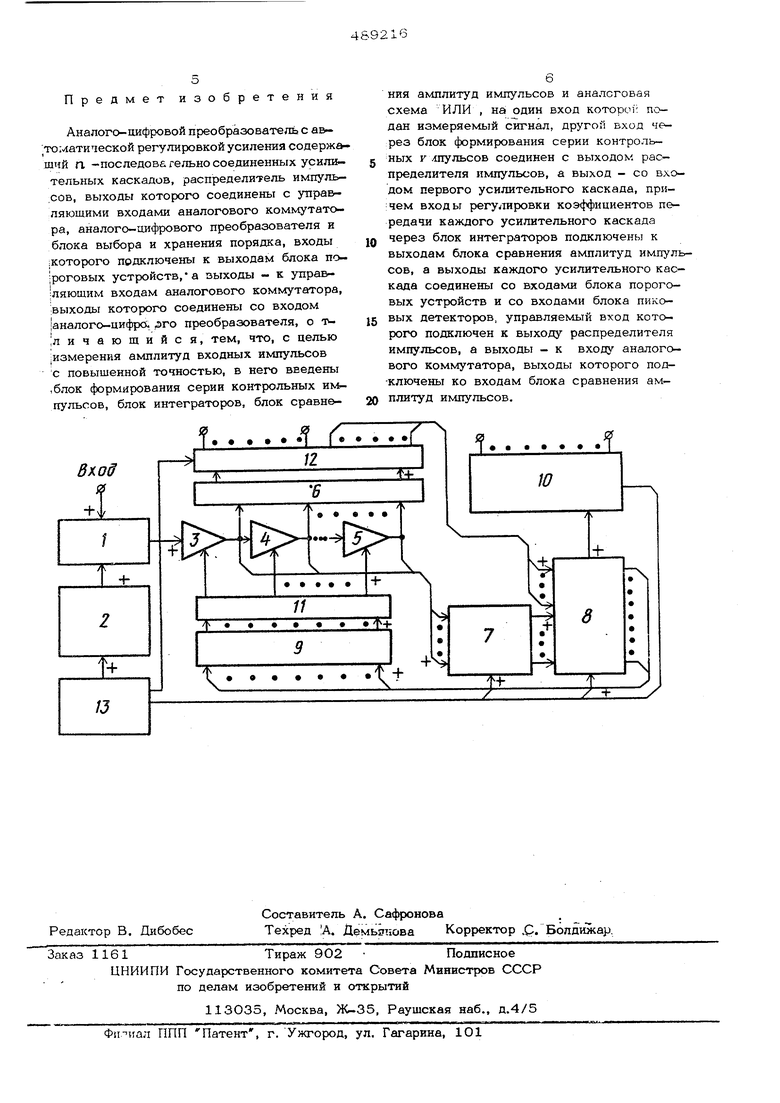

сигнал, ьторой вход пош-слючен х выходу бка 2 формирования серии кэнтролькьгх импульсов, а выход связан со Б;ШДОМ имгглчьного усилителя, состоящего из последоватено соединенных усилнтсл;-иых каскадов 3, и о с регулируе лым коэффициентом передачи, выходы которых подключен;- ко входам блока 6 пороговь Х устройств и входам блок., 7 пиковых детекторе-. Ььг:,сдь1 -тослед- него связаны со зходаЬШ екаао- ологс ко -л утатора 8, который сзсими ьыходамк соединен со БХОЯЗК ; блоаа 9 сравнакия а.-п литуды Hiva rynbccfc и ан ::ого--1.лфроього преобразователя 10. Bbjxofib: блоха 9 подключены ко входам бпокв. 11 кнтагаато- ров, который свг;зак ЕЬХодами с упоазля-

юишми Бxoдa ш усилитальнь х кэскадоз 3, 4, 5, Вьгходы 6 nopoio; ::,iк устроустсоединены со входами 12 зысора я хранения ггсрядка, а Еых.:;дьг гаслед;;его Бходэг- аиоГсо; osor-o :ъом:му. 8, Выходы распредгл -тедя J й-/-пупьсов связаньг с упрделк щк ли ;;;ходами блока 12, блохе 7 пзтко:-,.:. детэктороз. блока 2 формировани:- cepi,.; коктрспьны

имгпгльсов к ака:гЮГ -инфдозогС :ifX V-o:viy-a« тора 8,

Входной имшльс поступйг;-:: десез акалогозую схему ИЛР 1 на дход пеоьиго усилительного кас1и:.да :о, Зыходные хд ггульсы ycajiHTejrb bj : с,;-:;:ьдоп 3 ::: с

одновреманно поступахг ;:-а зколо; блоха S пороговых устройств iv t;j;OKa } пиковых детекторов. В блоке 7 а 4ллигудь импульсов запоминаются, а Е 6 пор-оговых устройств определяю-тся Hvmy.TbCb;, превь сиЕШие пороговый уровень, зьлде которого импулось ycилйБa;:ДiC I :лелкнейко, В блоке 12 акалйзхрухсас реаультать блока 6 ):ЮрО1ОЗЬ;Х yCipO :-: -. Б и ЗЬСХУа ;1СЯ

номер каскада )1ос,;:едме:: о .гд...;.;л / ; ахо- да кмлульсясго yc:d.;:.K-raJ::ii;; рабо-га лдэго в линейкой облает :. .-.;логоav,;:;. ;::ся-му.татор 8 соединяет аналс-гс-ддфрОл;с,;: i./p©обраэователь 10 с тем :vbaoaof,i б;:о1-,г. 7 пиковых детекторов, который хранхт ак-плитупу KTvraynbca с вь-:-сод.а у- ;-лк1Х ьно -о каскада, вь;бранного бдсКом -.Я аьйора и хранения порядка. 1Чя.г;:с-гс-.д;,Г;; ; преобразователь 10 ;;ресбрйз;ет зду ад т;плитуду в цифровой Есд. Псрядск дсгаравен яоряякоэок.су номеру одного да .; литепьных иаскалоз 3, - ; 5 SB :.д.::хо- де которого нмлульс имеет у :адс -:гльдсо значение, не преЕыиаюиюе урооннь эгсанкченкЯ; запрмккаефся г, увктардог.-- коде,

Таким Q6pu3Oiv;., входной скгяед задо--мкнается в полупогаркфлличесдой ipopv-vq : основанием систвлД счислеккЕ, чисдендс оавным коэойжцаекту у :длйния усилительного каскада.

По окончан1 и процессов восстановления чувствительности усилителя с выхода распределителя 13 управляющих и 4щ дьсов поступает импульс запуска на вход блока 2, который формирует серию ко трольных импульсов. Число контрольных импульсов равно числу управляемых каскадов усиления, а отношение амплитуды каждого из последующих импульсов к амплитуде предыдущего равно основанию счисления причем aMnnHi-yna последнего из серии имд/льсоБ равна отношению эталонного напряжения к основанию системы счисления. Контрольные ик«пульсы поступают через схему ИЛИ на вход усилительного каскада 3. Первый импульс серии предназначен для контроля усиления первого, считая от выхода усилителя каскада усиления, второй импульдля второго и т.д. Амплитуды выходных им плльсоз усилительнь х каскадов, соответствующие своим входным контрольным импульсам, запоминаются в блоке 7 пиковых детекторов.

Вь;ходные напряжения блока 7 подаются поочередно с помощью аналогового ком гутатора 8 напряженки на вход блока 9 сравнения а1.-шлитуд импульсов с эталонным напряжением. Если коэффициенты усиления касКо1Дов равны, своему нсминальному значенкгО. DasHOivcy основанию счисления, то вы- xoqifbi8 имгольсы каскадов усиления будут равны OAHoiviy и тому же эталонному напряженикз. В противном случае блок 9 сравнения амплитуд импульсов выдает ла вход соотвегс вуюшего интегратора блока 11 им- улье. равный разности выходного напряже кйя аналогового коммутатора 8 и. эталонного напряжения. Выходным напряжением б71ока 1 корректируется коэффициент пер€ дсчи того каскада усиления, в котором обкарзжекэ отклонение значения коэффициенfa усиления от номинального значения. Серкк гсонтрольных импульсов тложет формирозаться повторно в зависимости от величины периода повторения измеряемых импульсов.

Применение щирокополосных каскадов усилений вместе с блоком запоминания ко.IGB порядка и мантиссы входного сигнала обеспечивает щирокий динамический диапа- зек н безынердионность процесса : омерения апплитуд импульсов наносекундкой длительностИ; присущие системам разомкщ-того типа.

Устройство автоматической стабилизапин хоэффициектов передачи усигагтельных зсаскалов обеспечивает высокую то гость измерения амплитуд входньг;-- сигналов, присутую замкн тым системам автоматического регулирования.

D Предмет изобретения

Аналого-цифровой преобразователь с а&томати ческой регулировкой усиления содержащий п. -последова гельно соединенных усилительных каскадов, распределитель импульсов, выходы которого соединены с управляющими входами аналогового коммутатора, аналого-цифрового преобразователя и блока выбора и хранения порядка, входы iKOTOporo подключены к выходам блока по;роговых устройств,а выходы - к управ|ляющим входам аналогового коммутатора, выходы которого соединены со входом |аналого-цифрй лго преобразователя, о т ;личающийся, тем, что, с целью :Измерения амплитуд входных импульсов с повышенной точностью, в него введены ,блок формирования серии контрольных импульсов, блок интеграторов, блок сравнео

ния амплитуд импульсов и аналоговая схема ИЛИ , на один вход KOTopoii подан измеряемый сигнал, другой вход через блок формирования серии контрольных г дпульсов соединен с выходом распределителя импульсов, а выход - со входом первого усилительного каскада, при;чем входы регулировки коэффициентов передачи каждого усилительного каскада через блок интеграторов подключены к выходам блока сравнения амплитуд импулсов, а выходы каждого усилительного каскада соединены со входами блока пороговых устройств и со входами блока пиковых детекторов, управляемый вход которого подключен к выходу распределителя импульсов, а выходы - к входу аналогового коммутатора, выходы которого под-ключены ко входам блока сравнения амплитуд импульсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Импульсный логарифмический усилитель | 1975 |

|

SU577542A1 |

| Вычислительное устройство для первичной обработки информации | 1978 |

|

SU746604A1 |

| Устройство для считывания графической информации | 1983 |

|

SU1120378A1 |

| Вычислительное устройство для первичной обработки информации | 1978 |

|

SU746605A1 |

| Устройство для вычисления координат светового пятна | 1975 |

|

SU525037A1 |

| Вычислительное устройство для первичной обработки информации | 1978 |

|

SU746569A1 |

| Датчик положения светового пятна | 1975 |

|

SU578632A1 |

| Фоторегистратор | 1977 |

|

SU731309A1 |

| БОРТОВОЙ КОМПЛЕКС УПРАВЛЕНИЯ КОРРЕКТИРУЕМОЙ АВИАЦИОННОЙ БОМБЫ, ВЫПОЛНЕННОЙ ПО СХЕМЕ "УТКА", С ЛАЗЕРНОЙ ФЛЮГЕРНОЙ ГОЛОВКОЙ САМОНАВЕДЕНИЯ | 2003 |

|

RU2251656C1 |

| Импульсный усилитель с автоматической регулировкой усиления | 1973 |

|

SU482864A1 |

Авторы

Даты

1975-10-25—Публикация

1974-03-05—Подача