1

I Изобретение относится к электросвязи и может использоваться цля корреляционного приема, обработки и цекоцирования импульсных сигналов с относительной фазовой моцуляцией (ОФМ).

Известно устройство цля корреляционного приема импульсных сигналов с однократной относительной фазовой моцуляцией, содержащее параллельно соециненные по вхоцу синфазный и квадратурный каналы каждый из которых состоит из последовательно соединенных первого перемножител к второму входу которого подключен местный генератор, интегратора, к выходу которого подключен запоминающий блок, и второго перемножителя, и сумматор, к выходу которого подключен решающий блок. Однако такое устройство осуществляет автокорреляционный (некогерентный) прием сигнала, что снижает его помехозашишен- ность.

Цель изобретения - повышение помехозащищенности устройства. Для этого в каж.дом канале выход запоминающего блока подключен через последовательно соединенные первый знаковый перемножнтель и интегратор к второму входу второго перемножителя, выход которого подключен к последовательно соединенным второму и третьему знаковым перемножителям, ингенератору со сбросом, блокннг-генератору и счетному триггеру, при этом управляющий вхоц интегратора со сбросом подключен к выходу блокинг-генератора, управляющие входы первого и третьего знаковых перемножителей соединены с выходом рещающего устройства, а управляющий вход второго знакового перемножителя - с выходом счетного триггера.

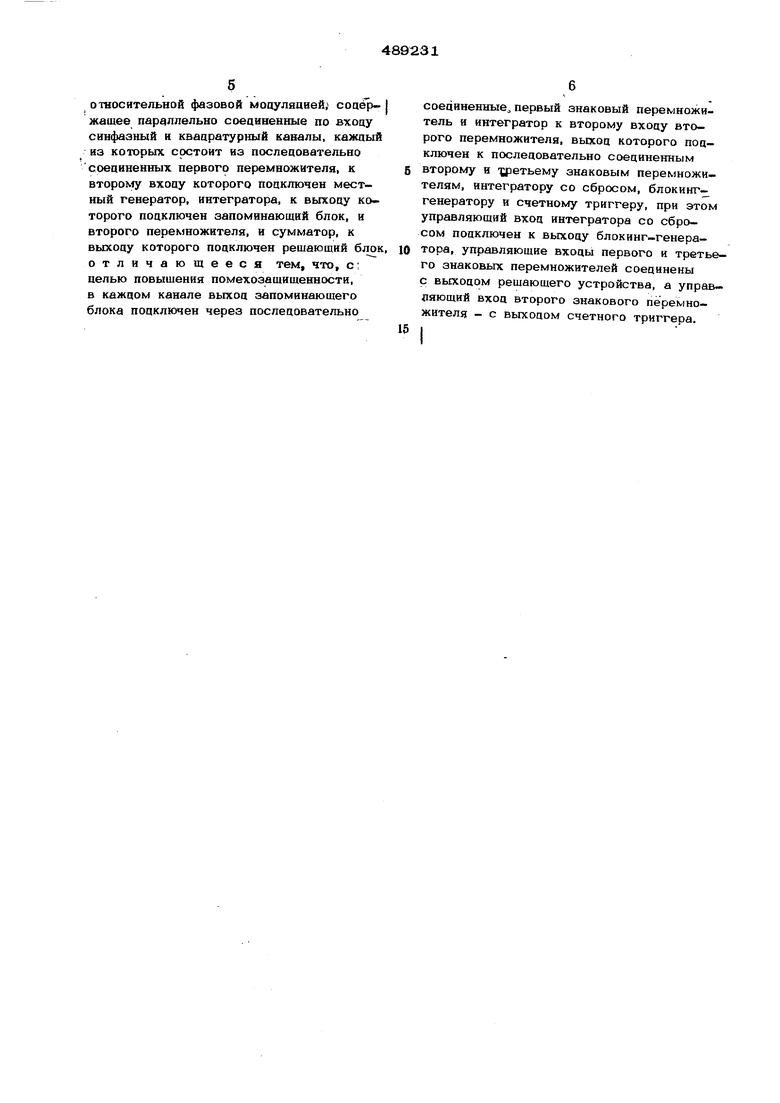

На чертеже дана блокинг-схема предлагаемого устройства.

Оно содержит параллельно соединенные по входу синфазный 1 н квадратурный 2 каналы, каждый из которых состоит из последовательно соединенных первого перемножителя 1-1 (2-1), интегратора 1-2 (2-2), к выходу которого подключены последовательно соединенные запоминающий блок 1-3(2-3), первый знаковый перемно- житель 1-4(2-4) и интегратор 1-5(2-5); второго перемножителя 1-6(2-6), второй вхоц которого соединен с выхоцом интегр тора 1-5(2-5). Выхоц второго перемножн теля 1-6(2-6) поцключен к послецовател но соединенным BTOpoiviy 1-7(2-7) и трет му 1-8(2-8) знаковым перемножителям, интегратору со сбросом 1-9 (2-9), блокин генератору 1-1(Х2-1О) и счетному тригге 1-11(2-11), вьпсоц которого соецинен с вторым вхоцом второго знакового перемно жителя 1-7(2-7), при: этом выход блокинг-генератора 1-10(2-10) соединен с .управляющим входом интегратора со сбросом 1-9(2-9). Входом устройства является объединенный вхоц первых перемножителей 1-1, 1-2, к вторым входам которых поцключен местный генератор 3, причем к первому перемножителю 2-1 квадратурного канала 2 местный генератор 3 подключен через фазовращатель 4. К выходам вторых знаковых пере .Н Жителей 1-7, 2-7 подключён сумматор 5, соединенный последовательно с решающим блоком 6, выход которого является выходом устройства и со динен с управляющими входами первых 1-4, 2-4 и третьих 1-8, 2-8знаковь1Х перемножителей. Объединенные управляющ -входы запоминающих блоков 1-3, 2-3 сое динены с входом синхроимпульсов, Устройство работает следующим образом. Прихоцящее на вхоц устройства сину соидальное колебание с ОФМ двоичными сигналами проходит далее одновременно в синфазный 1 и гсвадратурный 2 каналы, в каждом из которых входной сигнал в смеси с шумом поступает на вход первого перемножителя 1-1(2-1 ), на второй вход которого подается напряжение местного генератора 3, представляющее собой синусоидальное колебание с частотой, рав ной частоте приходящего сигнала, и произвольной фазой, причб м на первый пере- .множитель 2-1 квадратурного канала 2 аоцается сигнал местного генератора 3 через фазовращатель 4, осуи ествляю1ций сдвиг фаз на 9О . Выходное напряжение первого перемножителя 1-1(2-1), представляющее собой результат скалярного произведения напряжений сигналов пришед шего и местного генератора 3, фильтрует ся интегратором 1-2(2-2), с выхода которого отфильтрованное напряжение поступает одновременно на второй перемногжитель 1-6(2-6) и запоминающий блок 1-3(2-З), выполненный в виде временного селектора с запоминающей емкостью, на управляющий вход которого поступают I синхроимпульсы с тактовой частотой. Задержка напряжения, используемого -i в дальнейшем в качестве опорного, про- извсцится на один такт. Опорное напря- ение через первый знаковый умножиТель 1-4(2-4) поступает на интегратор 1-5(2-5), накапливающий напряжение за несколько тактов, в результате чего соотно- щение сигнал/шум увеличивается так, что при умножении опорного напряжения на основное -во втором перемножителе 1-6 (2-6), шумом; опорного напряжения можно пренебречь. С выхода второго перемножителя 1-6(2-6) напряжение поступает на второй знаковый перемножитель 1-7(2-7), где происходит обработка сигнала, в результате которой на входы сумматора 5 поступают выходные напряжения синфазного 1 и : квадратурного 2 каналов, имеющие одинаковые полярности, то необходимо для правильного сложения тих напряжений. Выходное напряжение сумматора 5 обрабатывается решающим блоком 6, откуда оно поступает на вход третьего накового перемножителя 1-8(2-8) и на ыход устройства. Третий знаковый перемноитель 1-8(2-8) производит вычисление наков напряжения в каждом из каналов 1(2) о отношению к суммарному. Знак напряжения с выхода третьего знакового перемножителя 1-8(2-8) положительный при одинаковых знаках сигналов с выходов решающего блока 6(суммарного) и второго знакового перемножителя 1-7(1-8) и отрицательный - при разных знаках. Отрицательное напряжение накапливается интегратором со сбросом 1-9(2-9), нарастая до уровня срабатывания блокинг-генератора 1-10(2-10), выходной импульс которого производит переброс счетного триггера 1-11(2-11) и сброс интегратора 1-9(2-9). Переброс счетного триггера 111 (2-11), управляющего работой второгб знакового перемножителя 1-7(2-7) приводит к инвертированию знака напряжения, поступающего на сумматор 5. Работа первого знакового перемножителя 1-4(2-4) управляется выходным напряжением решающего блока 6, при этом производится снятие фазовой манипуляции по решению, необходимое для правильного на.копления напряжения интегратором 1-5(2-5). В результате описанной работы устройства на выходе имеется сигнал, соответствующий напряжению на выходе корреляционного приемника. Предмет изобретения Устройство для корреляционного приема импульсных сигналов с однократной 1

относительной фазовой мооуляаией, соаер -1 жашее параллельно соеаиненные по вхоцу синфазный и квацратурный каналы, кажаый из которых состоит из последовательно соециненных первого перемножителя, к второму вхоцу которого поцключен местный генератор, интегратора, к выхоцу которого поцключен запоминающий блок, и второго перемножнтеля, и сумматор, к выходу которого подключен решающий блок, отличающееся тем, что, с ; пелью повышения помехозащищенности, в каждом канале выход запоминающего блока подключен через последовательно

соединенные первый знаковый переыножитель и интегратор к второму входу второго перемножителн, выход которого подключен к последовательно соединенным второму и изетьему знаковым перемножи- телям, интегратору со сбросом, блокинггенератору и счетному триггеру, при этом управляющий вход интегратора со сбросом подключен к выходу блокинг-генера-

тора, управляющие входы первого и третьего знаковых перемножителей соединены с выходом решающего устройства, а управляющий вход второго знакового перемножителя - с выходом счетного триггера.

I

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ КОРРЕЛЯЦИОННОГО ПРИЕМА ФАЗОМАНИПУЛИРОВАННЫХ СИГНАЛОВ | 1972 |

|

SU434612A1 |

| Устройство для корреляционногопРиЕМА фАзОМАНипулиРОВАННыХ СигНАлОВ | 1979 |

|

SU801301A2 |

| Устройство для когерентного приема фазоманипулированных сигналов | 1972 |

|

SU443455A1 |

| Устройство для восстановления несущей частоты | 1975 |

|

SU1046941A1 |

| ЛИНИЯ ПЕРЕДАЧИ ДИСКРЕТНОЙ ИНФОРМАЦИИ ПО ТРАКТАМ С ПЕРЕМЕННЫМИ ПАРАМЕТРАМИ | 1971 |

|

SU429546A1 |

| Синхронный приемник фазоманипулированного сигнала | 1974 |

|

SU486486A1 |

| УСТРОЙСТВО ТАКТОВОЙ СИНХРОНИЗАЦИИ | 2010 |

|

RU2423798C1 |

| Устройство для корреляционного приема фазоманипулированных сигналов с подстройкой частоты | 1984 |

|

SU1221762A1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ НАВИГАЦИОННЫХ СИГНАЛОВ ГЛОНАСС, GPS И ГАЛИЛЕО | 2010 |

|

RU2435307C1 |

| УСТРОЙСТВО КОМПЕНСАЦИИ СТРУКТУРНЫХ ПОМЕХ | 2010 |

|

RU2450445C2 |

Авторы

Даты

1975-10-25—Публикация

1973-01-31—Подача