Изобретение относится к радиотехнике и может быть использовано для тактовой синхронизации сигналов с квадратурно-амплитудной (КАМ) и фазовой манипуляцией (ФМн) в качестве составной части цифрового приемника КАМ-ФМн с подавленной несущей.

Известно устройство синхронизации тактовой и несущих частот (патент RU №2096917, МПК H04L 7/00), содержащее управляемый делитель частоты, делитель частоты, управляющий элемент, узел выделения ошибки сигнала синхронизации тактовой частоты в частотной области, три блока памяти, блок преобразования Фурье, сумматор, вычитатель, вентиль, формирователь управляющей величины, таймер, переключатель, оперативный запоминающий блок, задающий генератор, узел синхронизации несущей частоты, блок выделения ошибки синхронизации несущей частоты, генератор несущей частоты, синхронный детектор и блок управления.

Недостатком данного устройства является то, что оно не обеспечивает формирование нулевого сигнала ошибки на выходе при отсутствии ошибок синхронизации, то есть является источником внутренней манипуляционной помехи.

Известно также устройство тактовой синхронизации, входящее в состав цифроаналогового приемника двоичных символов, схема которого представлена на рис.1.32, стр.68 монографии «Цифровые системы фазовой синхронизации» под редакцией М.И.Жодзишского. - М.: Сов. радио, 1980. - 208 с.

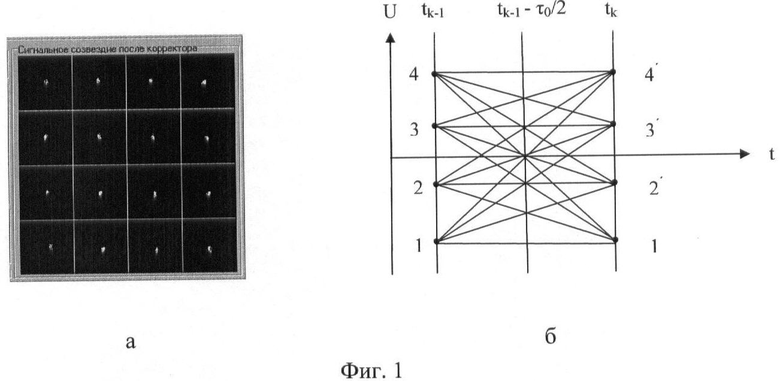

Известное устройство тазовой синхронизации содержит входной фильтр нижних частот, сигнал с выхода которого подается на два интегратора с временами интегрирования τс и τ0, на вторые входы которых поступают сигналы с выхода формирователя интервалов, выходы интеграторов с τс и τ0 соединены со входами первого и второго устройств определения знака (sign), выходы которых подключены к первому и второму входу умножителя через блок логики ±1; 0 и через регистр задержки на время τс-τ0/2 соответственно, а выход умножителя подключен через последовательно соединенные цифровой фильтр, цифроаналоговый преобразователь и управляемый генератор со входом формирователя интервалов. Поскольку известное устройство работает только с двухуровневыми сигналами (например, ФМ-2), причиной появления манипуляционной помехи могут быть повторяющиеся на двух или более тактовых интервалах символы «1» или «0». Наличие межсимвольной помехи, в совокупности с известными шумовой и межсимвольной помехами приводит к снижению качества восстановления тактовой частоты и, как следствие, к увеличению энергетических потерь приемника символов. В известном устройстве модуляционная помеха в точке точной синхронизации по тактовой частоте устраняется за счет алгоритма работы блока логики, который, в случае повторяющихся символов во входной последовательности, вырабатывает на выходе напряжение, равное нулю, которое, перемножаясь с сигналом ошибки с выхода регистра задержки, приводит сигнал ошибки к нулю, что соответствует состоянию синхронизма по тактовой частоте. В случае сигналов с КАМ и ФМн повторяющиеся символы являются не единственной причиной появления модуляционной помехи, что показано на фиг.1, где изображено, на примере сигнала КАМ-16, сигнальное созвездие сигнала и условные переходы на временной оси, соответствующее проекции сигнального созвездия на одну из координатных осей (в данном случае на ось Q). Моменты времени tk-1 и tk соответствуют моментам взятия отсчетов сигнала для принятия решения о варианте переданных k-1 и k символов. Момент времени tk-1-τ0/2 соответствует моменту взятия отсчета сигнала для формирования сигнала ошибки эквивалентного дискриминатора устройства тактовой синхронизации и показан для случая точного синхронизма по тактовой частоте. Очевидно, что сигнал ошибки должен быть равен нулю, что и выполняется для диагональных вариантов переходов 4-1', 1-4', 3-2', 2-3', но не выполняется для остальных вариантов перехода. Варианты 1-1', 2-2', 3-3', 4-4' также правильно исполняются в известном устройстве, поскольку они не несут информации о рассогласовании по тактовой частоте, то игнорирование остальных вариантов перехода приводит к уменьшению количества переходов в интервале наблюдения и, как следствие, к снижению качества восстановленной тактовой частоты. Кроме того, в известном устройстве не дифференцируются диагональные переходы и устройство реагирует лишь на повторяющиеся символы. Поэтому сигнал ошибки для переходов 4-3', 3-4', 2-4', 4-2', 3-1', 1-3', 2-1', 1-2' даже в случае точного синхронизма по тактовой частоте не равен нулю и достигает значительных уровней.

Недостатком данного устройства является то, что оно не осуществляет дифференциацию диагональных межсимвольных переходов, которые являются источником манипуляционной помехи и, тем самым, не обеспечивает формирование нулевого сигнала ошибки на выходе.

Наиболее близким по технической сущности к заявляемому изобретению является устройство тактовой синхронизации, представленное на рис.8. 2.1, стр.258 монографии «Защищенные радиосистемы цифровой передачи информации»/ П.Н.Сердюков, А.В.Бельчиков, А.Е.Дронов и др. - М.: ACT, 2006. - 403 с., содержащее синфазный и среднефазный интеграторы с управляемыми с помощью управляемого генератора импульсов моментами «опроса» и «сброса», при этом выход синфазного интегратора подключен через последовательно соединенные устройство определения знака и детектор Ik=(ak-1-ak)/2 к первому входу перемножителя, а выход среднефазного интегратора подключен через регистр задержки ко второму входу перемножителя, выход которого через цифровой фильтр соединен со входом управляемого генератора импульсов. Входной процесс r(t) дискретно обрабатывается синфазным и среднефазным интеграторами с «опросом» и «сбросом», что эквивалентно обработке сигнала согласованными фильтрами. В синфазном канале определяется полярность (знак) символа, а детектор обнаруживает переходы согласно алгоритму:

если ak-1=ak, тогда Ik=0;

если ak=-1, ak-1=+1, тогда Ik=+1;

если ak=+1, ak-1=-1, тогда Ik=-1.

В среднефазном тракте определяется величина ошибки синхронизации. Согласованную во времени работу трактов обеспечивает регистр задержки. Элементы синфазного и среднефазного трактов и перемножитель образуют эквивалентный дискриминатор (измерительный элемент) устройства тактовой синхронизации. Выходной сигнал дискриминатора усредняется с помощью цифрового фильтра и далее используется для управления частотой импульсного генератора и работой интеграторов с целью устранения ошибки синхронизации. Также как и в ранее рассмотренном устройстве тактовой синхронизации для случая двухуровневого сигнала в отсутствие ошибок синхронизации выходной сигнал эквивалентного дискриминатора равен нулю.

Недостатком данного устройства является то, что при приеме сигналов с КАМ и ФМн оно формирует на выходе эквивалентного дискриминатора сигнал ошибки, отличный от нуля при отсутствии ошибок синхронизации, то есть является источником внутренней манипуляционной помехи.

Цель изобретения - повышение помехоустойчивости приема сигналов с КАМ и ФМн за счет устранения манипуляционной помехи на выходе дискриминатора устройства тактовой синхронизации при отсутствии ошибок синхронизации

Цель достигается тем, что в известное устройство, содержащее управляемый генератор импульсов, первый регистр задержки, устройство определения знака, цифровой фильтр и перемножитель, согласно изобретению введены блок принятия решения, оперативное запоминающее устройство, первый блок вычитания, второй блок вычитания, второй регистр задержки, делитель на два, делитель частоты на два, инвертор, сумматор и аналогово-цифровой преобразователь, первый вход которого является первым входом устройства в целом, причем первый выход аналогово-цифрового преобразователя подключен к первому входу второго блока вычитания, а второй выход аналогово-цифрового преобразователя подключен к первому входу блока принятия решения, второй вход которого является вторым входом устройства в целом, выход блока принятия решения через последовательно соединенные первый регистр задержки, оперативное запоминающее устройство, второй блок вычитания, второй регистр задержки, перемножитель, делитель на два, цифровой фильтр, сумматор и управляемый генератор импульсов соединен со вторым входом аналогово-цифрового преобразователя и со вторым входом оперативного запоминающего устройства, второй выход которого соединен со вторым входом делителя на два, выход блока принятия решения также подключен к первому входу первого блока вычитания, ко второму входу которого подключен выход первого регистра задержки, а выход первого блока вычитания через устройство определения знака соединен со вторым входом перемножителя, при этом второй выход управляемого генератора импульсов, который является первым выходом устройства в целом, соединен с делителем частоты на два, выход которого, являющийся вторым выходом устройства в целом, соединен со вторым входом первого регистра задержки и через инвертор со вторым входом второго регистра задержки, при этом третьим входом устройства в целом является второй вход сумматора, а четвертым входом устройства в целом является третий вход оперативного запоминающего устройства.

Сопоставительный анализ технического решения с устройством, выбранным в качестве прототипа, показывает, что новизна технического решения заключается во введении в заявленное устройство новых схемных элементов: второго регистра задержки, первого сумматора, делителя на два, аналогово-цифрового преобразователя, первого блока вычитания, второго блока вычитания, делителя частоты на два, инвертора, второго сумматора с соответствующими связями.

Таким образом, заявляемое техническое решение соответствует критерию изобретения «новизна».

Анализ известных технических решений в исследуемой и смежных областях позволяет сделать вывод о том, что введенные функциональные узлы известны. Однако введение их в устройство тактовой синхронизации с указанными связями придает этому устройству новые свойства. Введенные функциональные узлы взаимодействуют так, что позволяют устранить манипуляционную помеху на выходе дискриминатора устройства тактовой синхронизации в случае приема сигналов с КАМ и ФМн и отсутствии ошибок синхронизации.

Таким образом, техническое решение соответствует критерию “изобретательский уровень", т.к. оно для специалиста явным образом не следует из уровня техники.

Изобретение может быть использовано для тактовой синхронизации цифровых приемников сигналов с квадратурно-амплитудной и фазовой манипуляцией с подавленной несущей.

Таким образом, изобретение соответствует критерию “промышленная применимость".

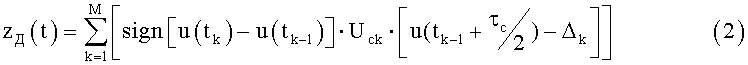

Структура предлагаемого устройства тактовой синхронизации получена из выражения для функции правдоподобия по параметру амплитуды ak оптимального дискриминатора при непрерывном времени наблюдения («Цифровые системы фазовой синхронизации» под редакцией М.И.Жодзишского, формула 1.30, стр.30). Для многоуровневого сигнала, характерного для КАМ, ФМ и АФМ сигналов, исходное выражение для функции правдоподобия по параметру амплитуды ak примет вид:

где N0 - односторонняя спектральная плотность шума,

- число выборок в интервале Δτ, разделяющем любые две последовательные метки символов;

- число выборок в интервале Δτ, разделяющем любые две последовательные метки символов;

индекс j обозначает j-и символ из множества n возможных символов;

L - число выборок на символ;

τc - длительность символа;

|φc0|≤π - фаза сигнала uвх0(t) по отношению к тактовым моментам времени kτc, выраженная в радианах;

P(j) - вероятность появления j-го символа;

с - константа.

Из выражения (1), с учетом эквивалентности операции интегрирования, входной смеси сигнал + шум и взятия мгновенного отсчета в момент, соответствующий середине символа, а также замены функции th(х) знаковой функцией sign(x), можно получить выражение для дискриминатора системы тактовой синхронизации, работающей с КАМ и ФМн сигналами.

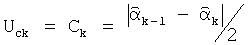

Здесь,  - амплитуда симметричного двухполярного сигнала и нормирующий коэффициент соответственно, а

- амплитуда симметричного двухполярного сигнала и нормирующий коэффициент соответственно, а  , где

, где  - решение относительно k-го параметра амплитуды.

- решение относительно k-го параметра амплитуды.

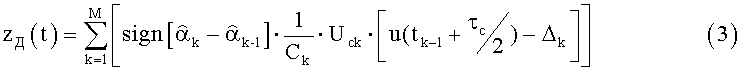

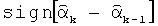

Учитывая, что первый сомножитель под знаком суммы выражения 2 определяет знак ошибки эквивалентного дискриминатора, его можно вычислять как знак разности текущего и задержанного решений относительно параметра амплитуды ak. Таким образом, выражение для дискриминатора системы тактовой синхронизации примет вид:

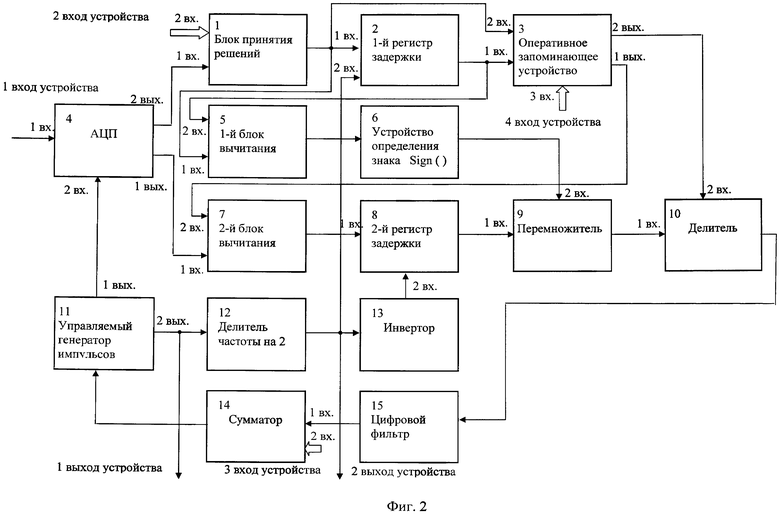

На фиг.2 представлена функционально-структурная блок схема устройства тактовой синхронизации, построенная на основе выражения (2).

На фиг.1, на примере сигнала КАМ-16, представлено сигнальное созвездие сигнала и условные переходы на временной оси, соответствующее проекции сигнального созвездия на одну из координатных осей (в данном случае на ось Q);

на фиг.2 - блок-схема устройства тактовой синхронизации;

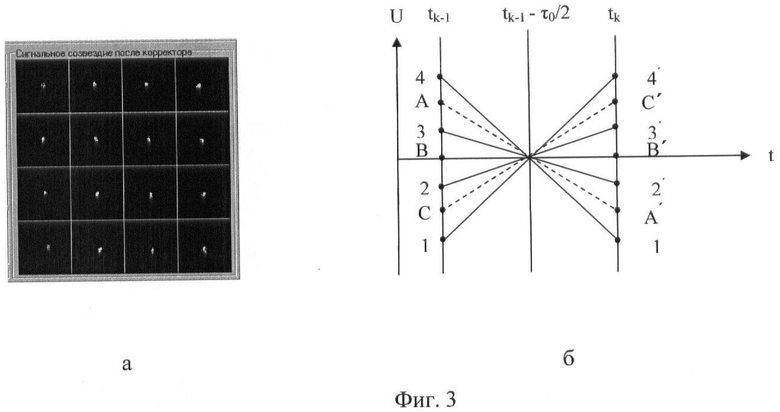

на фиг.3 - сигнальное созвездие сигнала КАМ-16 и условное изображение переходов на временной оси после операции приведения переходов многоуровневого входного сигнала к нулевому уровню при отсутствии ошибок синхронизации;

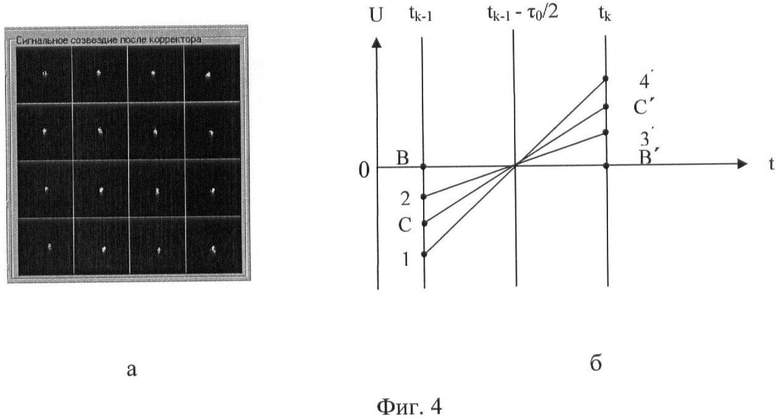

на фиг.4 - сигнальное созвездие сигнала КАМ-16 и условное изображение переходов на временной оси после операции приведения знака крутизны.

Устройство тактовой синхронизации (фиг.2) содержит:

- блок принятия решения 1,

- первый регистр задержки 2,

- оперативное запоминающее устройство 3,

- аналогово-цифровой преобразователь 4,

- первый блок вычитания 5,

- устройство определения знака 6,

- второй блок вычитания 7,

- второй регистр задержки 8,

- перемножитель 9,

- делитель на два 10,

- управляемый генератор импульсов 11,

- делитель частоты на два 12,

- инвертор 13,

- сумматор 14,

- цифровой фильтр 15.

Причем первый вход аналогово-цифрового преобразователя 4 является первым входом устройства в целом, а первый выход аналогово-цифрового преобразователя 4 подключен к первому входу второго блока вычитания 7, а второй выход аналогово-цифрового преобразователя 4 подключен к первому входу блока принятия решения 1, второй вход которого является вторым входом устройства в целом, выход блока принятия решения 1 через последовательно соединенные первый регистр задержки 2, оперативное запоминающее устройство 3, второй блок вычитания 7, второй регистр задержки 8, перемножитель 9, делитель на два 10, цифровой фильтр 15, сумматор 14 и управляемый генератор импульсов 11 соединен со вторым входом аналогово-цифрового преобразователя 4 и со вторым входом оперативного запоминающего устройства 3, второй выход которого соединен со вторым входом делителя на два 10, выход блока принятия решения 1 также подключен к первому входу первого блока вычитания 5, ко второму входу которого подключен выход первого регистра задержки 2, а выход первого блока вычитания 5 через устройство определения знака 6 соединен со вторым входом перемножителя 9, при этом второй выход управляемого генератора импульсов 11, который является первым выходом устройства в целом, соединен с делителем частоты на два 12, выход которого, являющийся вторым выходом устройства в целом, соединен со вторым входом первого регистра задержки 2 и через инвертор 13 со вторым входом второго регистра задержки 8, при этом третьим входом устройства в целом является второй вход сумматора 14, а четвертым входом устройства в целом является третий вход оперативного запоминающего устройства 3.

Предлагаемое устройство работает следующим образом.

Входной многоуровневый сигнал (фиг.2) поступает на первый вход аналого-цифрового преобразователя 4. На второй вход аналого-цифрового преобразователя 4 подается сигнал с удвоенной тактовой частотой. В дискретные моменты времени, определяемые, например, фронтами сигнала, берутся поочередно выборки входного сигнала. Четные выборки в моменты времени tk соответствуют серединам информационных символов, в то время как нечетные выборки соответствуют моментам времени, в которые осуществляется переход от одного информационного символа к другому, то есть  . Таким образом, четные выборки эквивалентны сигналу с выхода интегратора синфазного канала, а нечетные - сигналу величины ошибки с выхода интегратора среднефазного канала прототипа. Четные выборки сигнала со второго выхода аналого-цифрового преобразователя 4 подаются на первый вход блока 1 принятия решений. Блок 1 принятия решений в зависимости от координаты текущей точки сигнального созвездия на ось Y (на фиг.1 ось U) присваивает входному отсчету значение, соответствующее точке «1», если -A>U≥-B; значение, соответствующее точке «2», если 0>U≥-A; значение, соответствующее точке «3», если A>U≥0; значение, соответствующее точке «4», если B>U≥A.

. Таким образом, четные выборки эквивалентны сигналу с выхода интегратора синфазного канала, а нечетные - сигналу величины ошибки с выхода интегратора среднефазного канала прототипа. Четные выборки сигнала со второго выхода аналого-цифрового преобразователя 4 подаются на первый вход блока 1 принятия решений. Блок 1 принятия решений в зависимости от координаты текущей точки сигнального созвездия на ось Y (на фиг.1 ось U) присваивает входному отсчету значение, соответствующее точке «1», если -A>U≥-B; значение, соответствующее точке «2», если 0>U≥-A; значение, соответствующее точке «3», если A>U≥0; значение, соответствующее точке «4», если B>U≥A.

Значения порогов загружаются в блок 1 принятия решения по второму входу, который является вторым входом устройства в целом, и хранятся там до момента смены вида модуляции сигнала, поступающего на первый вход устройства, то есть до момента перенастройки на новый сигнал с отличным от ранее установленного вида модуляции. Процедура расчета значений порогов для других видов модуляции (КАМ-64, КАМ-128, КАМ-256) представлена на фиг.1б); величина k-го порога рассчитывается как координата k-й точки сигнального созвездия плюс половина расстояния между соседними точками по соответствующей координате. Решения  с выхода блока 1 принятия решения поступают на второй вход первого блока вычитания 5, на первый вход которого подаются решения

с выхода блока 1 принятия решения поступают на второй вход первого блока вычитания 5, на первый вход которого подаются решения  , задержанные на время, равное длительности символа с выхода первого регистра задержки 2. Результат вычитания подается с выхода первого блока вычитания 5 на вход устройства 6 определения знака.

, задержанные на время, равное длительности символа с выхода первого регистра задержки 2. Результат вычитания подается с выхода первого блока вычитания 5 на вход устройства 6 определения знака.

Таким образом, первый блок вычитания 5 совместно с устройством 6 определения знака вычисляет значение первого сомножителя выражения 3, а именно  . Решения с выхода блока принятия решения 1 и задержанные на время, равное длительности символа в первом регистре задержки 2 решения, подаются соответственно на второй и первый адресные входы оперативного запоминающего устройства 3, где хранятся два массива данных, загруженных по третьему входу перед началом работы устройства тактовой синхронизации в соответствии с видом модуляции сигнала, поступающего на вход устройства тактовой синхронизации. Первый массив данных содержит все возможные для выбранного вида модуляции значения

. Решения с выхода блока принятия решения 1 и задержанные на время, равное длительности символа в первом регистре задержки 2 решения, подаются соответственно на второй и первый адресные входы оперативного запоминающего устройства 3, где хранятся два массива данных, загруженных по третьему входу перед началом работы устройства тактовой синхронизации в соответствии с видом модуляции сигнала, поступающего на вход устройства тактовой синхронизации. Первый массив данных содержит все возможные для выбранного вида модуляции значения  , а второй массив данных содержит все возможные для выбранного вида модуляции значения

, а второй массив данных содержит все возможные для выбранного вида модуляции значения  .

.

Нечетные выборки сигнала со второго выхода аналого-цифрового преобразователя 4 подаются на первый вход второго блока вычитания 7, на второй вход которого поступают значения Δk с первого выхода оперативного запоминающего устройства 3. С выхода второго блока вычитания 7 результат приведения отсчетов сигнала к нулевому уровню при отсутствии ошибок синхронизации в момент перехода подается через второй регистр задержки 8 на первый вход перемножителя 9. Так же как и в известном устройстве, второй регистр задержки 8 обеспечивает согласованную во времени работу трактов сигналов, поступающих на первый и второй входы перемножителя 9. Сигнал на выходе второго регистра задержки 8 описывается последним множителем выражения 3, а именно:

Условное изображение переходов на временной оси после операции приведения показано на фиг.3б). Здесь переход АА' является приведенным переходом для 42' и 31', переход СС' является приведенным переходом для 13' и 24, ВВ' является приведенным переходом для повторяющихся символов 11', 22', 33' и 44', самостоятельные переходы 32' и 23' кроме того служат приведенными переходами для 43', 21' и 12, 34 соответственно. Из фиг.3б) видно, что после операции приведения уменьшилось количество вариантов возможных переходов и в отсутствие ошибок синхронизации величина напряжения на выходе второго блока вычитания 7 для любого варианта перехода на его входе тождественно равна нулю. Сигнал, описываемый выражением  с выхода второго регистра задержки 8 подается на первый вход перемножителя 9, на второй вход которого поступает сигнал, описываемый выражением

с выхода второго регистра задержки 8 подается на первый вход перемножителя 9, на второй вход которого поступает сигнал, описываемый выражением  с выхода устройства определения знака 6. Перемножитель 9 осуществляет в соответствии с выражением 3 операцию приведения знака крутизны переходов. Условное изображение переходов на временной оси после операции приведения показано на фиг.4б). С выхода перемножителя 9 сигнал временной ошибки поступает на первый вход делителя 10, в котором осуществляется его деление на соответствующее число Ck, поступающее на второй вход делителя 10 со второго выхода оперативного запоминающего устройства 3.

с выхода устройства определения знака 6. Перемножитель 9 осуществляет в соответствии с выражением 3 операцию приведения знака крутизны переходов. Условное изображение переходов на временной оси после операции приведения показано на фиг.4б). С выхода перемножителя 9 сигнал временной ошибки поступает на первый вход делителя 10, в котором осуществляется его деление на соответствующее число Ck, поступающее на второй вход делителя 10 со второго выхода оперативного запоминающего устройства 3.

В делителе 10 осуществляется операция нормирования всех возможных вариантов переходов по параметру крутизны. Нормирование позволяет устранить манипуляционную помеху не только при точной синхронизации, но и при произвольных отстройках в пределах полосы удержания, а также снижает влияние манипуляционной помехи при низких соотношениях сигнал/шум на входе 1 устройства тактовой синхронизации. После фильтрации в цифровом фильтре 15 в соответствии с выражением 3 сигнал ошибки суммируется во втором сумматоре 14 с цифровым кодом, соответствующим значению тактовой частоты входного сигнала устройства, и подается на управляющий вход управляемого генератора импульсов 11. При этом происходит корректировка временной (фазовой) ошибки восстановленной тактовой частоты относительно входного сигнала. Удвоенная тактовая частота, необходимая для работы различных функциональных узлов демодулятора сигналов с КАМ и ФМн, поступает на первый выход устройства тактовой синхронизации и после деления в делителе частоты на два 12 на второй выход устройства тактовой синхронизации. Кроме того, сигнал с тактовой частотой с выхода делителя частоты на два 12 подается на вторые тактовые входы первого 2 и второго 8 регистров задержки непосредственно и через инвертор 13 соответственно, обеспечивая согласованную во времени обработку сигнала.

Испытания предложенного устройства тактовой синхронизации по реальному сигналу показали его полезность, так для сигналов КАМ-16 и КАМ-64 при отношении сигнал/шум на входе демодулятора 25 и 28 дБ наблюдалось снижение вероятности ошибки в 1,7 и 2,6 раза соответственно по сравнению с устройством тактовой синхронизации, построенной по классической схеме прототипа. При отношении сигнал/шум на входе демодулятора 23 и 26,5 дБ улучшение составило 1,3 и 2 раза для сигналов КАМ-16 и КАМ-64 соответственно. При высоких отношениях сигнал/шум 26 и 29 дБ, смоделированных на лабораторной установке, выигрыш от использования предложенного устройства тактовой синхронизации увеличивается и составляет порядка 3,5-4,5 раз по вероятности ошибки. Следует также отметить, что попытка снизить влияние манипуляционной помехи за счет заужения полосы цифрового фильтра оказывается менее эффективной и, кроме того, приводит к ухудшению динамических свойств устройства тактовой синхронизации.

Аналого-цифровой преобразователь реализован на основе микросхемы AD 9230, управляемый генератор импульсов выполнен в виде цифрового синтезатора частоты на микросхемах AD 9858, ADV 7128KR80 и AD820AR, остальные элементы устройства тактовой синхронизации реализованы на основе микросхемы ПЛИС XC2VP50.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДЕМОДУЛЯТОР ФАЗОМАНИПУЛИРОВАННЫХ СИГНАЛОВ | 2008 |

|

RU2393641C1 |

| ВРЕМЕННОЙ ДИСКРИМИНАТОР УСТРОЙСТВА ТАКТОВОЙ СИНХРОНИЗАЦИИ | 2006 |

|

RU2314646C1 |

| Устройство автоподстройки несущей частоты | 1984 |

|

SU1298946A1 |

| Адаптивный цифровой корректор | 1982 |

|

SU1083379A1 |

| Адаптивный цифровой корректор | 1979 |

|

SU794734A1 |

| СПОСОБ КОРРЕЛЯЦИОННОГО ПРИЁМА СИГНАЛОВ С ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МОДУЛЯЦИЕЙ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2002 |

|

RU2237978C2 |

| Линейное устройство коррекции межсимвольной интерференции | 1984 |

|

SU1210225A1 |

| СЛЕДЯЩИЙ ПРИЕМНИК ШИРОКОПОЛОСНОГО СИГНАЛА | 1999 |

|

RU2157052C1 |

| АКУСТООПТИЧЕСКИЙ ПРИЕМНИК | 1991 |

|

RU2007046C1 |

| Когерентный приемник частотно-манипулированных радиосигналов с непрерывной фазой | 1990 |

|

SU1716615A1 |

Изобретение относится к радиотехнике и может быть использовано для тактовой синхронизации сигналов с квадратурно-амплитудной (КАМ) и фазовой манипуляцией (ФМн) в цифровых приемниках. Достигаемый технический результат - повышение помехоустойчивости приема сигналов с КАМ и ФМн. Устройство содержит управляемый генератор импульсов, два регистра задержки, устройство определения знака, цифровой фильтр, перемножитель, блок принятия решения, оперативное запоминающее устройство, аналогово-цифровой преобразователь, два блока вычитания, делитель, делитель частоты на два, инвертор и сумматор. 4 ил.

Устройство тактовой синхронизации, содержащее управляемый генератор импульсов, первый регистр задержки, устройство определения знака, цифровой фильтр и перемножитель, отличающееся тем, что введены блок принятия решения, оперативное запоминающее устройство, первый блок вычитания, второй блок вычитания, второй регистр задержки, делитель, делитель частоты на два, инвертор, сумматор и аналогово-цифровой преобразователь, первый вход которого является первым входом устройства в целом, причем первый выход аналогово-цифрового преобразователя подключен к первому входу второго блока вычитания, а второй выход аналогово-цифрового преобразователя подключен к первому входу блока принятия решения, второй вход которого является вторым входом устройства в целом, выход блока принятия решения через последовательно соединенные первый регистр задержки, оперативное запоминающее устройство, второй блок вычитания, второй регистр задержки, перемножитель, делитель, цифровой фильтр, сумматор и управляемый генератор импульсов соединен со вторым входом аналогово-цифрового преобразователя, и со вторым входом оперативного запоминающего устройства, второй выход которого соединен со вторым входом делителя, выход блока принятия решения также подключен к первому входу первого блока вычитания, ко второму входу которого подключен выход первого регистра задержки, а выход первого блока вычитания, через устройство определения знака соединен со вторым входом перемножителя, при этом второй выход управляемого генератора импульсов, который является первым выходом устройства в целом, соединен с делителем частоты на два, выход которого, являющийся вторым выходом устройства в целом, соединен со вторым входом первого регистра задержки, и через инвертор - со вторым входом второго регистра задержки, при этом третьим входом устройства в целом является второй вход сумматора, а четвертым входом устройства в целом является третий вход оперативного запоминающего устройства.

| УСТРОЙСТВО СИНХРОНИЗАЦИИ ТАКТОВОЙ И НЕСУЩЕЙ ЧАСТОТ | 1991 |

|

RU2096917C1 |

| УСТРОЙСТВО ЧАСТОТНО-ВРЕМЕННОЙ СИНХРОНИЗАЦИИ | 2006 |

|

RU2341892C2 |

| СПОСОБ И УСТРОЙСТВО СИНХРОНИЗАЦИИ М-ПОСЛЕДОВАТЕЛЬНОСТИ | 1997 |

|

RU2127954C1 |

| US 6278725 B1, 21.08.2001 | |||

| US 5661440 A, 26.08.1997. | |||

Авторы

Даты

2011-07-10—Публикация

2010-05-27—Подача