Изобретение относится к области радиотехники и может использоваться в приемниках шумоподобных сигналов с минимальной частотной манипуляцией.

Известно устройство компенсации структурных помех для приемников широкополосных сигналов. В устройстве на входе приемника имеется n идентичных узлов, в каждом из которых осуществляется компенсация одной из структурных помех в том случае, если ее уровень превышает допустимое значение [патент RU № 2143175, Н04В 1/10]. Однако известное устройство не обеспечивает эффективное подавление помехи вследствие проникновения полезного сигнала в канал формирования копии помехи.

Известно устройство подавления структурных помех, в котором структурная помеха сворачивается в узкополосную помеху, которая режектируется режекторным фильтром [патент RU № 2143781, Н04В 1/10]. Недостатком известного устройства является подавление части спектра полезного сигнала в полосе режекторного фильтра.

Наиболее близким техническим решением к предлагаемому является устройство подавления структурных помех в приемнике базовой станции системы связи с кодовым разделением каналов, содержащее приемник, вход которого соединен с выходом коммутатора, первый вход которого соединен с входом устройства непосредственно, а второй - через последовательно соединенные элемент задержки и блок режекции, приемник мешающего сигнала, модулятор и кодер, причем первый выход приемника мешающего сигнала соединен с третьим входом коммутатора, второй - с входом модулятора, третий - с входом кодера, выход кодера соединен с вторым входом модулятора, выход которого соединен с входом блока режекции [патент RU № 2122283, Н04В 1/10].

Недостатком известного устройства является низкая эффективность подавления структурной помехи вследствие невысокой точности формирования копии помехи. Кроме того, в устройстве необходима задержка входного сигнала на длительность информационного бита, что значительно усложняет реализацию устройства.

Предлагаемое изобретение призвано решить задачу повышения эффективности подавления структурной помехи при приеме шумоподобных сигналов с минимальной частотной манипуляцией.

Поставленная задача решается тем, что в устройстве компенсации структурных помех, содержащем приемник мешающего сигнала, модулятор, блок режекции, один вход которого соединен с выходом модулятора, коммутатор, первый и второй входы которого соединены соответственно с входом устройства и выходом блока режекции, а третий вход которого подключен к командному выходу приемника мешающего сигнала, согласно изобретению вход устройства соединен с вторым входом блока режекции и входом приемника мешающего сигнала, содержащего блок фазовой синхронизации, включающий фазовый дискриминатор, содержащий первый и второй перемножители, сигнальные входы которых соединены с входом устройства, третий и четвертый, пятый и шестой перемножители, выходы которых объединены соответственно через первый вычитатель и сумматор, первый и второй интеграторы, входы которых соответственно подключены к выходам первого вычитателя и сумматора, первый решающий блок, вход которого подключен к выходу первого интегратора, а выход которого соединен с опорным входом седьмого перемножителя, сигнальный вход которого подключен к выходу второго интегратора, а к выходу которого подключены последовательно соединенные первый петлевой фильтр и подстраиваемый генератор несущей частоты, квадратурные выходы которого соединены соответственно с опорными входами первого и второго перемножителей, при этом сигнальные входы третьего и пятого, четвертого и шестого перемножителей попарно объединены и подключены к выходам соответственно первого и второго перемножителей, блок кодовой синхронизации, включающий последовательно соединенные временной дискриминатор, содержащий последовательно соединенные восьмой перемножитель, сигнальный вход которого подключен к выходу сумматора, третий интегратор, синхронизирующий вход которого соединен с синхронизирующими входами первого и второго интеграторов и подключен к выходу дешифратора, подключенного к дополнительным выходам генератора кода, и девятый перемножитель, опорный вход которого подключен к выходу первого решающего блока, второй петлевой фильтр и управляемый фазовращатель, другой вход которого соединен с выходом делителя частоты, входом соединенного с первым квадратурным выходом подстраиваемого генератора несущей частоты, а выход которого соединен со входом генератора кода, инверсный выход которого соединен с опорным входом восьмого перемножителя, а прямой выход которого соединен со входом синтезатора опорных квадратурных сигналов, выходы которого соединены соответственно с попарно объединенными опорными входами третьего и шестого, четвертого и пятого перемножителей, блок оценки амплитуды, содержащий аттенюатор, вход которого подключен к выходу первого интегратора, а выход которого соединен с сигнальным входом десятого перемножителя, опорный вход которого подключен к выходу первого решающего блока, последовательно соединенные фильтр нижних частот, вход которого подключен к выходу десятого перемножителя, и пороговый элемент, выход которого является командным выходом приемника мешающего сигнала, последовательно соединенные четвертый интегратор, вход которого подключен к выходу первого вычитателя, а первый и второй синхронизирующие входы которого соединены соответственно с выходом дешифратора и выходом делителя частоты, и второй решающий блок, к выходу которого подключен один вход одиннадцатого перемножителя, другой вход которого соединен с выходом фильтра нижних частот, а выход которого является выходом блока оценки амплитуды, модулятор, содержащий двенадцатый и тринадцатый перемножители, сигнальные входы которых подключены соответственно к квадратурным выходам подстраиваемого генератора несущей частоты, опорные входы которых соединены соответственно с выходами синтезатора опорных квадратурных сигналов, а выходы которых объединены через второй вычитатель, выход которого соединен с сигнальным входом четырнадцатого перемножителя, опорный вход которого подключен к выходу блока оценки амплитуды, а выход которого является выходом модулятора, при этом первый и второй решающие блоки формируют оценку текущего информационного символа структурной помехи с задержкой соответственно на длительность информационного символа и длительность элемента кода.

Введение перечисленных узлов с описанными связями позволяет по сравнению с прототипом повысить помехоустойчивость приемника шумоподобного сигнала с минимальной частотной манипуляцией путем компенсации структурной помехи во входном сигнале.

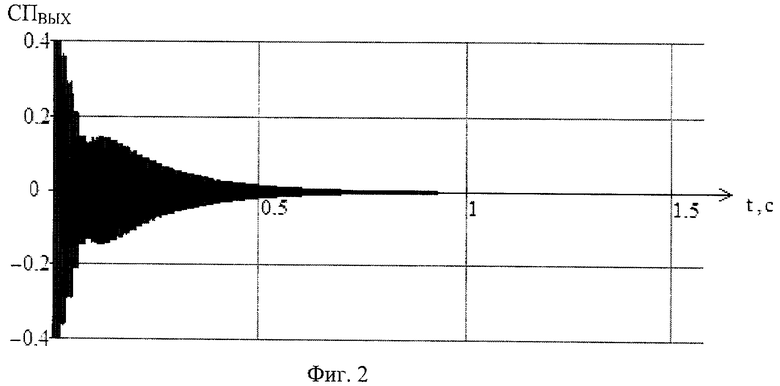

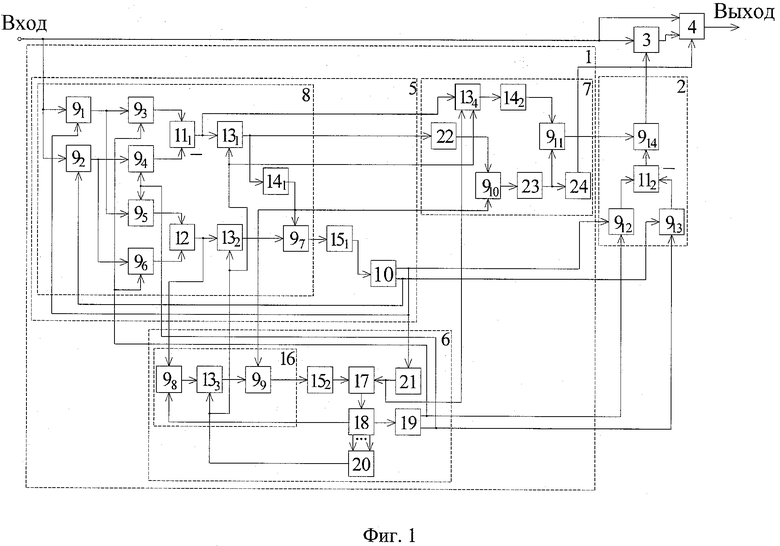

На фиг.1 приведена функциональная схема заявляемого устройства, на фиг.2 представлены результаты имитационного моделирования устройства компенсации структурных помех.

Устройство компенсации структурных помех содержит приемник 1 мешающего сигнала, модулятор 2, блок 3 режекции и коммутатор 4.

Приемник 1 мешающего сигнала включает блок 5 фазовой синхронизации, блок 6 кодовой синхронизации, блок 7 оценки амплитуды. Блок 5 фазовой синхронизации содержит фазовый дискриминатор 8, включающий первый 91 и второй 92 перемножители, сигнальные входы которых соединены с первым входом блока 3 режекции и первым входом коммутатора 4 и являются входом устройства, а опорные входы перемножителей 91 и 92 подключены соответственно к квадратурным выходам подстраиваемого генератора 10 несущей частоты. Фазовый дискриминатор 8 содержит также третий 93, четвертый 94, пятый 95, шестой 96 и седьмой 97 перемножители, первый вычитатель 111, сумматор 12, первый 131 и второй 132 интеграторы, первый решающий блок 141. При этом сигнальные входы третьего 93 и пятого 95, четвертого 94 и шестого 96 перемножителей попарно объединены и подключены соответственно к выходам первого 91 и второго 92 перемножителей. Выходы третьего 93 и четвертого 94, пятого 95 и шестого 96 перемножителей объединены соответственно через вычитатель 111 и сумматор 12, к выходам которых подключены соответственно первый 131 и второй 132 интеграторы. Сигнальный вход перемножителя 97 подключен к выходу интегратора 132, опорный вход перемножителя 97 подключен к выходу первого решающего блока 141, входом соединенного с выходом первого интегратора 131. Выход перемножителя 97, являющийся выходом фазового дискриминатора 8, соединен со входом первого петлевого фильтра 151, к выходу которого подключен вход подстраиваемого генератора 10 несущей частоты.

Блок 6 кодовой синхронизации содержит последовательно соединенные временной дискриминатор 16 и второй петлевой фильтр 152, а также управляемый фазовращатель 17, генератор 18 кода, синтезатор 19 опорных квадратурных сигналов, дешифратор 20, делитель 21 частоты. Временной дискриминатор 16 включает последовательно соединенные перемножитель 98, интегратор 133 и перемножитель 99, причем сигнальный вход перемножителя 98 соединен с выходом сумматора 12 блока 5 фазовой синхронизации. Синхронизирующий вход интегратора 133 соединен с синхронизирующими входами интеграторов 131 и 132 и подключен к выходу дешифратора 20, опорный вход перемножителя 99 подключен к выходу решающего блока 141, а выход перемножителя 99 является выходом временного дискриминатора 16. Вход генератора 18 кода подключен к выходу управляемого фазовращателя 17, сигнальный вход которого соединен с выходом делителя 21 частоты, а управляющий вход подключен к выходу петлевого фильтра 152. Вход синтезатора 19 опорных квадратурных сигналов подключен к прямому выходу генератора 18 кода, инверсный выход которого соединен с опорным входом перемножителя 98, а к дополнительным выходам генератора 18 кода подключен дешифратор 20. Выходы синтезатора 19 опорных квадратурных сигналов соединены соответственно с объединенными попарно опорными входами перемножителей 93 и 96, 94 и 95. Вход делителя 21 частоты соединен с первым квадратурным выходом подстраиваемого генератора 10 несущей частоты.

Блок 7 оценки амплитуды содержит аттенюатор 22, перемножитель 910, фильтр 23 нижних частот, пороговый элемент 24, интегратор 134, решающий блок 142 и перемножитель 911. Вход аттенюатора 22 подключен к выходу интегратора 131 блока 5 фазовой синхронизации, а выход аттенюатора 22 соединен с сигнальным входом перемножителя 910, опорный вход которого подключен к выходу первого решающего блока 141, а выход которого соединен со входом фильтра 23 нижних частот. Вход порогового элемента 24 подключен к выходу фильтра 23 нижних частот, а выход порогового элемента 24, являющийся командным выходом приемника 1 мешающего сигнала, соединен с третьим входом коммутатора 4. Вход интегратора 134 подключен к выходу вычитателя 111 блока 5 фазовой синхронизации, а первый и второй синхронизирующие входы интегратора 134 соединены соответственно с выходом дешифратора 20 и выходом делителя 21 частоты.

Выход интегратора 134 соединен со входом второго решающего блока 142, к выходу которого подключен опорный вход перемножителя 911, выход которого является выходом блока 7 оценки амплитуды.

Модулятор 2 содержит перемножители 912 и 913, сигнальные входы которых подключены соответственно к квадратурным выходам подстраиваемого генератора 10 несущей частоты, а опорные входы соединены соответственно с выходами синтезатора 19 опорных квадратурных сигналов, а также второй вычитатель 112 и перемножитель 914. Выходы перемножителей 912 и 913 объединены через вычитатель 112, к выходу которого подключен первый вход перемножителя 914, второй вход которого соединен с выходом перемножителя 911 блока 7 оценки амплитуды, а выход перемножителя 914 соединен со вторым входом блока 3 режекции, к выходу которого подключен второй вход коммутатора 4, выход которого является выходом устройства.

Устройство компенсации структурных помех работает следующим образом. Входной сигнал, представляющий аддитивную смесь полезного сигнала, структурной помехи и шума, поступает на сигнальный вход блока 3 режекции и входы перемножителей 91 и 92 блока 5 фазовой синхронизации. Полезный сигнал представляет шумоподобный сигнал с минимальной частотной манипуляцией. Структурная помеха (СП) также представляет ШПС с минимальной частотной манипуляцией, отличающийся от полезного сигнала структурой модулирующей кодовой последовательности, а также амплитудой, временем запаздывания и частотным сдвигом.

В перемножителях 91 и 92 входной сигнал перемножается с опорными квадратурными сигналами соответственно cos(ω0t) и sin(ω0t) частоты ω0, равной средней частоте структурной помехи. Указанные сигналы вырабатываются подстраиваемым генератором 10 несущей частоты блока 5 фазовой синхронизации. Квадратурные видеочастотные составляющие структурной помехи с выходов перемножителей 91 и 92 поступают на попарно объединенные сигнальные входы перемножителей 93 и 95, 94 и 96 соответственно, где перемножаются с опорными видеочастотными сигналами, формируемыми синтезатором 19 опорных квадратурных сигналов блока 6 кодовой синхронизации. При идеальной кодовой синхронизации опорные квадратурные сигналы являются точными копиями квадратурных видеочастотных компонентов I(t) и Q(t) принимаемой структурной помехи.

Результаты перемножения квадратурных составляющих входного и опорных сигналов объединяются в вычитателе 111 и сумматоре 12, образуя соответственно «косинусную» и «синусную» квадратурные составляющие, пропорциональные cosφ(t) и sinφ(t), где φ(t) - фазовая ошибка системы синхронизации (составляющие удвоенной частоты ω0 подавляются при последующей обработке). Интеграторы 131 и 132 в квадратурных каналах фазового дискриминатора 8 осуществляют интегрирование поступающих на их входы квадратурных составляющих сжатой по спектру структурной помехи на интервалах, равных периоду Тп повторения ШПС (одинаковому для полезного сигнала и структурной помехи). Сброс интеграторов 131 и 132 осуществляется с шагом Тп синхроимпульсами, вырабатываемыми дешифратором 20 блока 6 кодовой синхронизации.

Результаты z1 и z2 интегрирования в квадратурных каналах фазового дискриминатора 8, пропорциональные величинам Acosφ и Asinφ, где А - амплитуда СП, поступают на выходной перемножитель 97, формирующий сигнал ошибки zд(φ), пропорциональный фазовому рассогласованию принимаемой структурной помехи и опорных сигналов частоты ω0. При этом составляющая z2 поступает на сигнальный вход перемножителя 97 непосредственно, а составляющая z1 поступает на опорный вход перемножителя 97 через решающий блок 141, осуществляющий преобразование вида sign(z1) (знаковая функция), т.е. формирующий оценку информационного символа помехи, благодаря чему исключается влияние цифровой модуляции D(t)∈[1,-1] структурной помехи на формирование сигнала ошибки zд(φ).

Выходной сигнал петлевого фильтра 151, сглаживающего флуктуации сигнала ошибки zд(φ), обусловленные действием шума, используется для управления частотой и фазой опорных сигналов, формируемых подстраиваемым генератором 10 несущей частоты структурной помехи.

Блок 6 кодовой синхронизации работает следующим образом. Сигнал с выхода сумматора 12 поступает на вход перемножителя 98, где перемножается с опорной инверсной кодовой последовательностью -d(t). Прямой код d(t)∈[1,-1] используется при формировании опорных видеочастотных сигналов I(f) и Q(t) в синтезаторе 19 опорных квадратурных сигналов. Оба кода (прямой и инверсный) формируются генератором 18 кода. Выходной сигнал перемножителя 98 интегрируется на интервалах, равных периоду Тп повторения ШПС, в результате чего на выходе интегратора 133 образуется сигнал ошибки, поступающий на сигнальный вход перемножителя 99. С помощью перемножителя 99 исключается влияние цифровой модуляции структурной помехи на формирование сигнала ошибки, пропорционального временному рассогласованию принятой СП и опорных квадратурных сигналов I(t) и Q(t). Достигается это путем подачи на опорный вход перемножителя 99 оценки информационного символа с выхода решающего блока 141. Петлевой фильтр 152 сглаживает флуктуации сигнала ошибки, формируя управляющий сигнал для управляемого фазовращателя 17. Меандровый сигнал тактовой частоты fт=1/T формируется делителем 21 частоты путем деления несущей частоты f0:fт=f0/m, m - целое.

На вход генератора 18 кода меандровый сигнал тактовой частоты поступает через управляемый фазовращатель 17. Формируемая генератором 18 кода кодовая последовательность (прямой код d(t)) поступает на вход синтезатора 19 опорных квадратурных сигналов, определяя знак приращения фазы π/2 на интервалах, равных длительности Т элемента кода.

С выходов синтезатора 19 опорные квадратурные сигналы I(t) и Q(t) поступают соответственно на перемножители 93 и 96, 94 и 95 фазового дискриминатора 8 блока 5 фазовой синхронизации, а также на перемножители 912 и 913 модулятора 2. Дешифратор 20, подключенный к генератору 18 кода, формирует синхроимпульсы с частотой повторения Fп=1/Тп для интеграторов 131, 132 и 133 фазового и временного дискриминаторов 8 и 16, а также для интегратора 134 блока 7 оценки амплитуды.

Блок 7 оценки амплитуды работает следующим образом. Результат z1 интегрирования в синфазном канале фазового дискриминатора 8 поступает на сигнальный вход перемножителя 910 через аттенюатор 22, формирующий оценку амплитуды СП: DA=2z1/М, где М=ТП/ТД - число отсчетов на интервале интегрирования, ТД - интервал дискретизации. На опорный вход перемножителя 910 поступает оценка информационного символа D с выхода решающего блока 141, благодаря чему исключается влияние цифровой модуляции СП на формирование оценки амплитуды структурной помехи. Фильтр нижних частот 23 служит для сглаживания флуктуации оценки амплитуды А помехи. При превышении оценкой амплитуды А заданного порогового уровня на выходе порогового элемента 24 формируется команда на включение блока 3 режекции в тракт приема полезного сигнала.

Интегратор 134 осуществляет интегрирование поступающей на его вход синфазной составляющей сжатой по спектру структурной помехи на интервалах, равных длительности элемента Т. При этом на первый синхронизирующий вход интегратора 134 поступают синхроимпульсы тактовой частоты fт с выхода делителя 21 частоты, что обеспечивает установку на выходе интегратора 134 текущего значения результата интегрирования z1k на интервале 0<t≤kТ, k=1, 2, …, N, где N - длина кода. Результат интегрирования z1k поступает на вход решающего блока 142, осуществляющего оценку информационного символа структурной помехи Dk на момент t=kТ путем выполнения преобразования вида sign(z1k). Перемножитель 811 формирует оценку амплитуды СП с использованием оценки информационного символа Dk, которая используется в модуляторе 2 для формирования копии структурной помехи.

Модулятор 2 работает следующим образом. Перемножители 912 и 913 осуществляют формирование квадратурных составляющих копии структурной помехи путем перемножения опорных видеочастотных сигналов I(t) и Q(t), вырабатываемых синтезатором 19, с опорными квадратурными сигналами cos(ω0t) и sin(ω0t) соответственно, формируемыми подстраиваемым генератором 10 несущей частоты.

В перемножителе 914 формируется копия структурной помехи с точностью до амплитуды (с учетом цифровой модуляции СП) путем перемножения выходного сигнала единичной амплитуды вычитателя 112 и оценки амплитуды, сформированной перемножителем 911. Выходной сигнал блока 3 режекции представляет собой очищенный от помехи полезный сигнал, который поступает на второй вход коммутатора 4.

Коммутатор 4 по команде с выхода порогового элемента 24 осуществляет "включение блока 3 режекции в тракт приема полезного сигнала.

В установившемся режиме работы устройства степень подавления структурной помехи определяется точностью слежения за задержкой и фазой СП (точностью систем кодовой и фазовой синхронизации), а также точностью оценки амплитуды и информационных символов СП.

На фиг.2 представлены результаты имитационного моделирования устройства компенсации структурных помех для приемников шумоподобных сигналов с минимальной частотной манипуляцией для случая отсутствия шума: зависимость нормированной по значению А структурной помехи на выходе устройства компенсации от времени при параметрах СП N=16383, Тп=40 мс. Как видно из рисунка, по завершении переходного процесса (при выбранных параметрах следящих фильтров и ФНЧ 23 блока 7 оценки амплитуды время переходного процесса составляет около 1 с) устройство обеспечивает подавление СП около 60 дБ. При наличии шума степень подавления структурной помехи определяется погрешностью оценок амплитуды, задержки и фазы СП. Так в случае, когда ошибка измерения амплитуды составляет 1%, задержки - 0,01T и фазы - 0,01 фазового цикла (среднеквадратические значения), подавление СП составляет около 40 дБ.

Заявляемое устройство может быть реализовано на современной цифровой элементной базе, в частности, с использованием программируемых логических интегральных схем (ПЛИС).

Пример цифровой реализации синтезатора опорных квадратурных сигналов с использованием накапливающего сумматора (аккумулятора фазы) и постоянного запоминающего устройства для хранения отсчетов квадратурных сигналов приведен в монографии [Цифровые системы фазовой синхронизации. / М.И.Жодзишский, С.Ю.Сила-Новицкий, В.А.Прасолов и др.; Под ред. М.И.Жодзишского. - М.: Сов. Радио, 1980. - с.55-57].

По сравнению с устройством-прототипом предлагаемое устройство позволяет повысить эффективность компенсации структурной помехи за счет высокой точности фазовой и кодовой синхронизации, а также обеспечивает подавление СП в реальном масштабе времени.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО КОМПЕНСАЦИИ СТРУКТУРНЫХ ПОМЕХ | 2013 |

|

RU2534221C1 |

| КОРРЕЛЯЦИОННЫЙ ПРИЕМНИК ШУМОПОДОБНЫХ СИГНАЛОВ С МИНИМАЛЬНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 2008 |

|

RU2374776C2 |

| КОРРЕЛЯЦИОННЫЙ ПРИЕМНИК ШУМОПОДОБНЫХ СИГНАЛОВ С МИНИМАЛЬНОЙ ЧАСТОТНОЙ МОДУЛЯЦИЕЙ | 2014 |

|

RU2548010C1 |

| КОРРЕЛЯЦИОННЫЙ ПРИЕМНИК ШУМОПОДОБНЫХ СИГНАЛОВ | 2010 |

|

RU2431919C1 |

| СПОСОБ ПРИЕМА ШУМОПОДОБНЫХ СИГНАЛОВ С МИНИМАЛЬНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 2006 |

|

RU2307474C1 |

| УСТРОЙСТВО УСКОРЕННОЙ СИНХРОНИЗАЦИИ ПРИЕМНИКА ШУМОПОДОБНЫХ СИГНАЛОВ С МИНИМАЛЬНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 2011 |

|

RU2446560C1 |

| УСТРОЙСТВО ДЛЯ РАЗДЕЛЕНИЯ ДВУХ ЧАСТОТНО-МОДУЛИРОВАННЫХ СИГНАЛОВ С ПЕРЕКРЫВАЮЩИМИСЯ СПЕКТРАМИ | 1991 |

|

RU2065666C1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ ПРИЕМНИКА ШУМОПОДОБНЫХ СИГНАЛОВ С МИНИМАЛЬНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 2007 |

|

RU2357359C2 |

| УСТРОЙСТВО ПОДАВЛЕНИЯ ШИРОКОПОЛОСНЫХ ПОМЕХ | 2000 |

|

RU2190297C2 |

| СПОСОБ ПРИЕМА ШУМОПОДОБНЫХ ЧАСТОТНО-МАНИПУЛИРОВАННЫХ СИГНАЛОВ С НЕПРЕРЫВНОЙ ФАЗОЙ | 2006 |

|

RU2323536C1 |

Изобретение относится к области радиотехники и может использоваться в приемниках шумоподобных сигналов с минимальной частотной манипуляцией. Технический результат заключается в повышении эффективности компенсации структурной помехи в реальном масштабе времени за счет высокой точности формирования ее копии. Для достижения технического результата устройство содержит приемник мешающего сигнала, включающий блок фазовой синхронизации, содержащий фазовый дискриминатор, петлевой фильтр и подстраиваемый генератор несущей частоты, блок кодовой синхронизации, содержащий когерентный временной дискриминатор, петлевой фильтр, управляемый фазовращатель, делитель частоты, генератор кода, дешифратор и синтезатор опорных квадратурных сигналов, и блок оценки амплитуды, а также модулятор, блок режекции и коммутатор. 2 ил.

Устройство компенсации структурных помех, содержащее приемник мешающего сигнала, модулятор, блок режекции, один вход которого соединен с выходом модулятора, коммутатор, первый и второй входы которого соединены соответственно с входом устройства и выходом блока режекции, а третий вход которого подключен к командному выходу приемника мешающего сигнала, отличающееся тем, что вход устройства соединен с вторым входом блока режекции и входом приемника мешающего сигнала, содержащего блок фазовой синхронизации, включающий фазовый дискриминатор, содержащий первый и второй перемножители, сигнальные входы которых соединены с входом устройства, третий и четвертый, пятый и шестой перемножители, выходы которых объединены соответственно через первый вычитатель и сумматор, первый и второй интеграторы, входы которых соответственно подключены к выходам первого вычитателя и сумматора, первый решающий блок, осуществляющий знаковую функцию для оценки информационного символа, вход которого подключен к выходу первого интегратора, а выход которого соединен с опорным входом седьмого перемножителя, сигнальный вход которого подключен к выходу второго интегратора, а к выходу которого подключены последовательно соединенные первый петлевой фильтр и подстраиваемый генератор несущей частоты, квадратурные выходы которого соединены соответственно с опорными входами первого и второго перемножителей, при этом сигнальные входы третьего и пятого, четвертого и шестого перемножителей попарно объединены и подключены к выходам соответственно первого и второго перемножителей, блок кодовой синхронизации, включающий последовательно соединенные временной дискриминатор, содержащий последовательно соединенные восьмой перемножитель, сигнальный вход которого подключен к выходу сумматора, третий интегратор, синхронизирующий вход которого соединен с синхронизирующими входами первого и второго интеграторов и подключен к выходу дешифратора, подключенного к дополнительным выходам генератора кода, и девятый перемножитель, опорный вход которого подключен к выходу первого решающего блока, второй петлевой фильтр и управляемый фазовращатель, другой вход которого соединен с выходом делителя частоты, входом соединенного с первым квадратурным выходом подстраиваемого генератора несущей частоты, а выход которого соединен со входом генератора кода, инверсный выход которого соединен с опорным входом восьмого перемножителя, а прямой выход которого соединен со входом синтезатора опорных квадратурных сигналов, выходы которого соединены соответственно с попарно объединенными опорными входами третьего и шестого, четвертого и пятого перемножителей, блок оценки амплитуды, содержащий аттенюатор, вход которого подключен к выходу первого интегратора, а выход которого соединен с сигнальным входом десятого перемножителя, опорный вход которого подключен к выходу первого решающего блока, последовательно соединенные фильтр нижних частот, вход которого подключен к выходу десятого перемножителя, и пороговый элемент, выход которого является командным выходом приемника мешающего сигнала, последовательно соединенные четвертый интегратор, вход которого подключен к выходу первого вычитателя, а первый и второй синхронизирующие входы которого соединены соответственно с выходом дешифратора и выходом делителя частоты, и второй решающий блок, осуществляющий оценку информационного символа, к выходу которого подключен один вход одиннадцатого перемножителя, другой вход которого соединен с выходом фильтра нижних частот, а выход которого является выходом блока оценки амплитуды, модулятор, содержащий двенадцатый и тринадцатый перемножители, сигнальные входы которых подключены соответственно к квадратурным выходам подстраиваемого генератора несущей частоты, опорные входы которых соединены соответственно с выходами синтезатора опорных квадратурных сигналов, а выходы которых объединены через второй вычитатель, выход которого соединен с сигнальным входом четырнадцатого перемножителя, опорный вход которого подключен к выходу блока оценки амплитуды, а выход которого является выходом модулятора.

| СПОСОБ ПОДАВЛЕНИЯ СТРУКТУРНЫХ ПОМЕХ В ПРИЕМНИКЕ БАЗОВОЙ СТАНЦИИ СИСТЕМЫ СВЯЗИ С КОДОВЫМ РАЗДЕЛЕНИЕМ КАНАЛОВ И УСТРОЙСТВО ЕГО РЕАЛИЗАЦИИ | 1996 |

|

RU2122283C1 |

| УСТРОЙСТВО КОМПЕНСАЦИИ ПОМЕХ ДЛЯ ПРИЕМНИКОВ ШИРОКОПОЛОСНЫХ ФАЗОМАНИПУЛИРОВАННЫХ СИГНАЛОВ | 1999 |

|

RU2143781C1 |

| Цифроаналоговый преобразователь с автокалибровкой | 1986 |

|

SU1361720A1 |

Авторы

Даты

2012-05-10—Публикация

2010-05-07—Подача