Изобретение относится к вычнслнтельиой технике, в частности к устройствам для регистрации информации, и мо) быт использовано в спектроскопии магнитного резонанса.

Известен многоканальный регистратор, содержащий регистр адреса, первая группа выходов которого соединена с адресными Входами запоминающего блока, информаиконные выходы которого соединены с группой входов регистра числа, соединенного через аналого-цифровой преобразователь с входом многоканального рег-истратора, выход которого соединен с выходом блока формирования импульсов, счетчик, соедиценный с первой группой входов схемы сразнения, блок управления, выходы которо соединены с входами регистра адреса, запоминающего блока и регистра числа, причем выходы регистров адреса я числа череэ соответствующие ци о-аналоговые преобразователи соединены с инднкационнымм выходами многоканального регистратора. Одвахо отсутствие возможности одиовременной регистрации и отображения ин формации , в особенности при низкой частоте повторения импульсов, снижает быстродействие регистратора.

Цель изобретения - повышение производительности устройства.

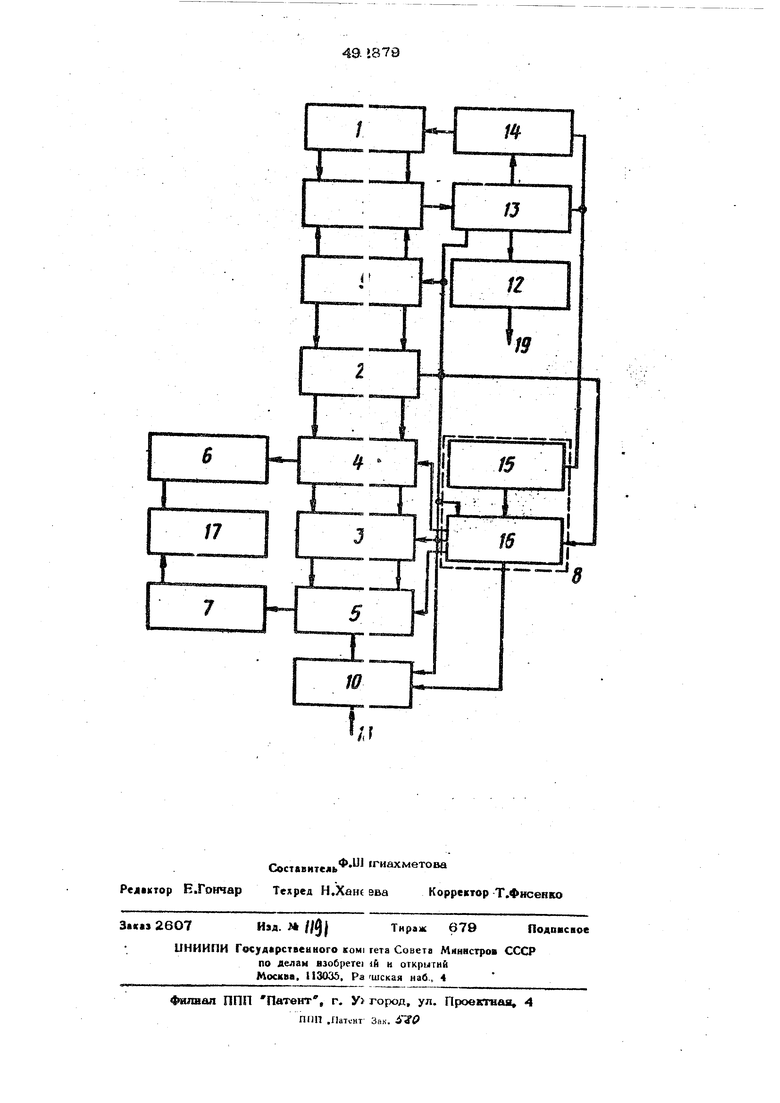

Достигается это тем, что многоканаль регистратор содержит реверюивный счотчик, дополнительную схему сравнения, блр формирования интервалов и блок программ причем соответствующий выход блока управления соединен с первыми входами блока формирования интервалов и блока прог рамм, выходы которого соединены с входом блока формирования импульсов, со вторым входом блока формирования ннте( валов, с соответствующим входом аналого-цифрового преобразователя, первым входом блсжа yпpaвn гния и входом |хэвврсивного счетчика, первая группа выходом которого и вторая группа выходов регист ра адреса соединены с группами входов дополнительной схемы сравнения, выход которой сс динен со вторым входом блока управления второй вход блока программ 3 ссх динен с выходом схемы сравнения, вто рая группа входоа которой соединена со второй группой выходов реверсив11О1о сче чика, а выход блока формирования интервалов соединен со входом счетчика. На чертеже блок-схема многоканаль ного регистратора. Многоканальный регистратор содержит схемы сравнения 1 и 2, запоминающий блок 3, регистр адреса 4, регистр числа 5, цифро-аналогшыб иреобра зователи 7, блок управления 8, реверсивный счетчик 9, аналого-цифровой преобразсхватель счетчик 11, блок 12 формирований импул сов, блок программ 13, блок 14 формиро вания интервалов. Кроме того на чертеже обозначены ге нератор 15 тактовых частот, узел 16 уп равления, устройство 17 ивдикадии, вход 18 и выход 19 многоканального ре гистратора. Регистратор работает следующим образом, В регистраторе реализуется режим непрерывного наблюдения информации, храняшейся в запоминающем блоке 3. При этом по сигналам из блока управления 8 регистр адреса 4 выбирает последовательно ячейки запомиигдюшетО блока содержимое которых выводится на регист числа 5. Коды иу регистра адреса 4 и регистра числа 5, iipoo6paooBai Hue и ана логовые величины iui(|po-аналоговыми пре образователями G и 7i поступают на уст ройство индикации 17, на экране которого наблюдается график зарегистрировлнной функции. Период опроса всех ячеек запоминающего блока. 3 - Т t//, где - время обращения к одной ячейке запоминающего блока 3, а /V - число ячеек запоминающего блока 3. Период Т задае1х:я 1« нератором так товых частот 15, блока управления 8, На выходе 19 многоканального регист ратора вырабатьшается серия импульсов с периодом повторения Т и Т периода опроса всех ячеек запоминающего блока Выполнение этого условия необходимо для того, чтобы обеспечи1Ъ регистршшю сигнала, возбужденного предшествующей серией импульсси), в /побои ячейке запоминающего блока 3 за время генералин последующей серии импульсов. По пусковому импульсу, псх;тупающе из генератора 15 тактовых частот блок программ 13 посылает команду в блок 1 формирования импул1х:ов иа формирование первого импульса серии и в блок 14 фор мирования интервалов на форми1ювание первого интервала между имнульс;ами, Бл формирован{)й интервалов можот вырабатьгаать несколько пнтерволов фиксиропа ной д iи№лы oeтиo Пусть первый интервал имеет фиксированную длнтельнсють Тогда блок 14 формирования KBi epaanoB вырабатывает оди из фиксироваршых интервалов, и сигнал Конец интервала поступает в блок программ 13а который вырабатывает KOiv-sanfibi на формирование второго имГЕульса и второго и тервдлао Допустим что следующий интервал имеет переменную длительность, Зтот интервал формируется путем многократного повто|:юния одного кз фиксированных интервалов, В этом случае скгиалы Коиеи итчэрвала из GjiOKa 14 формирования инторвалов постуггают в счет- чкк 11 до тех порг пока код в счетчике 11 не будет равен KOayj записанному в реве сивном счетчике 9, и на выходе CK. сравнеинп 1 не появится сигнал, KOTOpbtii поступит в блок программ 13, На этом формирова)ие переменного интервала закапмюзлется, программ 13 при этом вырабатывает команды на форми)ОВс11 ио очередного импульса и интервала серии. После отработки пос; едиего интервала серии (этот момент соответ :тиует полвлепию полезного сигнала иа входе 18 многокаиалг. регистратора) с выхода блока программ 13 в аналого-цифровой преобразователь 10 п;х:туиает команда на преобразование входного сигнала цифровой код; а в блок управле ия 8-на paspeujeiuie прж.мч сигнала со схемы сравнения 2., Кроме того, сигнал с выхода блока программ 13 поступает на вход реверсивного счетчика 9 и код, эапислпный в счетчике 9, увеличивается .или уме Ы11нетсн на , обуспав;глвая том самым изменение задержки .между импульсами {переменные интервалы) при генергшни следующей серии. Генерация следующей серии начинается с приходом очередного пускового импульса с генератора 15 тактовых частот 6jjOKa управления 8, и, практически, может начаться сразу же после выдачи команды с выхода блока программ 13, пск;кольку в cooTBei-CTBKH с условием Т и Т, все ячейки Запоминающего блока 3 будут оп. рошены и входной сигнал, по/гученпый в 11р8дыдущей серии импул1 сов, будет аа|)егис1 рирован преаше. Чем появится оче1)едной командный импульс на выходе блока программ 13, Сигнал и а выходе схемы сравнения 2 noявJ яeтcя в момент когда код в регистре адреса 4 равен коду в реверсивном счетчике 9,.т.е. длительность перемешш цч тервалон серии приведена в соответствие с номером ячейки запоминающего блока 3.

Сигвая с Boixona с;хомы сравнення 2 яостукает Б узоп управления 16 блока укравгю-гПИ-; 8, к «гсследний вырабатьтЁвет коман- дь- па navievj а.ода нз ана юго-цифрового преобрааоБат-е.гш 10 в persscTp чисиа 5 н сумммройанне . с за писан jaiM ранее числом в яанной ячейке запоминшошего бпока 3.

Таки.- c6f3a30fvf3 обеспоЧлзается многоканального регистратора щж непрарьгаг.ом набгоодекйк за ходом акепердалвнта для случая вязкой частоть пов1 ренкя серий имгг/льеов, что позволяет увеличить бь Строяейств-«8 perHCTpavopa.

Предлагаешь;и 1ч«югокан(ЛЬР-ь;й р-эгисТ |ратор пайт приь еиекиш для управneisiiH кмпульскьпч-: шерным магнитным реsoHaHcotvf ЯМР - релаксоыетро-л- нпй другой ехспериментапьной установкой.

Предмет к з о б р е т н я

М110гокаиапьнь Й регистратор, содержаaiKfi рзг«стр гщроса, первая группа выходов которого соединена с адресными входами aanoMT-nias-ouiero бпокп, ии4 рма11ИОнные выходы которого соедине1 Ь с группой входов регистра числа, соединенного через анапого-Цпфровой преобразователь с входом мпо гоканальиого регистратора, выход которого соекиисн с выходом блока формирования UMir/fibcoBj c4eT4HKs соейкке1Г(ый с первой

6

группой входов схемы сравнения, блсчс управления, выходы которого соединены с входами регистра адреса, запоминающего блока и регистра числа, причем выхсщы регистров адреса и micnti через соответствующие цифро-аналоговые преобразователи соединены с индикационными выходами регистратора, OjT л и ч а да щ и fl с я тем,, что, с целью повышения производительности устройства содержит реверсивный , дополнительную схему сравнения, блок формирования интервалов и блок програкМ, причем соответствующий выход блока управления соединен с первыми входами блока формирования Иllтep aлol и блока программ, выходы которого соединены с входом блока феркировлния импульсов, со вторым входом блока формиронании ингервалов, с соответствующим входом аиалого-иифрового преобразователя, iinpiibiKi входом блока

0 управления и входом ров(р:ио11ого счетпи- sea, первая группа йыходоп ксугорого и вто- рея группа выходов регистра соединены с группами входов домапиительной схемы сравнения, выход которой со{;динвн со вторым входом блок1 управления, второй вход блока программ с(.единси с выходом схемы сравнения, впорая группа входов которой соединена со (jropoff r-pyimofl выходов-реверсивного счетчика, а выход блока ) формирования иптерналов со 1дино1 с входом счетчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный формирователь серии импульсов | 1980 |

|

SU932601A1 |

| Устройство для построения гистрограммы -интервалов | 1978 |

|

SU721079A1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ВЕНТИЛЬНЫМ ПРЕОБРАЗОВАТЕЛЕМ | 1991 |

|

RU2064730C1 |

| УСТРОЙСТВО ДЛЯ РЕГИСТРАЦИИ ИНФОРМАЦИИ | 1996 |

|

RU2097703C1 |

| Многоканальное устройство для програмного управления | 1980 |

|

SU875339A1 |

| Устройство для передачи асинхронных сигналов | 1982 |

|

SU1075288A2 |

| Микропроцессорное устройство для управления вентильным преобразователем | 1985 |

|

SU1356155A1 |

| СПОСОБ n-КАНАЛЬНОЙ РЕГИСТРАЦИИ ИНТЕРВАЛОВ ВРЕМЕНИ И РЕГИСТРАТОР ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2005 |

|

RU2287846C1 |

| Устройство для сопряжения интерфейса ввода-вывода с регистратором | 1983 |

|

SU1144100A2 |

| Многокоординатное устройство для управления | 1987 |

|

SU1522155A1 |

Авторы

Даты

1975-11-25—Публикация

1973-01-15—Подача