1135

Изобретение относится к электротехнике-, а именно к устройствам им- пульсно-фазового управления вентильными преобразователями частоты, работающими от трехфазной сети переменного тока, с использованием методов цифровой обработки информации, и может быть применено в реверсивном

злектроприводе постоянного тока..

Цель изобретения - расширение функциональных возможностей путем увеличения количества вводимых и выводимых в параллельном коде сигналов

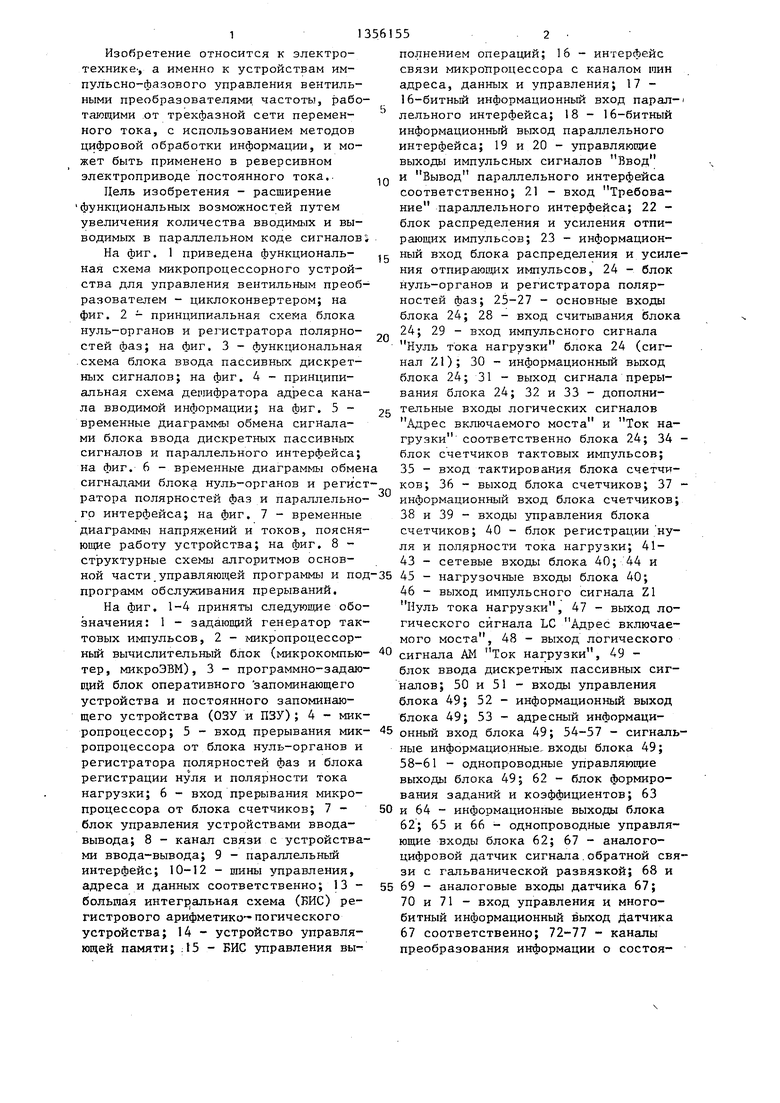

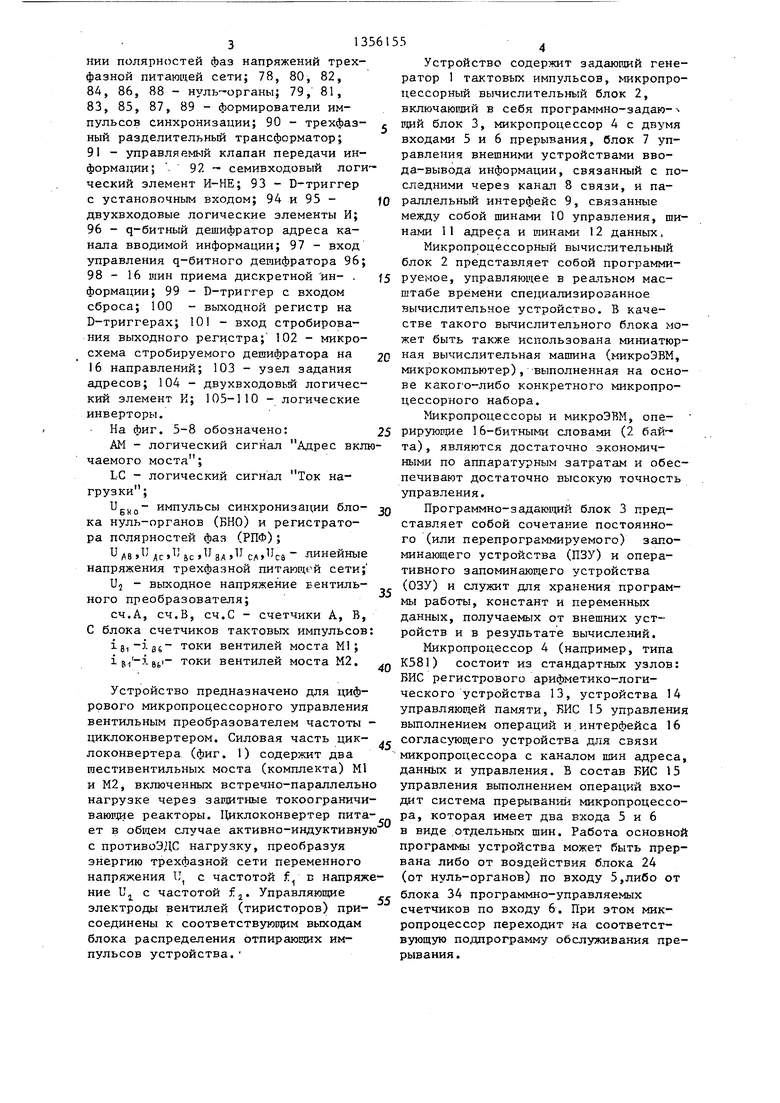

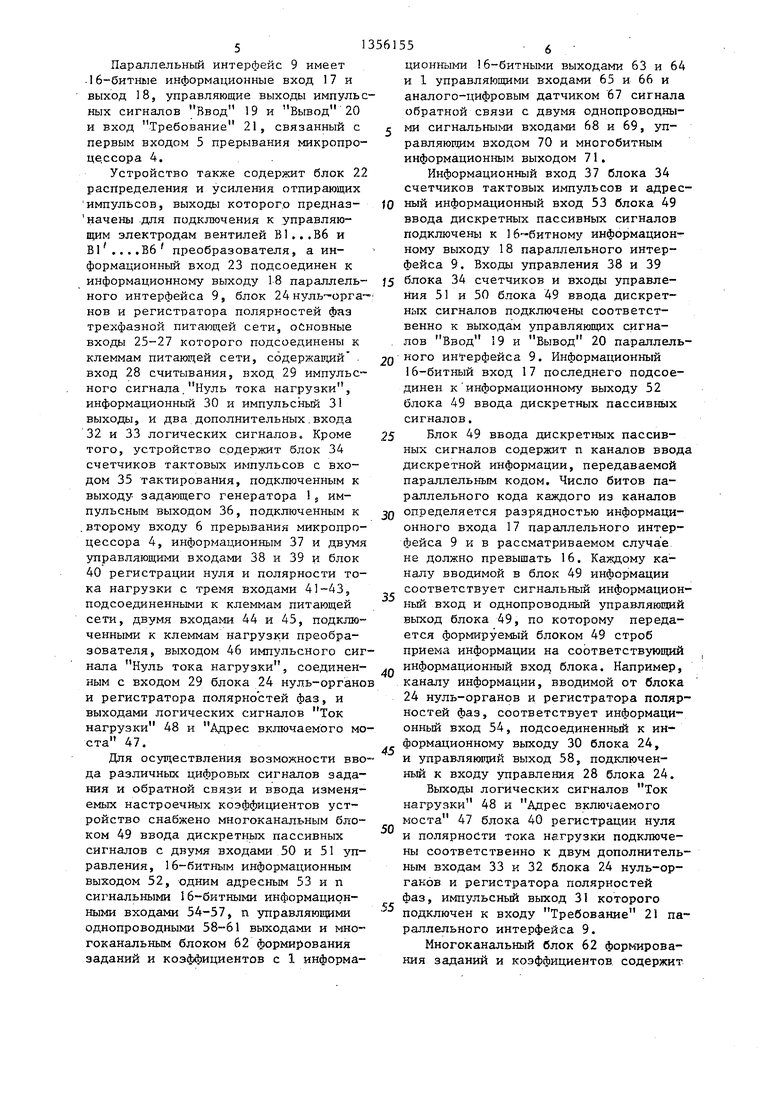

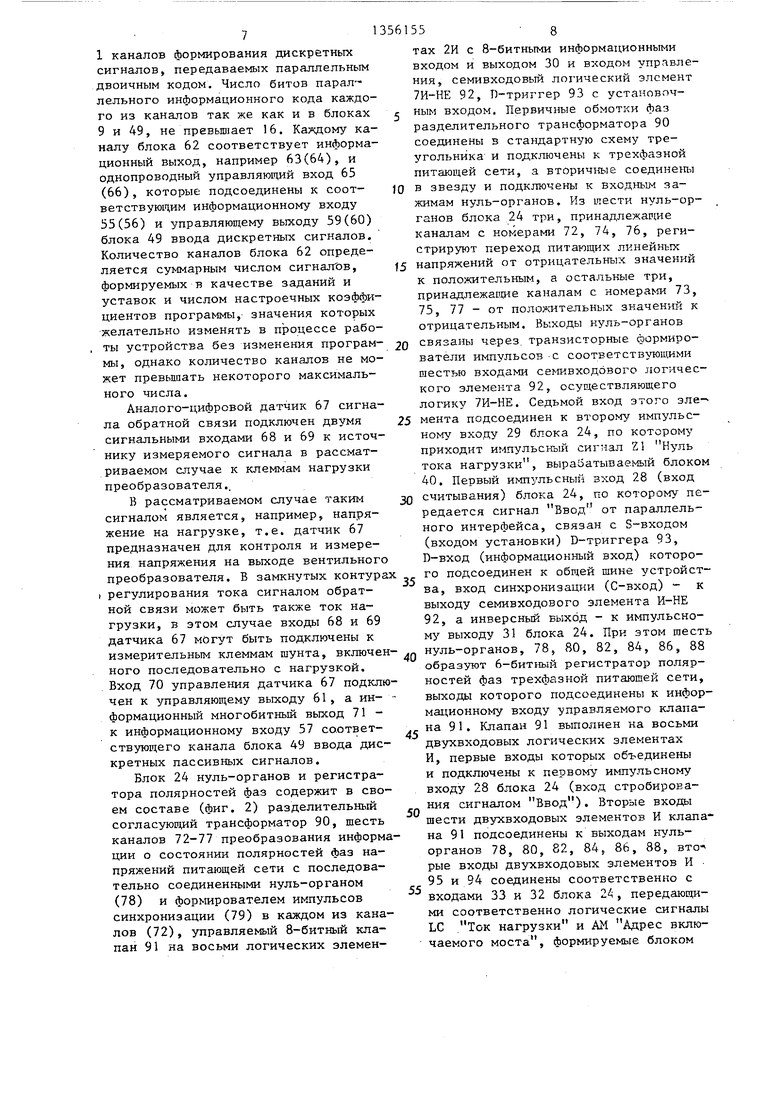

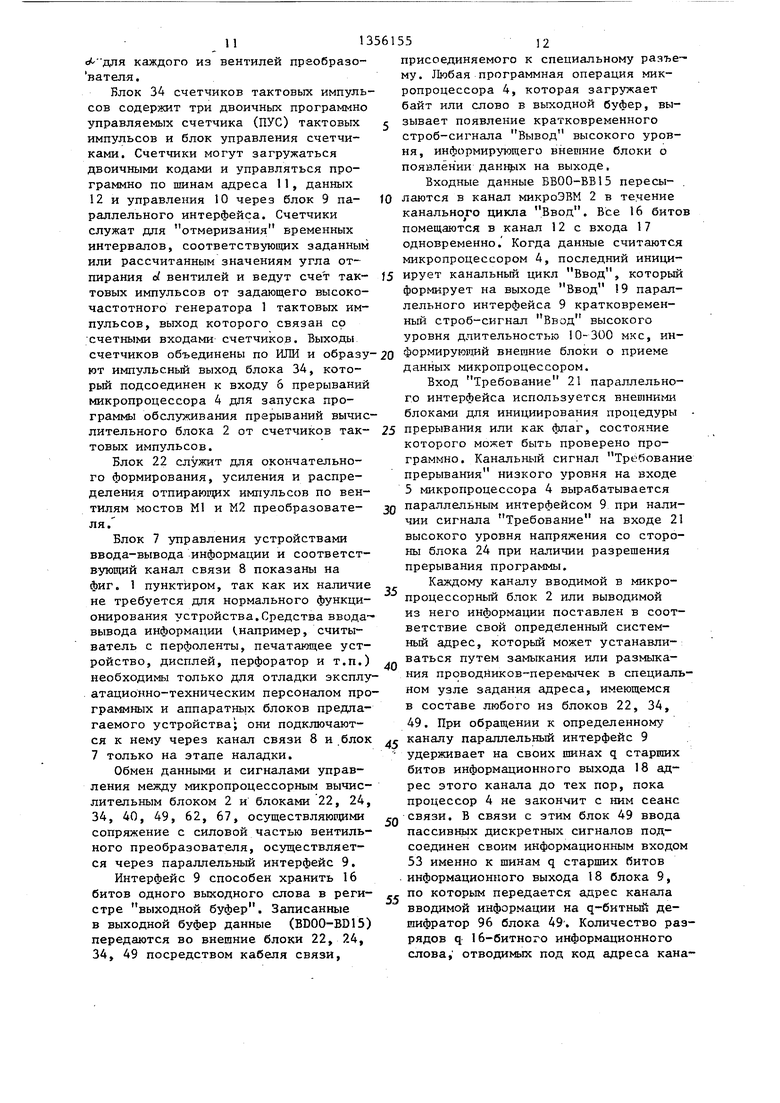

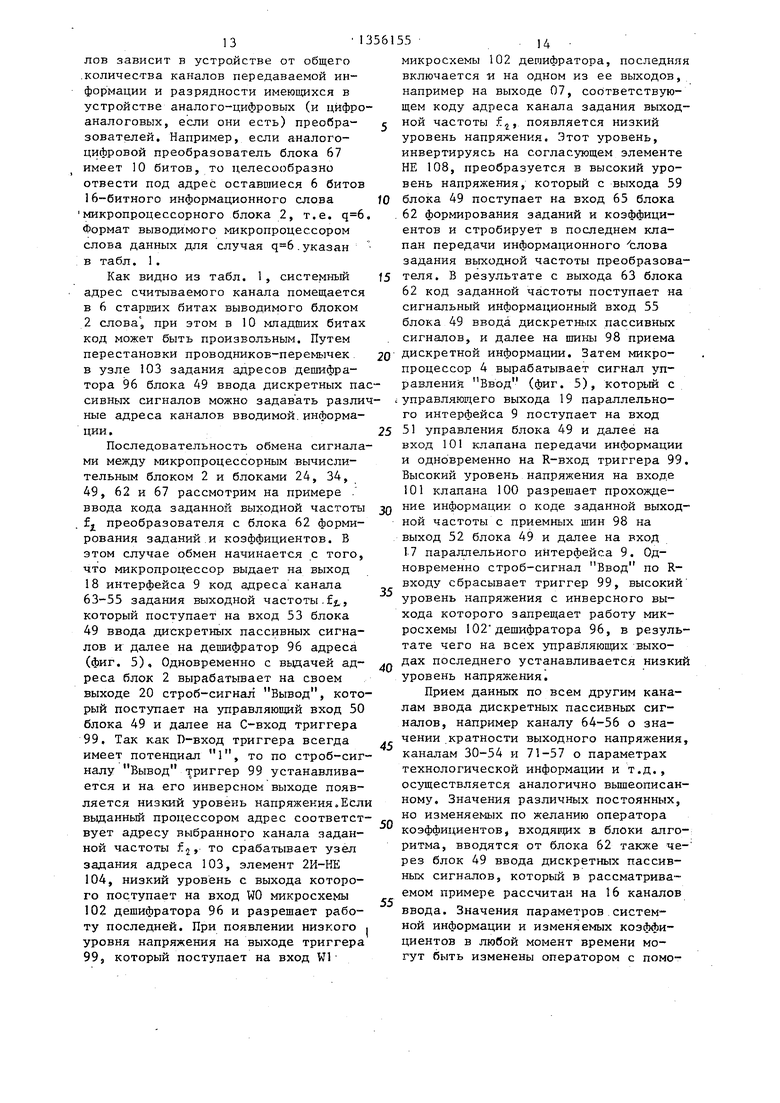

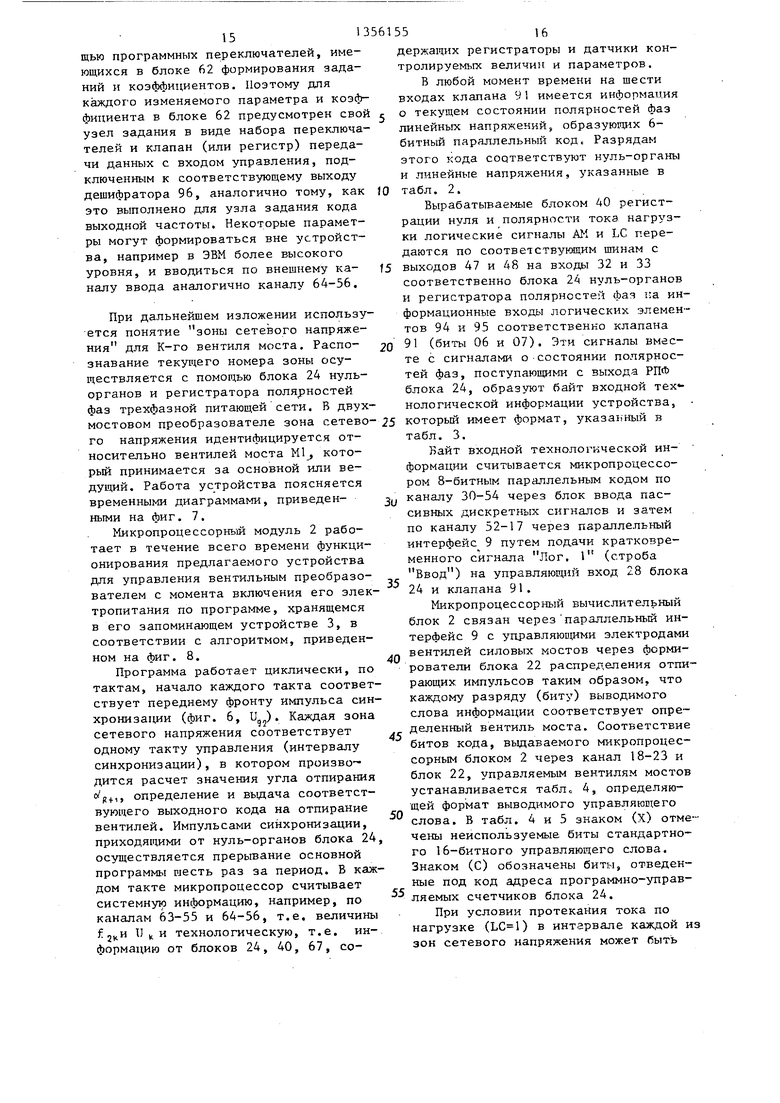

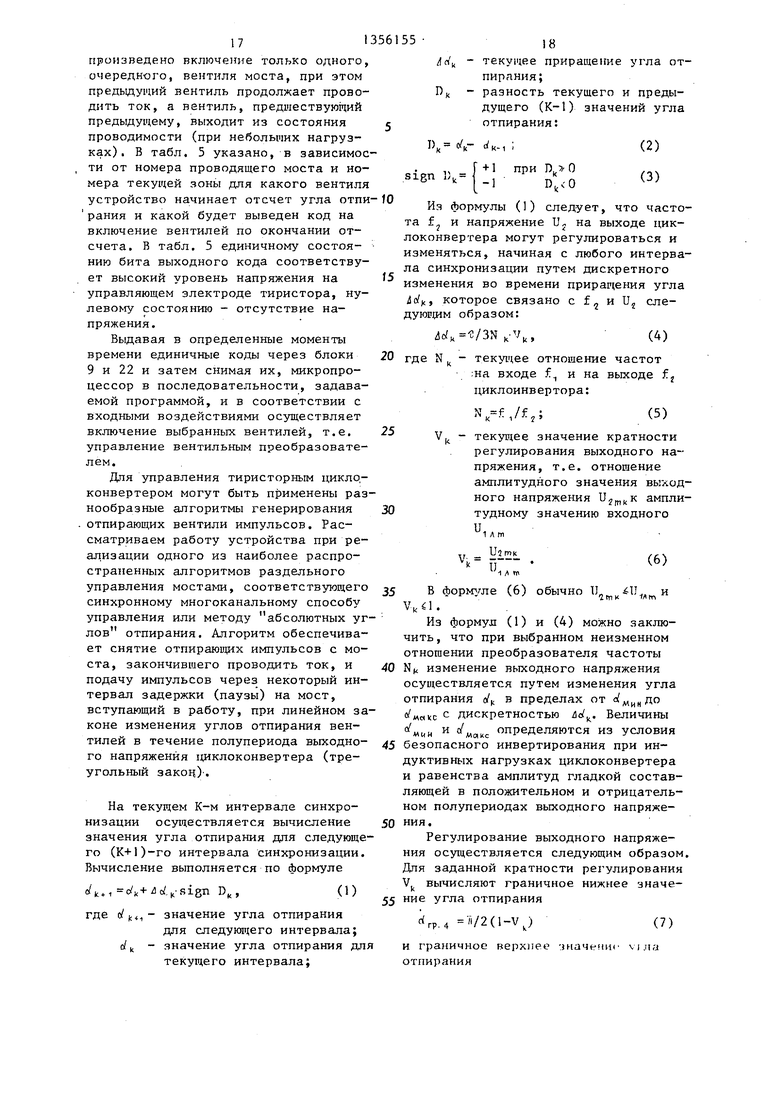

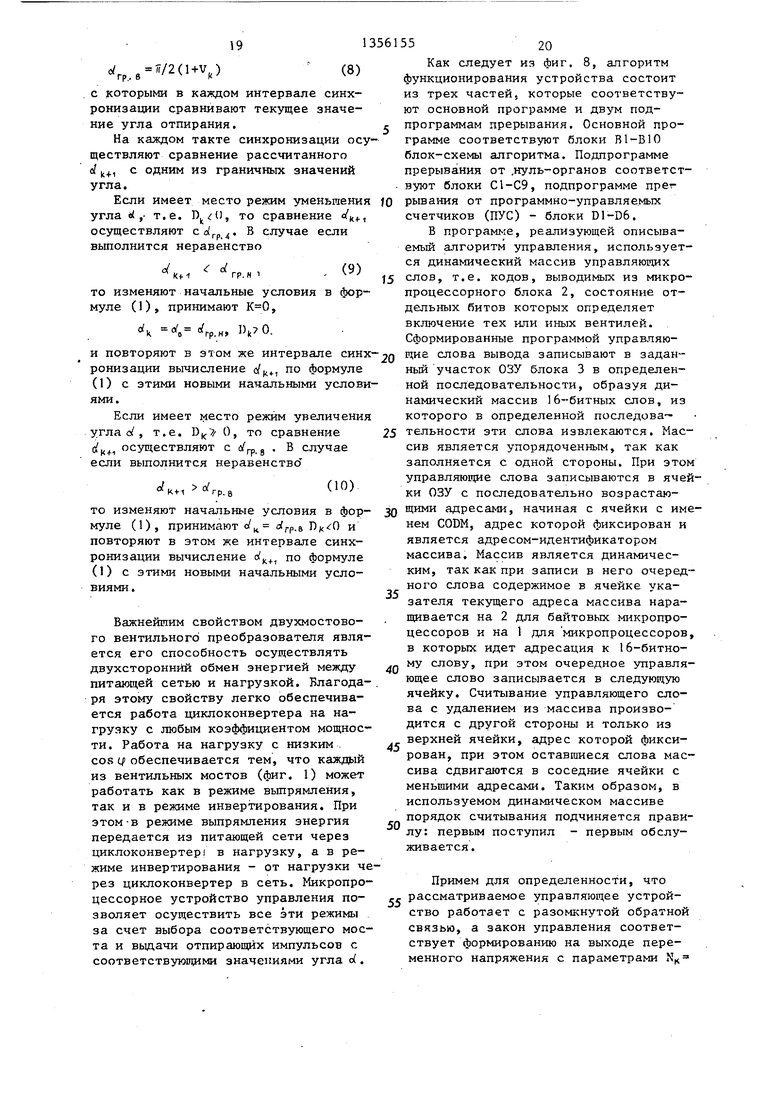

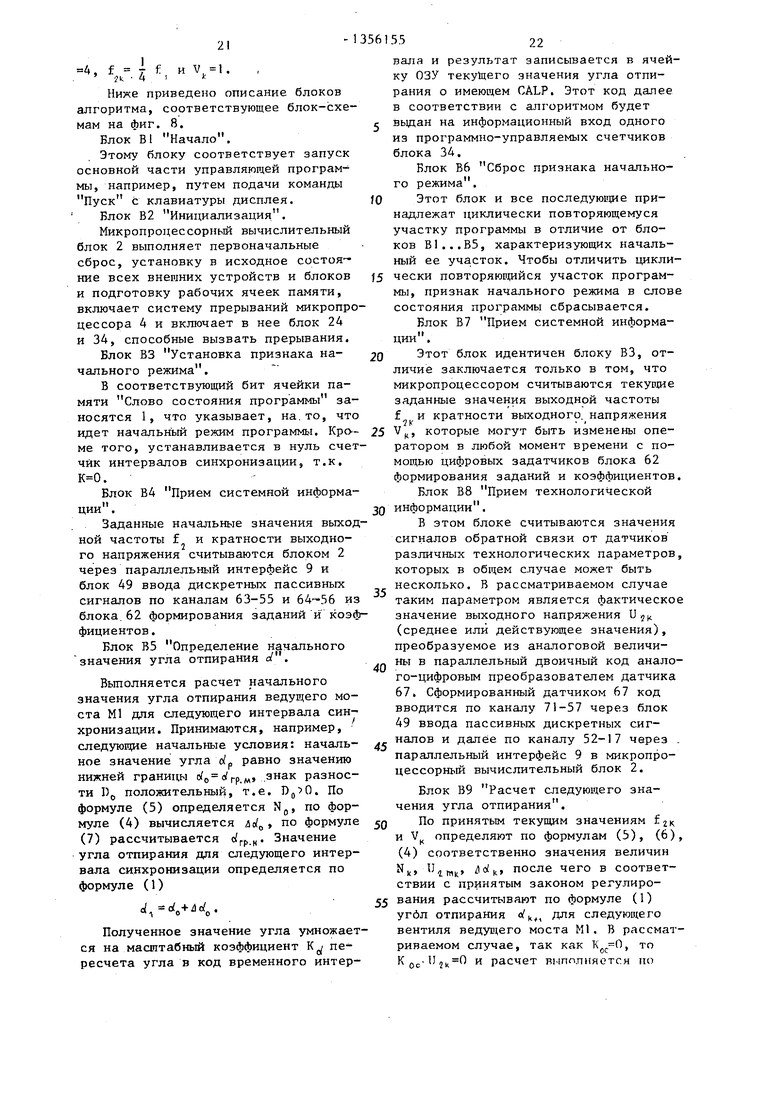

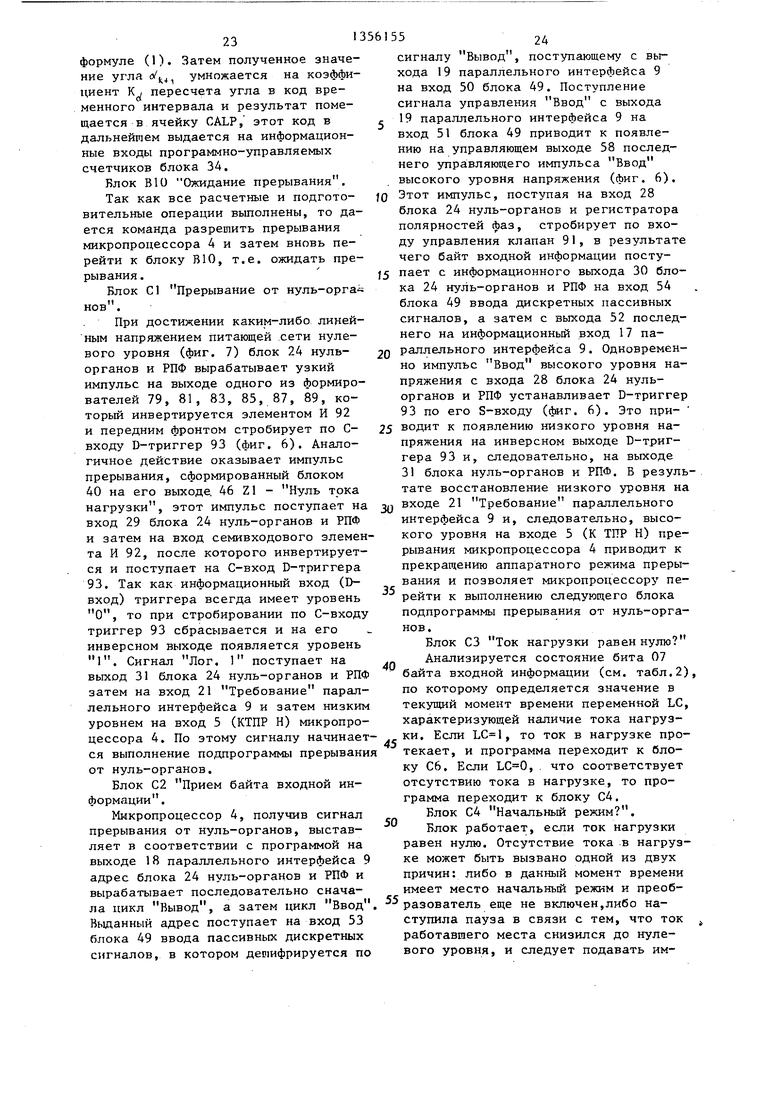

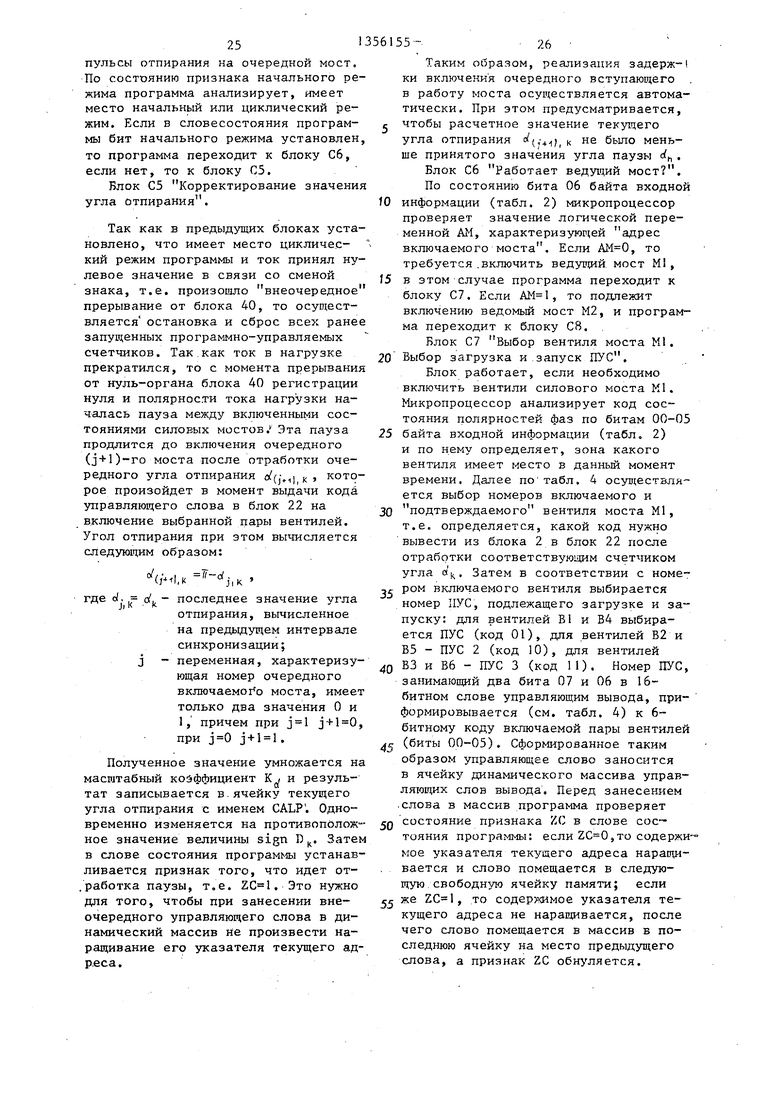

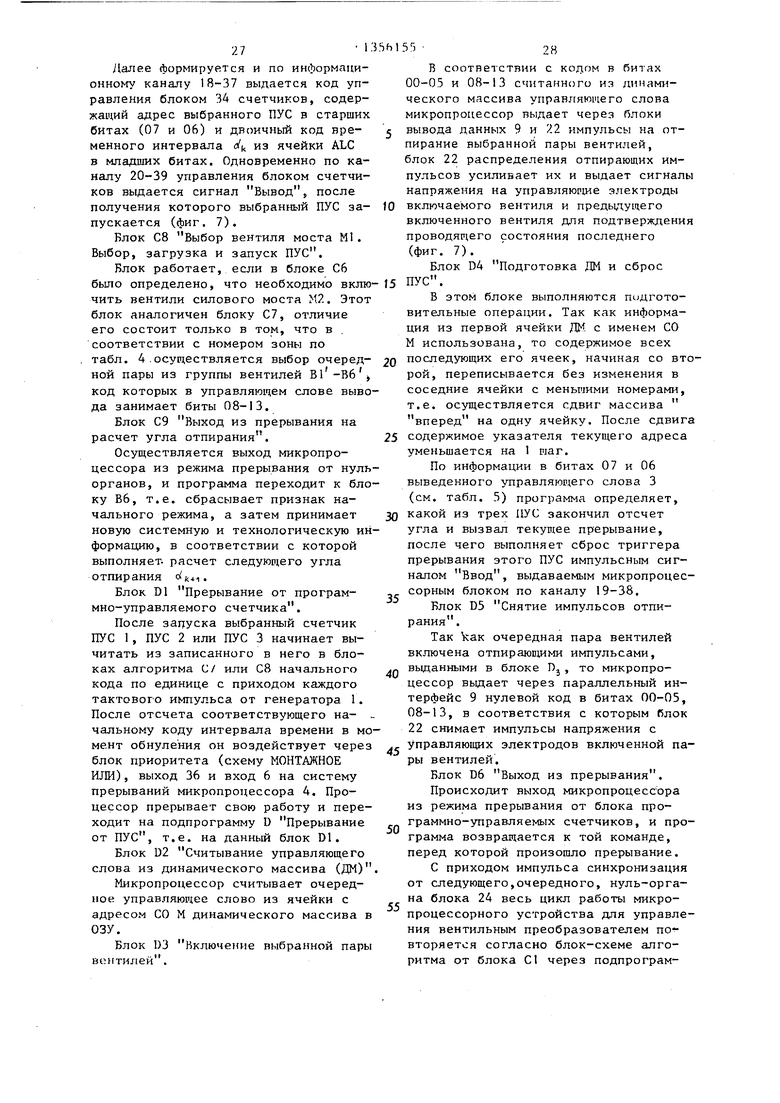

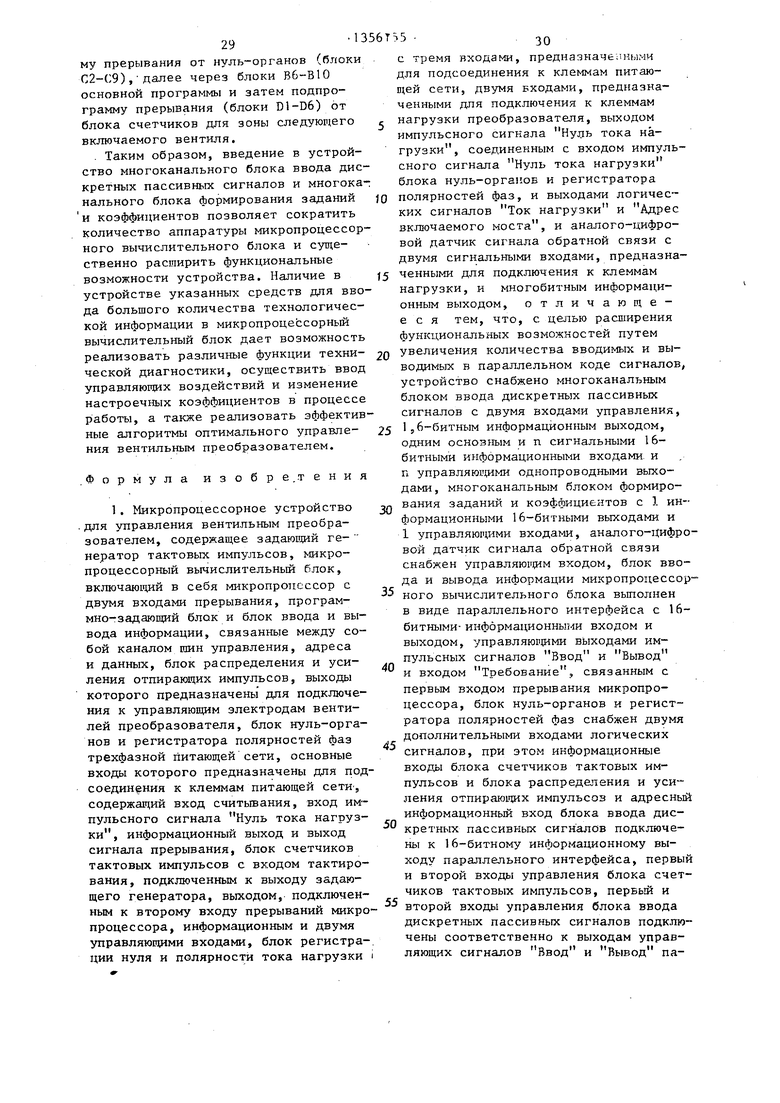

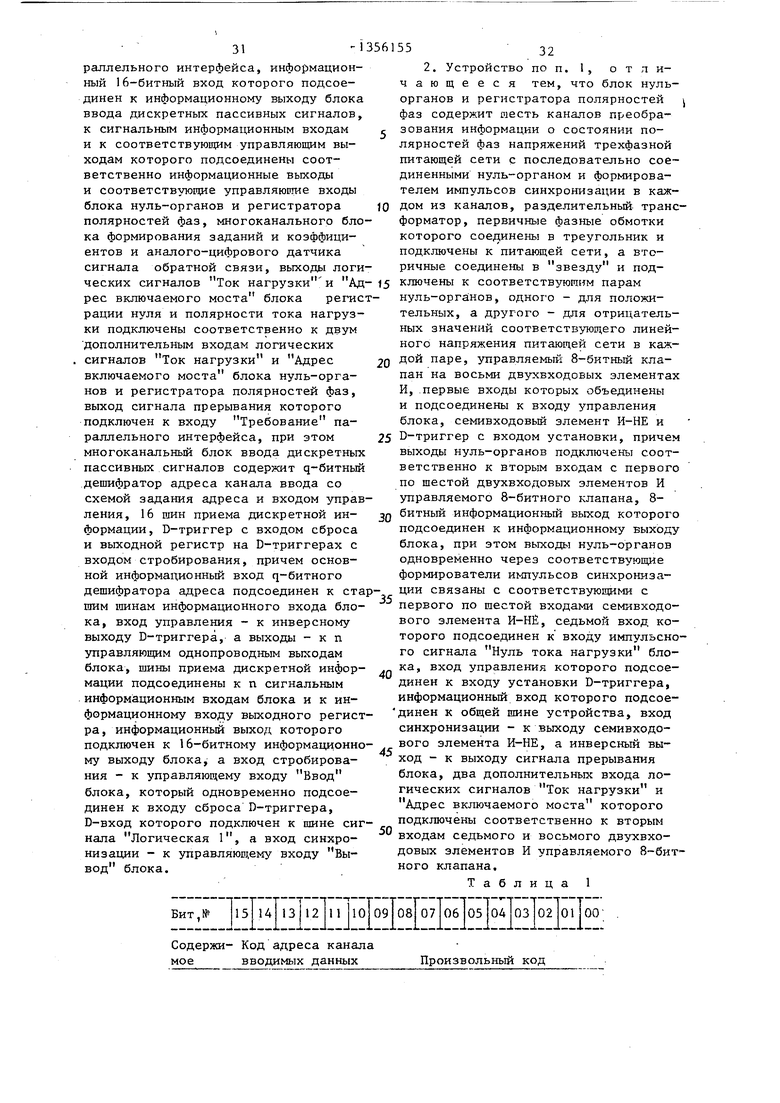

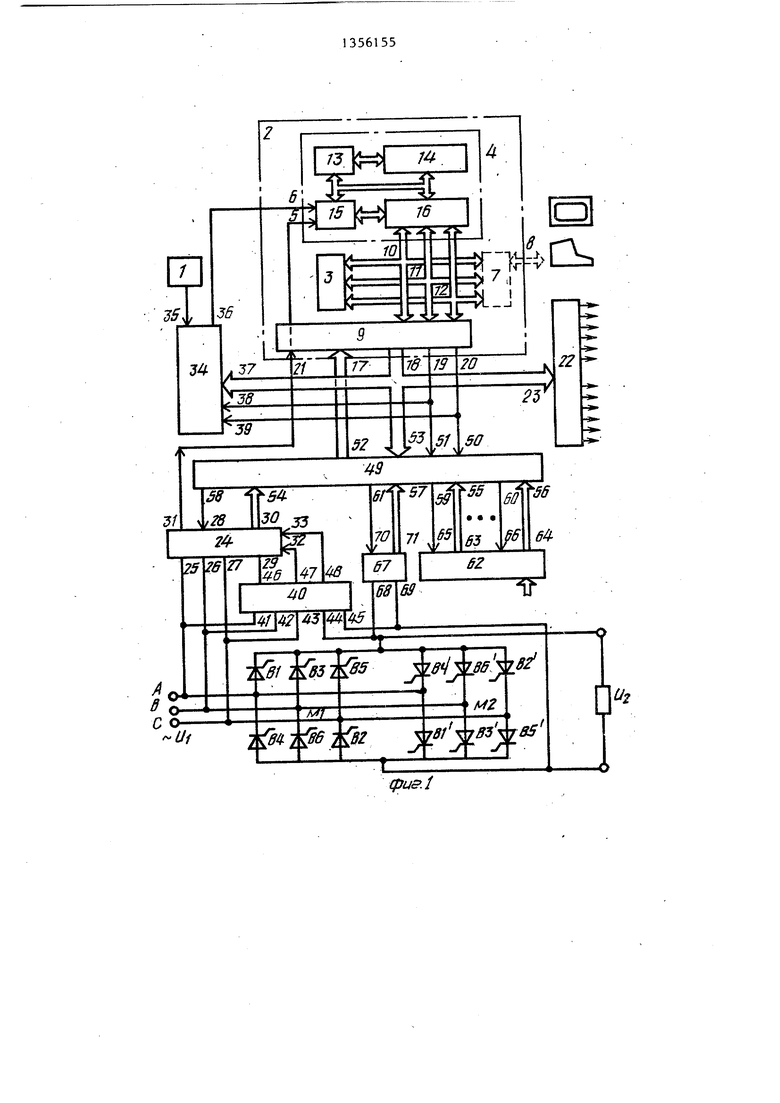

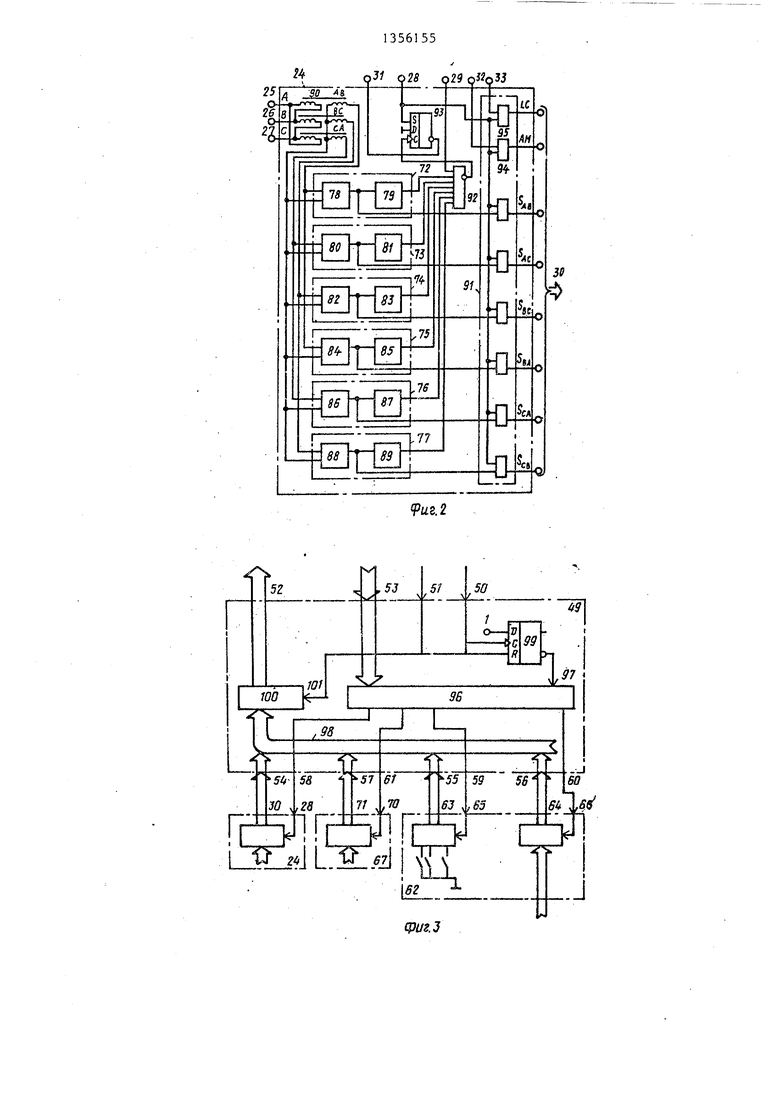

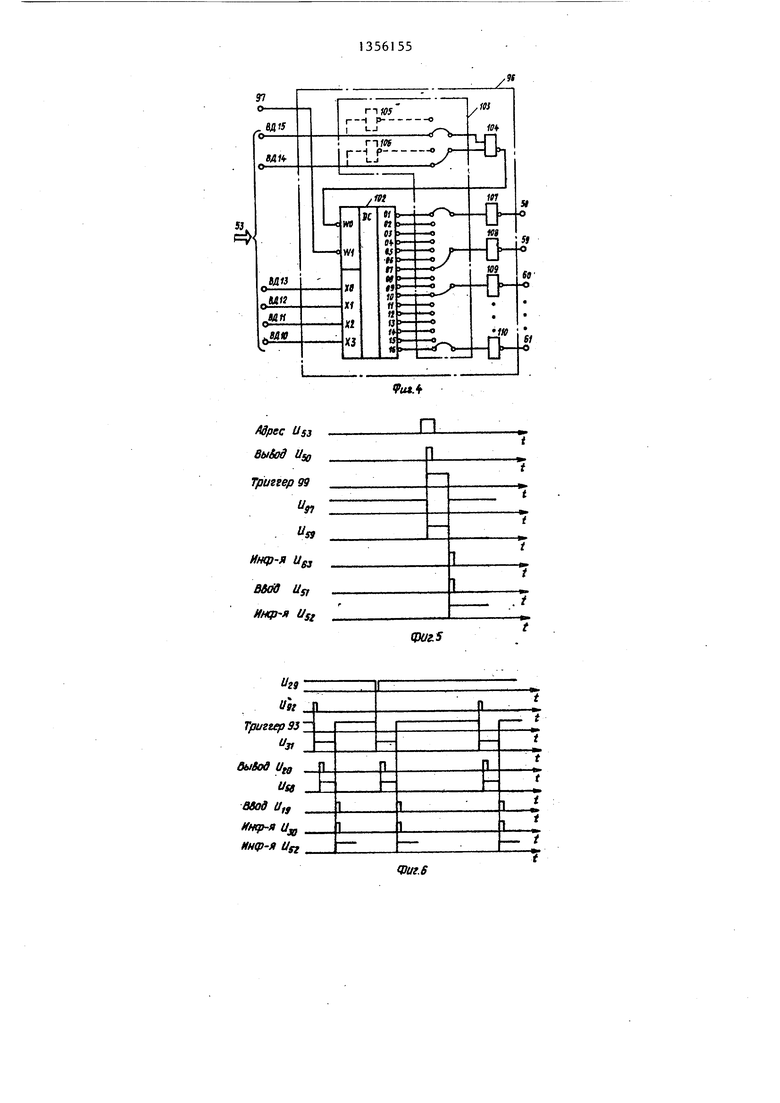

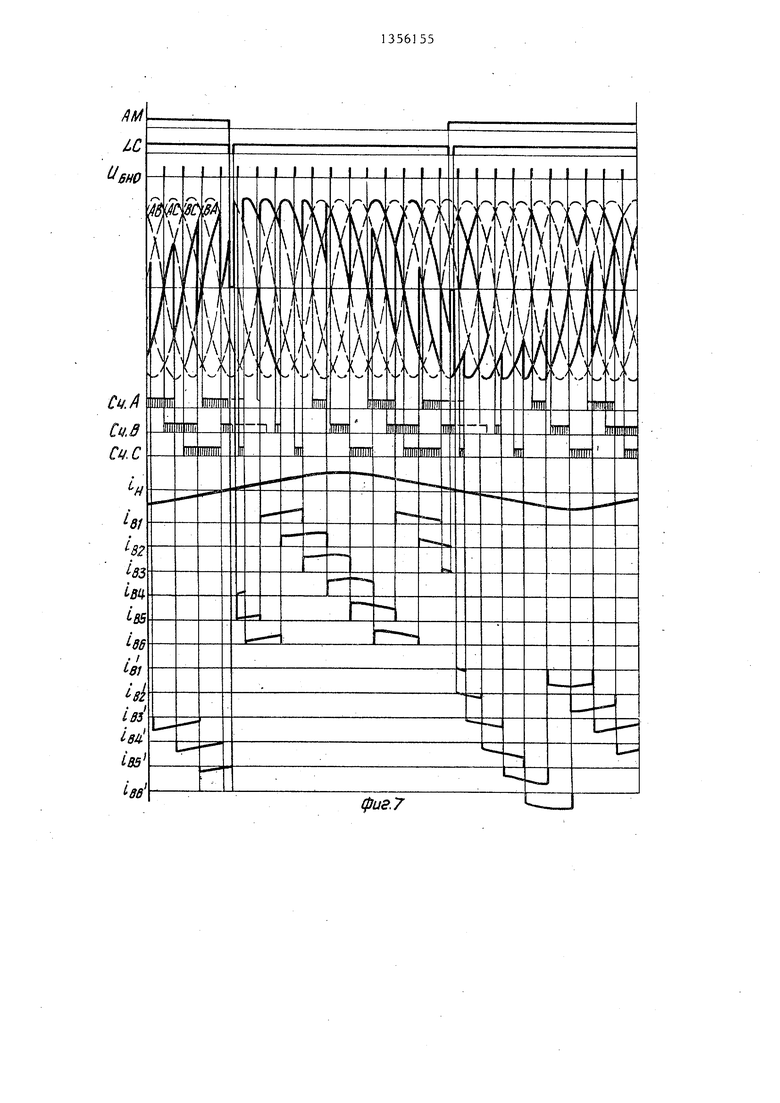

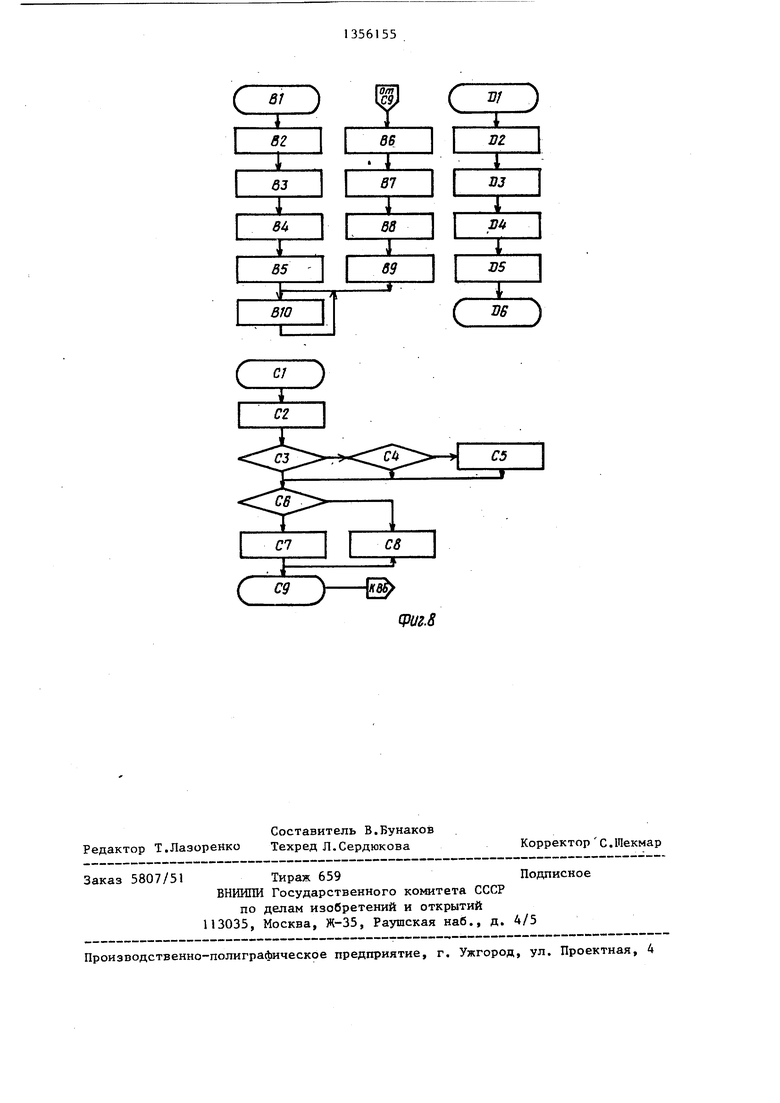

На фиг. 1 приведена функциональ- ная схема микропроцессорного устройства для управления вентильным преобразователем - циклоконвертером; на фиг. 2 - принципиальная схема блока нуль-органов и регистратора полярностей фаз; на фиг. 3 - функциональная .схема блока ввода пассивных дискретных сигналов; на фиг. 4 - принципиальная схема дешифратора канала вводимой информации; на фиг. 5 - временные диаграммы обмена сигналами блока ввода дискретных пассивных сигналов и параллельного интерфейса; на фиг. 6 - временные диаграммы обмен сигналами блока нуль-органов и регистратора полярностей фаз и параллельного интерфейса; на фиг. 7 - временные диаграммы напряжений и токов, поясняющие работу устройства; на фиг. 8 - структурные схемы алгоритмов основной части,управляющей программы и под прогр-амм обслуживания прерываний.

На фиг. 1-4 принятпы следующие обозначения: 1 - задающий генератор тактовых импульсов, 2 - микропроцессорный вычислительный блок (микрокомпью- тер, микроэвм), 3 - программно-задаю- 0ЩЙ блок оперативного запоминающего устройства и постоянного запоминающего устройства (ОЗУ и ПЗУ); 4 - микропроцессор; 5 - вход прерывания мик- ропроцессора от блока нуль-органов и регистратора полярностей фаз и блока регистрации нуля и полярности тока нагрузки; 6 - вход прерывания микропроцессора от блока счетчиков; 7 - блок управления устройствами ввода- вывода; 8 - канал связи с устройствами ввода-вывода; 9 - параллельный интерфейс; 10-12 - шины управления, адреса и данных соответственно; 13 - большая интег1 альная схема (БИС) регистрового арифметико - погического устройства; 14 - устройство управляющей памяти; ;15 - БИС управления вы

5

10

0

30

. 25 35

40 45 50 55

552

полнением операций; 16 - интерфейс связи микропроцессора с каналом гаин адреса, данных и управления; 17 - 16-битный информационный вход парал-i лельного интерфейса; 18 - 16-битный информационный выход параллельного интерфейса; 19 и 20 - управляющие выходы импульсных сигналов Ввод и Вывод параллельного интерфейса соответственно; 21 - вход Требование параллельного интерфейса; 22 - блок распределения и усиления отпирающих импульсов; 23 - информационный вход блока распределения и усиления отпираюпл 1х импульсов, 24 - блок нуль-органов и регистратора полярностей фаз; 25-27 - основные входы блока 24; 28 - вход считывания блока 24; 29 - вход импульсного сигнала Нуль тока нагрузки блока 24 (сигнал Z1); 30 - информационный вькод блока 24; 31 - выход сигнала прерывания блока 24; 32 и 33 - дополнительные входы логических сигналов Адрес включаемого моста и Ток нагрузки соответственно блока 24; 34 - блок счетчиков тактовых импульсов; 35 - вход тактирования блока счетчиков; 36 - выход блока счетчиков; 37 - информационный вход блока счетчиков; 38 и 39 - входы управления блока счетчиков; 40 - блок регистрации нуля и полярности тока нагрузки; 41- 43 - сетевые входы блока 40; 44 и

45- нагрузочные входы блока 40;

46- выход импульсного сигнала Z1 Нуль тока нагрузки, 47 - выход логического сигнала LC Адрес включаемого моста, 48 - выход логического сигнала AM Ток нагрузки, 49 - блок ввода дискретных пассивных сигналов; 50 и 51 - входы управления блока 49; 52 - информационный выход блока 49; 53 - адресный информационный вход блока 49; 54-57 - сигнальные информационные, входы блока 49; 58-61 - однопроводные управляющие выходы блока 49; 62 - блок формирования заданий и коэффициентов; 63

и 64 - информационные выходы блока 62; 65 и 66 - однопроводные управляющие входы блока 62; 67 - аналого- цифровой датчик сигнала.обратной связи с гальванической развязкой; 68 и

69- аналоговые входы датчика 67;

70и 71 - вход управления и многобитный информационный выход датчика 67 соответственно; 72-77 - каналы преобразования информации о состоя

НИИ полярн(5стей фаз напряжений трехфазной питающей сети; 78, 80, 82, 84, 86, 88 - нуль-органы; 79, 81, 83, 85, 87, 89 - формирователи импульсов синхронизации; 90 - трехфазный разделительный трансформатор; 91 - управляемый клапан передачи информации; . 92 - семивходовый логический элемент И-НЕ; 93 - D-триггер с установочным входом; 94 и 95 - двухвходовые логические элементы И; 96 - q-битный дешифратор адреса канала вводимой информации; 97 - вход управления q-битного дешифратора 96; 98-16 шин приема дискретной ин- . формации; 99 - D-триггер с входом сброса; 100 - выходной регистр на D-триггерах; 101 - вход стробирова- ния выходного регистра; 102 - микросхема стробируемого дешифратора на 16 направлений; 103 - узел задания адресов; 104 - двухвходовый логический элемент И; 105-110 - логические инверторы.

На фиг. 5-8 обозначено:

AM - логический сигнал Адрес включаемого моста ;

LC - логический сигнал Ток нагрузки ;

и...,-- импульсы синхронизации блоb к о

ка нуль-органов (БНО) и регистратора полярностей фаз (РПФ);

иАвИ лсП ьс.ВА сАИ- сй линейные напряжения трехфазной питающей сети;

Uj - выходное напряжение вентильного преобразователя;

сч.А, сч.В, сч.С - счетчики А, В, С блока счетчиков тактовых импульсов

ТОКИ вентилей моста Ml;

токи вентилей моста М2. Устройство предназначено для цифрового микропроцессорного управления вентильным преобразователем частоты циклоконвертером. Силовая часть цик- локонвертера (фиг. 1) содержит два гаестивентильных моста (комплекта) Ml и М2, включенных встречно-параллельн нагрузке через защитные токоограничи вающие реакторы. Циклоконвертер питает в общем случае активно-индуктивну с противоЭДС нагрузку, преобразуя энергию трехфазной сети переменного напряжения U, с частотой f с напряжние j с частотой f J. Управляющие электроды вентилей (тиристоров) присоединены к соответствующим выходам блока распределения отпирающих импульсов устройства.

o

5

0

5

.0

5

5

0

Устройство содержит задающий генератор 1 тактовых импульсов, микропроцессорный вычислительный блок 2, включающий в себя программно-задаю-- рщй блок 3, микропроцессор 4 с двумя входами 5 и 6 прерывания, блок 7 управления внешними устройствами ввода-вывода информации, связанный с последними через канал 8 связи, и параллельный интерфейс 9, связанные между собой шинами 10 управления, шинами 11 адреса и шинами 12 данных,

Микропроцессорный вычислительный блок 2 представляет собой программируемое, управляющее в реальном масштабе времени специализированное вычислительное устройство. В качестве такого вычислительного блока может быть также использована миниатюрная вычислительная машина (микроЭВМ, микрокомпьютер), выполненная на основе какого-либо конкретного микропроцессорного набора.

Микропроцессоры и микроЭВМ, опе- рируюпще 16-битными словами (2 байта) , являются достаточно экономичными по аппаратурным затратам и обеспечивают достаточно высокую точность управления.

Программно-задаювщй блок 3 представляет собой сочетание постоянного (или перепрограммируемого) запоминающего устройства (ПЗУ) и оперативного запоминающего устройства (ОЗУ) и служит для хранения программы работы, констант и переменных данных, получаемых от внешних устройств и в результате вычислений.

Микропроцессор 4 (например, типа К581) состоит из стандартных узлов: БИС регистрового арифметико-логического устройства 13, устройства 14 управляющей памяти, БИС 15 управления выполнением операций и интерфейса 16 соглас тощего устройства для связи микропроцессора с каналом шин адреса, данных и управления. В состав БИС 15 управления выполнением операций входит система прерываний микропроцессора, которая имеет два входа 5 и 6 в виде отдельных шин. Работа основной программы устройства может быть прервана либо от воздействия блока 24 (от нуль-органов) по входу 5,либо от блока 34 программно-управляемых счетчиков по входу 6. При этом микропроцессор переходит на соответствующую подпрограмму обслуживания прерывания .

51

Параллельный интерфейс 9 имеет . I 6-битные информационные вход 1 7 и выход 18, управляющие выходы импульсных сигналов Ввод 19 и Вывод 20 и вход Требование 21, связанный с первым входом 5 прерывания микропрс- це.ссора 4..

Устройство также содержит блок 22 распределения и усиления отпирающих импульсов, выходы которого предназ- начены .для подключения к управляю- пщм электродам вентилей В1...В6 и Bl ....B6 преобразователя, а информационный вход 23 подсоединен к информационному выходу 18 параллель- ного интерфейса 9, блок 24 нуль- орга нов и регистратора полярностей фаз трехфазной питающей сети, основные входы 25-27 которого подсоединены к клеммам питающей сети, содержащий . вход 28 считывания, вход 29 импульсного сигнала,Нуль тока нагрузки, информационный 30 и импульсный 31 выходы, и два.дополнительных.входа 32 и 33 логических сигналов. Кроме того, устройство содержит блок 34 счетчиков тактовых импульсов с входом 35 тактирования, подключенным к выходу задающего генератора 1s импульсным выходом 36, подключенным к .второму входу 6 прерывания микропроцессора 4, информационным 37 и двумя управляющими входами 38 и 39 и блок 40 регистрации нуля и полярности тока нагрузки с тремя входами 41-43, подсоединенными к клеммам питающей сети, двумя входами 44 и 45, подключенными к клеммам нагрузки преобразователя, выходом 46 импульсного сигнала Нуль тока нагрузки, соединен- ным с входом 29 блока 24 нуль-органо и регистратора полярностей фаз, и выходами логических сигналов Ток нагрузки 48 и Адрес включаемого моста 47.

Для осуществления возможности вво да различных цифровых сигналов задания и обратной связи и ввода изменяемых настроечных коэффициентов устройство снабжено многоканальным блоком 49 ввода дискретных пассивных сигналов с двумя входами 50 и 51 управления, 16-битным информационным выходом 52, одним адресным 53 и п сигнальными 16-битными информационными входами 54-57, п управляющими однопроводными 58-61 выходами и многоканальным блоком 62 формирования заданий и коэффициентов с 1 информа

5 0 5 Q Q

5

5

0

536

ционными 16-битными выходами 63 и 64 и 1 управляющими входами 65 и 66 и аналого-цифровым датчиком 67 сигнала обратной связи с двумя однопроводны- ми сигнальными входами 68 и 69, управляющим входом 70 и многобитным информационным выходом 71.

Информационный вход 37 блока 34 счетчиков тактовых импульсов и адресный информационный вход 53 блока 49 ввода дискретных пассивных сигналов подключены к 16 -битному информационному выходу 18 параллельного интерфейса 9. Входы управления 38 и 39 блока 34 счетчиков и входы управления 51 и 50 блока 49 ввода дискретных сигналов подключены соответственно к выходам управляющих сигналов Ввод 19 и Вывод 20 параллельного интерфейса 9. Информационный 16-битный вход 17 последнего подсоединен к информационному выходу 52 блока 49 ввода дискретных пассивных сигналов.

Блок 49 ввода дискретных пассивных сигналов содержит п каналов ввода дискретной информации, передаваемой параллельным кодом. Число битов параллельного кода каждого из каналов определяется разрядностью информационного входа 17 параллельного интерфейса 9 и в рассматриваемом случае не должно превышать 16. Каждому каналу вводимой в блок 49 информации соответствует сигнальный информационный вход и однопроводный управляющий вьпсод блока 49, по которому передается формируемый блоком 49 строб приема информации на соответствующий информационный вход блока. Например, каналу информации, вводимой от блока 24 нуль-органов и регистратора полярностей фаз, соответствует информаци- онньш вход 54, подсоединенный к информационному вьпсоду 30 блока 24, и управляющий выход 58, подключенный к входу управления 28 блока 24.

Выходы логических сигналов Ток нагрузки 48 и Адрес включаемого моста 47 блока 40 регистрации нуля и полярности тока нагрузки подключены соответственно к двум дополнительным входам 33 и 32 блока 24 нуль-органов и регистратора полярностей фаз, импульсный выход 31 которого подключен к входу Требование 2 параллельного интерфейса 9.

Многоканальный блок 62 формирования заданий и коэффициентов содержит

713561

1 каналов формирования дискретных сигналов, передаваемых параллельным двоичным кодом. Число битов параллельного информационного кода каждого из каналов так же как и в блоках 9 и 49, не превьшшет 16. Каждому каналу блока 62 соответствует информационный выход, например 63(64), и однопроводный управляющий вход 65 (66), которые подсоединены к соот- Ю ветствующим информационному входу 55(56) и управляющему выходу 59(60) блока 49 ввода дискретных сигналов. Количество каналов блока 62 определяется суммарным числом сигналив, t5 формируемых в качестве заданий и уставок и числом настроечных коэффициентов программы, значения которых желательно изменять в процессе рабо- ты устройства без изменения програм- 20 мы, однако количество каналов не может превышать некоторого максимального числа.

Аналого-цифровой датчик 67 сигнала обратной связи подключен двумя 25 сигнальными входами 68 и 69 к источнику измеряемого сигнала в рассматриваемом случае к клеммам нагрузки преобразователя..

В рассматриваемом случае таким зо сигналом является, например, напряжение на нагрузке, т.е. датчик 67 предназначен для контроля и измерения напряжения на выходе вентильного преобразователя, В замкнутых контурах регулирования тока сигналом обратной связи может быть также ток нагрузки, в этом случае входы 68 и 69 датчика 67 могут быть подключены к измерительным клеммам шунта, включен- .,. ного последовательно с нагрузкой. Вход 70 управления датчика 67 подключен к управляющему выходу 61 , а ий- формационный многобитный выход 71 - к информационному входу 57 со,ответ- ствующего канала блока 49 ввода дискретных пассивных сигналов.

Блок 24 нуль-органов и регистратора полярностей фаз содержит в своем составе (фиг, 2) разделительный согласуюсдай трансформатор 90, шесть каналов 72-77 преобразования информации о состоянии полярностей фаз напряжений питающей сети с последовательно соединенными нуль-органом (78) и формирователем импульсов синхронизации (79) в каждом из каналов (72), управляемый 8-битный клапан 91 на восьми логических элемен45

50

55

,.

5

0

5

55 8

тах 2И с 8-битными информационными входом и выходом 30 и входом управления, семивходовый логический элемент 7И-НЕ 92, D-триггер 93 с установочным входом. Первичные обмотки фаз разделительного трансформатора 90 соединены в стандартную схему треугольника и подключены к трехфазной питающей сети, а вторичные соединетч в звезду и подключены к входным зажимам нуль-органов. Из шести нуль-органов блока 24 три, принадлежащие каналам с номерами 72, 74, 76, регистрируют переход питающих линейных напряжений от отрицательных значений к положительным, а остальные три, принадлежас 51е каналам с номерами 73, 75, 77 - от положительных значений к отрицательным. Выходы нуль-органов связаны через, транзисторные формирователи импульсов -с соответствующими шестью входами семивходового логического элемента 92, осупдаствляющего логику 7И-НЕ. Седьмой вход этого зле- мента подсоединен к второму импульсному входу 29 блока 24, по которому приходит импульсный сигнал Z Нуль тока нагрузки, вырабатываемый блоком 40, Первый импульсный вход 28 (вход считывания) блока 24, по которому передается сигнал Ввод от параллельного интерфейса, связан с S-входом (входом установки) D-триггера 93, D-вход (информационный вход) которого подсоединен к общей шине устройства, вход синхронизации (С-вход) - к выходу семивходового элемента И-НЕ 92, а инверсньй выход - к импульсному выходу 31 блока 24, При этом шесть нуль-органов, 78, 80, 82, 84, 86, 88 образуют 6-битный регистратор полярностей фаз трехфазной питаюшей сети, выходы которого подсоединены к информационному входу управляемого клапана 91, Клапан 91 выполнен на восьми двухвходовых логических элементах И, первые входы которых объединены и подключены к первому импульсному входу 28 блока 24 (вход стробирова- ния сигналом Ввод). Вторые входы шести двухвходовых элементов И клапана 91 подсоединены к выходам нуль- органов 78, 80, 82, 84, 86, 88, втo рые входы двухвходовых элементов И 95 и 94 соединены соответственно с входами 33 и 32 блока 2А, передающими соответственно логические сигналы LC .Ток нагрузки и AM Адрес включаемого моста, формируемые блоком

40 регистрации куля и полярности то- ка нагрузки. Выходы двухвходовых логических элементов клапана 91 образу-. ют 8-битный инф армационный выход клапана 91, который подсоединен к j информационному выходу 30 блока 24. . Блок 49 ввода дискретных пассивных сигналов служит для ввода в микропроцессорный вычислительный блок дискретной информации в параллельном 10 двоичном коде от различных дискретных устройств и имеет в общем случае несколько каналов ввода, задаваемых их адресами. Блок 49 содержит q-битный дешифратор 96 адреса канала ввода |5 дешифратора 96 адреса канала вводи- со схемой 103 задания адреса и входом мой информации.

направлений, оставшиеся два информа ционных входа блока 49 и дешифратор 96 связаны через узел 103 задания адресов и двухвходовый элемент И 10 с первым входом WO управления микросхемы 102 дешифратора, второй вхо W1 управления которой подсоединен к входу 97 управления q-битногс) дешиф ратора 96 адреса, т.е. к инверсному выходу D-триггера 99. Выходы микросхемы 102 дешифратора 96 связаны че рез узел 103 задания адресов и логи ческие инверторы 107-110 с соответствующими выходами 58-61 q-битного

97 управления, шина 98 приема дискретной информации, D-триггер 99 с входом сброса (R-вход) и выходной регистр 100, .например, на D-тригге- рах с.входом 101 стробирования. Информационный- вход q-битного. дешифратора адреса подсоединен к шинам информационного входа 53 блока 49, вход 97 управления - к инверсному выходу триггера 99, а выходы - к Р управляющим однопроводным выходам 58- 61 блока 49. 111ина 98 приема дискретной информации подсоединены к К сигнальным информационным входам 54-57 блока 49 и к информационному входу выходного регистра 100. -Количество шин 98 приема дискретной информации определяется разрядностью слова микУстройство для управления вентиль ным преобразователем работает следующим образом.

20 После включения электропитания и запуска программы программно-задающий блок 3 ОЗУ и ПЗУ микропроцессорного вычислительного блока 2 выполняет первоначальные сброс и установ25 ку всех внешних устройств и блоков, включает систему прерываний микропроцессора 4 и вырабатывает определе ный закон управления. Заданное значение выходной частоты fg кратнос

30 выходного напряжения U, например, в двоичном коде считывается микропро. цессором через параллельный интерфе 9, блок 49 ввода пассивных дискретных сигналов из блока 62 формироваропроцессорного вычислительного бло- 35 заданий и коэффициентов для ча40

ка 2 и параллельного интерфейса 9.

Информационный выход выходного клапана 100 подключен к 16-битному информационному выходу 52 блока 49, а вход 101 стробирования - к управляющему входу 51 (входу Ввод) блока 49. Одновременно управляющими вход 51 подсоединен к входу сброса (К-вхо- ду) D-триггера 99, D-вход которого подключен к шине сигнала Лог. 1, а вход синхронизации - к управляющему входу 50 (входу Вывод) блока 49.

q-Битный дешифратор 96 адреса многоканального блока 49 ввода пассивных дискретных сигналов содержит мик- Q росхему 102 стробируемого дешифратора на 16 направлений, например К155ИДЗ, узел 103 задания адресов, двухвходовый логический элемент И 104 и логические инверторы 105-НО. Если (фиг. 4), 4 информационных входа блока 49 и дешифратора 96 подключены к соответствующим входам микросхемы 102- дешифратора на 16

стоты f2 по каналу 63-55 для кратно ти выходного напряжения U по каналу 64-56, корректируется в.соответствии с сигналом обратной связи, вводи мым с выхода аналого-цифрового преобразователя 67 по каналу 71-57 согласно выработанному закону управления. Затем программой рассчитывается необходимая последовательность изме г нения во времени угла отпирания d вентилей циклоконвертера и первое значение угла с/ в двоичном коде подготавливается к вьщаче его на информационный вход соответствующего четчика тактовых импульсов блока 34 Задаюпщй генератор I вырабатывает тактовые импульсы стабильной частоты в диапазоне 1-10 МГц, количество которых, задаваемое программно с помо щью микропроцессорного вычислительного блока 2 и подсчитываемое специально, предназначенными для этого счетчиками, определяет с высокой точностью величину угла отпирания

дешифратора 96 адреса канала вводи- мой информации.

направлений, оставшиеся два информа- ционных входа блока 49 и дешифратора 96 связаны через узел 103 задания адресов и двухвходовый элемент И 104 с первым входом WO управления микросхемы 102 дешифратора, второй вход W1 управления которой подсоединен к входу 97 управления q-битногс) дешифратора 96 адреса, т.е. к инверсному выходу D-триггера 99. Выходы микросхемы 102 дешифратора 96 связаны через узел 103 задания адресов и логические инверторы 107-110 с соответствующими выходами 58-61 q-битного

Устройство для управления вентильным преобразователем работает следующим образом.

После включения электропитания и запуска программы программно-задающий блок 3 ОЗУ и ПЗУ микропроцессорного вычислительного блока 2 выполняет первоначальные сброс и установку всех внешних устройств и блоков, включает систему прерываний микророцессора 4 и вырабатывает определен-: ный закон управления. Заданное значение выходной частоты fg кратности

выходного напряжения U, например, в двоичном коде считывается микропро. цессором через параллельный интерфейс 9, блок 49 ввода пассивных дискретных сигналов из блока 62 формирова заданий и коэффициентов для ча

стоты f2 по каналу 63-55 для кратности выходного напряжения U по каналу 64-56, корректируется в.соответствии с сигналом обратной связи, вводимым с выхода аналого-цифрового преобразователя 67 по каналу 71-57 согласно выработанному закону управления. Затем программой рассчитывается необходимая последовательность изменения во времени угла отпирания d вентилей циклоконвертера и первое значение угла с/ в двоичном коде подготавливается к вьщаче его на информационный вход соответствующего четчика тактовых импульсов блока 34. Задаюпщй генератор I вырабатывает тактовые импульсы стабильной частоты в диапазоне 1-10 МГц, количество которых, задаваемое программно с помощью микропроцессорного вычислительного блока 2 и подсчитываемое специально, предназначенными для этого счетчиками, определяет с высокой точностью величину угла отпирания

11

каждого из вентилей пргобразо- вателя.

Блок 34 счетчиков тактовых импульсов содержит три двоичных программно управляемых счетчика (ПУС) тактовых импульсов и блок управления счетчиками. Счетчики могут загружаться двоичными кодами и управляться программно по шинам адреса 11, данных 12 и управления 10 через блок 9 па- раллельного интерфейса. Счетчики служат для отмеривания временных интервалов, соответствующих заданным или рассчитанным значениям угла отпирания d вентилей и ведут счет так- товых импульсов от задающего высокочастотного генератора 1 тактовых импульсов, выход которого связан со счетными входами счетчиков. Выходы счетчиков объединены по ИЛИ и образу- ют импульсньй выход блока 34, который подсоединен к входу 6 прерываний микропроцессора 4 дпя запуска программы обслуживания прерываний вычислительного блока 2 от счетчиков так- товых импульсов.

Блок 22 служит для окончательного формирования, усиления и распределения отпираюгцгх импульсов по вентилям мостов Ml и М2 преобразовате- ля.

Блок 7 управления устройствами ввода-вывода информации и соответствующий канал связи 8 показаны на фиг. 1 пунктиром, так как их наличие не требуется для нормального функционирования устройства.Средства ввода- вывода информации (.например, считыватель с перфоленты, печатающее устройство, дисплей, перфоратор и т.п.) необходимы только для отладки эксплзг атационно-техническим персоналом программных и аппаратнь1х блоков предлагаемого устройства; они подключаются к нему через канал связи 8 и блок 7 только на этапе наладки.

Обмен данными и сигналами управления между микропроцессорным вычислительным блоком 2 и блоками 22, 24, 34, 40, 49, 62, 67, осуществляюпвими сопряжение с силовой частью вентильного преобразователя, осуществляется через параллельный интерфейс 9.

Интерфейс 9 способен хранить 16 битов одного выходного слова в реги- стре выходной буфер. Записанные в выходной буфер данные (BDOO-BD15) передаются во внешние блоки 22, 24, 34, 49 посредством кабеля связи.

j 10 )5 у- 20 с25

зо

е ,, -) Q зг- ок jc ;

, „ - „ )

35615512

присоединяемого к специальному разъему. Любая программная операция микропроцессора 4, которая загружает байт или слово в выходной буфер, вызывает появление кратковременного строб-сигнала Вывод высокого уровня, информирующего внешние блоки о появлен ии данЩ)1Х на выходе.

Входные данные ББОО-ВВ15 пересылаются в канаш микроЭВМ 2 в течение канального цикла Ввод. Все 16 битов помещаются в канал 12 с входа 17 одновременно. Когда данные считаются микропроцессором 4, последний инициирует канальный цикл Ввод, который формирует на выходе Ввод 19 параллельного интерфейса 9 кратковременный строб-сигнал Ввод высокого уровня длительностью 10-300 мкс, ин- формируюрщй внешние блоки о приеме данных микропроцессором.

Вход Требование 21 параллельного интерфейса используется внешниг-ш блоками для инициирования процедуры прерывания или как флаг, состояние которого может быть проверено программно. Канальный сигнал Требование прерывания низкого уровня на входе 5 микропроцессора 4 вырабатывается параллельным интерфейсом 9 при наличии сигнала Требование на входе 21 высокого уровня напряжения со стороны блока 24 при наличии разрешения прерывания программы.

Каждому каналу вводимой в микропроцессорный блок 2 или выводимой из него информации поставлен в соответствие свой определенный системный адрес, который может устанавливаться путем замыкания или размыкания проводников-перемычек в специальном узле задания адреса, имеющемся в составе любого из блоков 22, 34, 49. При обращении к определенном каналу параллельный интерфейс 9 удерживает на своих шинах q старших битов информационного выхода 18 адрес этого канала до тех пор, пока процессор 4 не закончит с ним сеанс связи. В связи с этим блок 49 ввода пассивных дискретных сигналов подсоединен своим информационным входом 53 именно к шинам q старших битов информационного выхода 18 блока 9, по которым передается а,црес канала вводимой информации на q-битный дешифратор 96 блока 49. Количество разрядов q 16-битного информационного слова, отводимых под код адреса каналов зависит в устройстве от общего количества каналов передаваемой информации и разрядности имеющихся в устройстве аналого-цифровых (и цифро- аналоговых, если они есть) преобразователей. Например, если аналого- цифровой преобразователь блока 67 имеет 10 битов, то целесообразно отвести под адрес оставшиеся 6 битов 16-битного информационного слова микропроцессорного блока 2, т.е. . Формат выводимого микропроцессором слова данных для случая .указан в табл. 1.

Как видно из табл. 1, системный адрес считываемого канала помещается в 6 старших битах выводимого блоком 2 слова , при этом в 10 младших битах код может быть произвольным. Путем перестановки проводников-перемычек в узле 103 задания адресов дешифратора 96 блока 49 ввода дискретных пассивных сигналов можно задавать различные адреса каналов вводимой.информации.

Последовательность обмена сигналами между микропроцессорным вычислительным блоком 2 и блоками 24, 34, 49, 62 и 67 рассмотрим на примере . ввода кода заданной выходной частоты fj преобразователя с блока 62 формирования заданий и коэффициентов. В этом случае обмен начинается с того, что микропроигессор выдает на выход 18 интерфейса 9 код адреса канала 63-55 задания выходной частоты.f.., который поступает на вход 53 блока 49 ввода дискретных пассивных сигналов и далее на дешифратор 96 адреса (фиг. 5), Одновременно с выдачей адреса блок 2 вырабатывает на своем выходе 20 строб-сигнал Вывод, который поступает на управляющий вход 50 блока 49 и далее на С-вход триггера 99. Так как 1)-вход триггера всегда имеет потенциал 1, то по строб-сигналу Вывод триггер 99 устанавливается и на его инверсном выходе появляется низкий уровень напряжения,Если вьщанньш процессором адрес соответствует адресу выбранного канала заданной частоты f2, то срабатывает узел задания адреса 103, элемент 2И-НЕ 104, низкий уровень с выхода которого поступает на вход WO микросхемы 102 дещифратора 96 и разрешает работу последней. При появлении низкого , уровня напряжения на выходе триггера 99э который поступает на вход W1

микросхемы 102 дешифратора, последняя включается и на одном из ее выходов, например на выходе 07, соответствующем коду адреса канала задания выходной частоты .f, появляется низкий уровень напряжения. Этот уровень, инвертируясь на согласующем элементе НЕ 108, преобразуется в высокий уровень напряжения, который с выхода 59

блока 49 поступает на вход 65 блока . 62 формирования заданий и коэффициентов и стробирует в последнем клапан передачи информационного слова задания выходной частоты преобразователя. В результате с выхода 63 блока 62 код заданной частоты поступает на сигнальный информационный вход 55 блока 49 ввода дискретных пассивных сигналов, и далее на шины 98 приема

дискретной информации. Затем микропроцессор 4 вырабатывает сигнал управления Ввод (фиг. 5), который с управляющего выхода 19 параллельного интерфейса 9 поступает на вход

0

5

0

5 51 управления блока 49 и далее на вход 101 клапана передачи информации и одновременно на R-вход триггера 99. Высокий уровень напряжения на входе 101 клапана 100 разрешает прохождение информации о коде заданной выходной частоты с приемных шин 98 на выход 52 блока 49 и далее на вход 17 параллельного интерфейса 9. Одновременно строб-сигнал Ввод по R- входу сбрасывает триггер 99, высокий уровень напряжения с инверсного выхода которого запрещает работу микросхемы 102 дешифратора 96, в результате чего на всех управляющих выходах последнего устанавливается низкий уровень напряжения.

Прием данных по всем другим каналам ввода дискретных пассивных сигналов, например каналу 64-56 о значении кратности выходного напряжения, каналам 30-54 и 71-57 о параметрах технологической информации и т.д., осуществляется аналогично вьш1еописан- ному. Значения различных постоянных, но изменяемых по желанию оператора коэффициентов, входящих в блоки алгоритма, вводятся от блока 62 также че- рез блок 49 ввода дискретных пассивных сигналов, который в рассматриваемом примере рассчитан на 16 каналов

ввода. Значения параметров системной информации и изменяемых коэффициентов в любой момент времени могут быть изменены оператором с помо5

0

5

15 3

щью программных переключателей, имеющихся в блоке 62 формирования заданий и коэффициентов. Поэтому для каждого изменяемого параметра и коэффициента в блоке 62 предусмотрен свой узел задания в виде набора переключателей и клапан (или регистр) передачи данных с входом управления, подключенным к соответствующему выходу дешифратора 96, аналогично тому, как это выполнено для узла задания кода выходной частоты. Некоторые параметры могут формироваться вне устройства, например в ЭВМ более высокого уровня, и вводиться по внешнему ка- налу ввода аналогично каналу 64-56,

При дальнейшем изложении используется понятие зоны сетевого напряжения для К-го вентиля моста. Распознавание текущего номера зоны осуществляется с помощью блока 24 нуль- органов и регистратора полярностей фаз трехфазной питающей сети. В двух- мостовом преобразователе зона сетевого напряжения идентифицируется относительно вентилей моста М1 который принимается за основной или ве- . Работа устройства поясняется временными диаграммами, приведенными на фиг. 7.

Микропроцессорньш модуль 2 работает в течение всего времени функционирования предлагаемого устройства для управления вентильным преобразователем с момента включения его электропитания по программе, хранящемся в его запоминающем устройстве 3, в соответствии с алгоритмом, приведенном на фиг. 8.

Программа работает циклически, по тактам, начало каждого такта соответствует переднему фронту импульса синхронизации (фиг. 6, и ). Каждая зона сетевого напряжения соответствует одному такту управления (интервалу синхронизации), в котором производится расчет значения угла отпирания о и,, определение и вьщача соответствующего выходного кода на отпирание вентилей. Импульсами синхронизации, приходящими от нуль-органов блока 24 осуществляется прерывание основной программы щесть раз за период. В каждом такте микропроцессор считывает системную информацию, например, по каналсям 63-55 и 64-56, т.е. величины f. 2y. tc и технологическую, т.е. информацию от блоков 24, 40, 67, со5516

держащих регистраторы и датчики контролируемых величин и параметров. В любой момент времени на шести

входах клапана

имеется информация

5

0

5

и

5

0

5

0

5

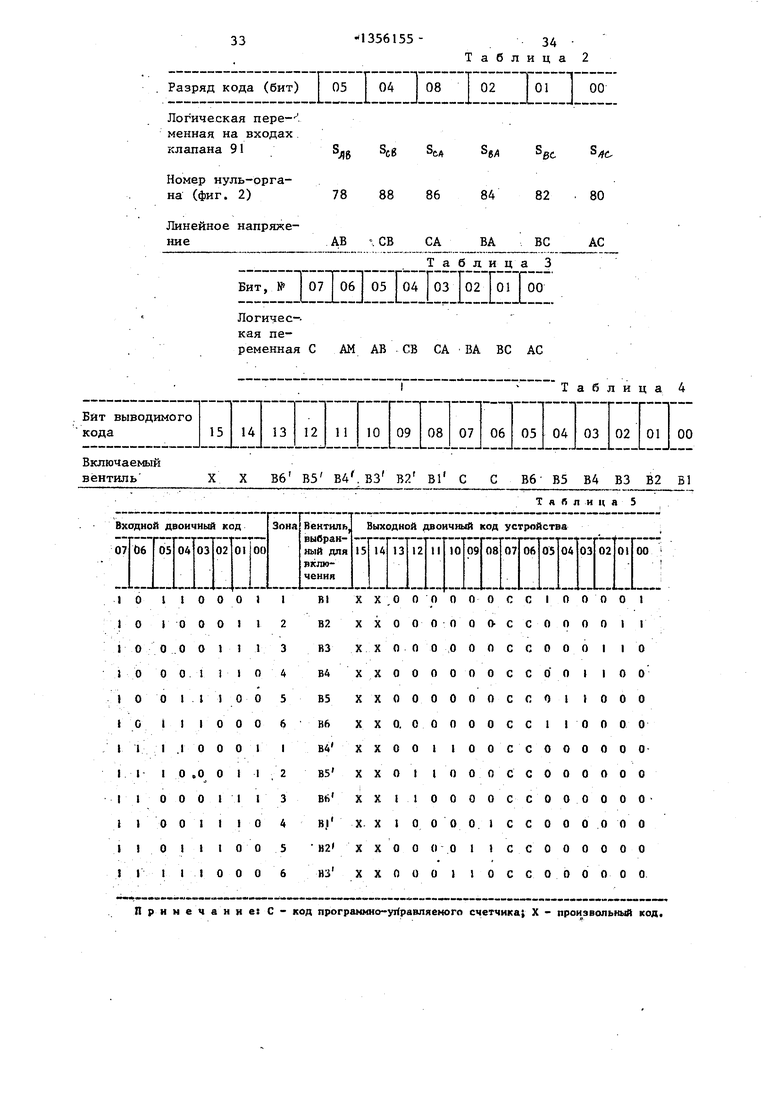

о текущем состоянии полярностей фаз линейных напряжений, образующих 6- битный параллельный код. Разрядам этого кода соответствуют нуль-органы и линейные напряжения, указанные в табл. 2.

Вырабатываемые блоком 40 регистрации нуля и полярности тока нагрузки логические сигналы AM и LC передаются по соответствующим шинам с выходов 47 и 48 на входь: 32 и 33 соответственно блока 24 нуль-органов и регистратора полярностей фая ;а информационные входы логических элементов 94 и 95 соответственно клапана 91 (биты 06 и 07). Эти сигналы вместе с сигналами о-состоянии полярностей фаз, поступающими с выхода РПФ блока 24, образуют байт входной тех«- нологической информации устройства, который имеет формат, указанный в табл. 3.

Байт входной технологической ин- формации считывается микропроцессором 8-битным параллельным кодом по каналу 30-54 через блок ввода пассивных дискретных сигналов и затем по каналу 52-17 через параллельный интерфейс 9 путем подачи кратковременного сигнала Лог. 1 (строба Ввод) на управляющий вход 28 блока 24 и клапана 91.

Микропроцессорный вычислительный блок 2 связан через параллельный интерфейс 9 с управляюи;ими электродами вентилей силовых мостов через формирователи блока 22 распределения отпирающих импульсов таким образом, что каждому разряду (биту) выводимого слова информации соответствует определенный вентиль моста. Соответствие битов кода, вьщаваемого микропроцессорным блоком 2 через канал 18-23 и блок 22, управляемым вентилям мостов устанавливается табл« 4, определяющей формат выводимого управляюЕдаго слова. В табл. 4 и 5 знаком (Х) отмечены неиспользуемые биты стандартно- го 16-битного управляющего слова. Знаком (С) обозначены биты, отведенные под код адреса программно-управляемых счетчиков блоха 24.

При условии протекания тока по нагрузке () в интервале каж,аой из зон сетевого напряжения может быть

17

произведено включение только одного, очередного, вентиля моста, при этом предыдущий вентиль продолжает проводить ток, а вентиль, предшествующий предыдущему, выходит из состояния проводимости (при небольших нагрузках) В табл. 5 указано, в зависимости от номера проводящего моста и номера текущей зоны для какого вентиля устройство начинает отсчет угла отпи рання и какой будет выведен код на включение вентилей по окончании отсчета. В табл. 5 единичному состоя- нию бита выходного кода соответствует высокий уровень напряжения на управляющем электроде тиристора, нулевому состоянию - отсутствие напряжения.

Выдавая в определенные моменты времени единичные коды через блоки 9 и 22 и затем снимая их, микропроцессор в последовательности, задаваемой программой, и в соответствии с входными воздействиями осуществляет включение выбранных вентилей, т.е. управление вентильным преобразователем.

Для управления тиристорным цикло,- конвертером могут быть применены разнообразные алгоритмы генерирования отпирающих вентили импульсов. Рассматриваем работу устройства при реализации одного из наиболее распространенных алгоритмов раздельного управления мостами, соответствующего синхронному многоканальному способу управления или методу абсолютных уг лов отпирания. Алгоритм обеспечивает снятие отпирающих импульсов с моста, закончившего проводить ток, и подачу импульсов через некоторый интервал задержки (паузы) на мост, вступающий в работу, при линейном законе изменения углов отпирания вентилей в течение полупериода выходно- го напряжения гщклоконвертера (треугольный закоц).

На текущем К-м интервале синхронизации осутдествляется вычисление значения угла отпирания дпя следующего (К+1)-го интервала синхронизации. Вычисление выполняется по формуле

(с+1 . D,(1)

где 0/1(4,- значение угла отпирания

для следуюп|его интервала; о/1( - значение угла отпирания для текущего интервала;

jfO t518

/fd n - теку1цее приращение угла отпирания;

DH - разность текущего и предыдущего (К-1) значений угла отпирания:

(2) (3)

Из формулы (1) следует, что частота fj и напряжение Uj на выходе цик- локонвертера могут регулироваться и изменяться, начиная с любого интервала синхронизации путем дискретного изменения во времени приращения угла io/x, которое связано с f и Uj сле- дуюп(им образом:

4c;, C/3N ,-V,, (4)

где N 1 - теку1чее отношение частот

:на входе f и на выходе f циклоинвертора:

,; (5)

V| - текущее значение кратности регулирования выходного напряжения, т.е. отношение амплитудного значения выходного напряжения амплитудному значению входного

и.

1 л m

,,

Ч fj -I / m

(6)

30 40 5

,50

55

В (6) обычно . V.U.

Из формул (1) и (4) можно заключить , что при выбранном неизменном отношении преобразователя частоты N| изменение выходного напряжения осуществляется путем изменения угла отпирания е/ц в пределах от о/имкс дискретностью /1о. Величины макс определяются из условия безопасного инвертирования при индуктивных нагрузках циклоконвертера и равенства амплитуд гладкой составляющей в положительном и отрицательном полупериодах выходного напряжения.

Регулирование выходного напряжения осуществляется следующим образом Для заданной кратности регулирования V| вычисляют граничное нижнее значение угла отпирания

гр.4 V2(1-V j(7)

и граничное верхнее -значение vi.na отпирания

19

«/2(1+VJ

(8)

Чр.. в - ц

С которыми в каждом интервале синхронизации сравнивают текущее значение угла отпирания.

На каждом такте синхронизации осуществляют сравнение рассчитанного о ij, с одним из граничных значений угла.

Если имеет место режим уменьшения угла в( ,- т.е. , то сравнение /Kf, осуществляют со(гр.. В случае если выполнится неравенство

о(.

d .

Kft ГР. N 1

то изменяют начальные условия муле (1), принимают ,

of

VH повторяют в этом же интервале синхронизации вычисление с/., по формуле (1) с этими новыми начальными условиями.

Если имеет место режим увеличения

угла о, т.е. D О, то сравнение

осзш ествляют с d

Гр. 8

В случае

если выполнится неравенство

KV1 .e

(10)

то изменяют начальные условия в фор- ЗО Щ™ адресами, начиная с ячейки с именем CODM, адрес которой фиксирован и

муле (1), принимают ofrp.s и повторяют в этом же интервале синхронизации вычисление d по формуле (I) с этими новыми начальными условиями .

Важнейшим свойством двухмостово- го вентильного преобразователя является его способность осуществлять двухсторонний обмен энергией между питающей сетью и нагрузкой. Благода- . ря этому свойству легко обеспечивается работа циклоконвертера на нагрузку с любым коэффициентом мощности. Работа на нагрузку с низким . cos (f обеспечивается тем, что каждый из вентильных мостов (фиг. 1) может работать как в режиме выпрямления, так и в режиме инвертирования. При этом-в режиме выпрямления энергия передается из питающей сети через циклоконвертер в нагрузку, а в режиме инвертирования - от нагрузки через циклоконвертер в сеть. Микропроцессорное устройство управления позволяет осуществить все эти режимы за счет выбора соответствующего моста и выдачи отпирающих импульсов с соответствующими значениями угла d,

35

40

45

50

является адресом-идентификатором массива. Массив является динамическим, так как при записи в него очередного слова содержимое в ячейке указателя текущего адреса массива наращивается на 2 для байтовых микропроцессоров и на 1 для микропроцессоров, в которых идет адресация к 16-битному слову, при этом очередное управляющее слово записывается в следующую ячейку. Считывание управляющего слова с удалением из массива производится с другой стороны и только из верхней ячейки, адрес которой фиксирован, при этом оставшиеся слова массива сдвигаются в соседние ячейки с меньшими адресами. Таким образом, в используемом динамическом массиве порядок считывания подчиняется правилу: первым поступил - первым обслуживается.

Примем для определенности, что ff рассматриваемое управляющее устройство работает с разомкнутой обратной связью, а закон управления соответствует формированию на выходе переменного напряжения с параметрами N

г

10

2п

5615520

Как следует из фиг. 8, алгоритм функционирования устройства состоит из трех частейS которые соответствуют основной программе и двум подпрограммам прерывания. Основной программе соответствуют блоки В1-В10 блок-схемы алгоритма. Подпрограмме прерывания от .нуль-органов соответствуют блоки С1-С9, подпрограмме прет- рывания от программно-управляемых счетчиков (ПУС) - блоки D1-D6.

В программе, реализующей описываемый алгоритм управления, используется динамический массив управляющих слов, т.е. кодов, выводимьпс из микропроцессорного блока 2, состояние отдельных битов которых определяет включение тех или иных вентилей. Сформированные программой управляющие слова вывода записывают в заданный участок ОЗУ блока 3 в определенной последовательности, образуя динамический массив 16-битных слов, из которого в определенной последовательности эти слова извлекаются. Массив является упорядоченным, так как заполняется с одной стороны. При этом управляющие слова записываются в ячейки ОЗУ с последовательно возрастаю15

25

5

0

5

0

является адресом-идентификатором массива. Массив является динамическим, так как при записи в него очередного слова содержимое в ячейке указателя текущего адреса массива наращивается на 2 для байтовых микропроцессоров и на 1 для микропроцессоров, в которых идет адресация к 16-битному слову, при этом очередное управляющее слово записывается в следующую ячейку. Считывание управляющего слова с удалением из массива производится с другой стороны и только из верхней ячейки, адрес которой фиксирован, при этом оставшиеся слова массива сдвигаются в соседние ячейки с меньшими адресами. Таким образом, в используемом динамическом массиве порядок считывания подчиняется правилу: первым поступил - первым обслуживается.

Примем для определенности, что рассматриваемое управляющее устройство работает с разомкнутой обратной связью, а закон управления соответствует формированию на выходе переменного напряжения с параметрами N

21

1

4, f 7 f и V 1.

k ч 1 k

Нике приведено описание блоков алгоритма, соответствующее блок-схемам на фиг. 8,

Блок В1 Начало.

Этому блоку соответствует запуск основной части управляющей программы, например, путем подачи команды Пуск с клавиатуры дисплея. Блок В2 Инициализация.

Микропроцессорный вычислительный блок 2 выполняет первоначальные сброс, установку в исходное состояние всех внешних устройств и блоков и подготовку рабочих ячеек памяти, включает систему прерываний микропроцессора 4 и включает в нее блок 24 и 34, способные вызвать прерывания.

Блок ВЗ Установка признака на- чального режима.

В соответствующий бит ячейки памяти Слово состояния программы заносятся 1, что указывает, на.то, что идет начальн ый режим программы. Кро- ме того, устанавливается в нуль счетчик интервалов синхронизации, т.к. .

Блок В4 Прием системной информации .

Заданные начальные значения выходной частоты f и кратности выходного напряжения считываются блоком 2 через параллельный интерфейс 9 и блок 49 ввода дискретных пассивных сигналов по каналам 63-55 и 64-56 из блока.62 формирования заданий и коэффициентов .

Блок В5 Определение начального значения угла отпирания d.

Выполняется расчет начального значения угла отпирания ведущего моста Ml для следующего интервала синхронизации. Принимаются, например, следующие начальные условия: началь- нов значение угла dp равно значению нижней границы о/о (гр, .знак разности Dp положительный, т.е. 1)|,0. По формуле (5) определяется N, по формуле (4) вычисляется &s{, по формуле (7) рассчитывается .. Значение угла отпирания для следующего интервала синхронизации определяется по формуле (1)

о(,

Полученное значение угла умножается на масштабный коэффициент К пересчета угла в код временного интер-1356 5522

вала и результат записывается в ячейку ОЗУ текущего значения угла отпирания о имеющем CALP. Этот код далее в соответствии с алгоритмом будет вьщан на информационный вход одного из программно-управляемых счетчиков блока 34.

Блок В6 Сброс признака начального режима.

Этот блок и все последующие принадлежат циклически повторяющемуся участку программы в отличие от блоков В1...В5, характеризующих начальный ее участок. Чтобы отличить циклически повторяюищйся участок программы, признак начального режима в слов состояния программы сбрасывается.

Блок В7 Прием системной информации .

Этот блок идентичен блоку ВЗ, отличие заключается только в том, что микропроцессором считываются текупще заданные значения выходной частоты f и кратности выходного, напряжения Vj,, которые могут быть изменены оператором в любой момент времени с помощью цифровых задатчиков блока 62 формирования заданий и коэффициентов

Блок В8 Прием технологической информации.

В этом блоке считываются значения сигналов обратной связи от датчиков различных технологических параметров которых в общем случае может быть несколько. В рассматриваемом случае таким параметром является фактическо значение выходного напряжения (среднее или действующее значения), преобразуемое из аналоговой величины в параллельный двоичный код аналого-цифровым преобразователем датчика 67. Сформированный датчиком 67 код вводится по каналу 71-57 через блок 49 ввода пассивньк дискретных сигналов и далее по каналу 52-17 через параллельный интерфейс 9 в микропроцессорный вычислительный блок 2.

Блок В9 Расчет следующего значения угла отпирания.

По принятым текущим значениям fjK и V определяют по формулам (5), (6) (4) соответственно значения величин NK, и, /10/, после чего в соответствии с принятым законом регулирования рассчитывают по формуле (1) угбл отпирания ,, для следующего вентиля ведущего моста Ml. В рассматриваемом случае, так как .0, то ос расчет вмпплкяется ю

23

формуле (1). Затем полученное значение угла умножается на коэффициент К / пересчета угла в код временного интервала и результат помещается в ячейку CALP, этот код в дальнейшем выдается на информационные входы программно-управляемых счетчиков блока 34.

Блок В10 Ожидание прерывания.

Так как все расчетные и подготовительные операции выполнены, то дается команда разрешить прерывания микропроцессора 4 и затем вновь перейти к блоку В10, т.е. ожидать прерывания .

Блок С1 Прерывание от нуль-орга нов.

1

J5 пает с информационного выхода 30 блока 24 нуль-органов и РПФ на вход 54 блока 49 ввода дискретных пассивных сигналов, а затем с выхода 52 последнего на информационный вход 17 па2Q раллельного интерфейса 9. Одновременно импульс Ввод высокого уровня напряжения с входа 28 блока 24 нуль- органов и РПФ устанавливает D-триггер 93 по его S-входу (фиг. 6). Это при-

25 водит к появлению низкого уровня напряжения на инверсном выходе D-триг- гера 93 и, следовательно, на выходе 31 блока нуль-органов и . в резул тате восстановление низкого уровня н

При достижении каким-либо линейным напряжением питающей сети нулевого уровня (фиг. 7) блок 24 нуль- органов и РПФ вырабатывает узкий импульс на выходе одного из формирователей 79, 81, 83, 85, 87, 89, который инвертируется элементом И 92 и передним фронтом стробирует по С- входу D-триггер 93 (фиг. 6). Аналогичное действие оказывает импульс прерывания, сформированный блоком 40 на его выходе. 46 Z1 - Нуль тока нагрузки, этот импульс поступает на зо 1 Требование параллельного вход 29 блока 24 нуль-органов и РПФ интерфейса 9 и, следовательно, высои затем на вход семивходового элемента И 92, после которого инвертируется и поступает на С-вход D-триггера 93. Так как информационный вход (D- вход) триггера всегда имеет уровень О, то при стробировании по С-входу триггер 93 сбрасывается и на его инверсном выходе появляется уровень 1. Сигнал Лог. 1 поступает на вьпсод 31 блока 24 нуль-органов и РПФ затем на вход 21 Требование параллельного интерфейса 9 и затем низким уровнем на вход 5 (КТПР Н) микропроцессора 4. По этому сигналу начинается выполнение подпрограммы прерывания от нуль-органов.

Блок С2 Прием байта входной информации.

Микропроцессор 4, получив сигнал прерывания от нуль-органов, выставляет в соответствии с программой на выходе 18 параллельного интерфейса 9 адрес блока 24 нуль-органов и РПФ и вырабатывает последовательно снача35

40

45

50

кого уровня на входе 5 (К ТИР Н) п рывания микропроцессора 4 приводит прекращению аппаратного режима пре вания и позволяет микропроцессору рейти к выполнению следующего блок подпрограммы прерывания от нуль-ор нов.

Блок СЗ Ток нагрузки равен нулю

Анализируется состояние бита 07 байта входной информации (см. табл по которому определяется значение текущий момент времени переменной L характеризующей наличие тока нагру ки. Если , то ток в нагрузке п текает, и программа переходит к бл ку Сб. Если ,. что соответству отсутствию тока в нагрузке, то про грамма переходит к блоку С4.

Блок С4 Началькьй режим.

Блок работает, если ток нагрузки равен нулю. Отсутствие тока в нагр ке может быть вызвано одной из дву причин: либо в данный момент време имеет место начальный режим и прео

ла цикл Вывод, а затем цикл Ввод. разователь еще не включен,либо наВыданный адрес поступает на вход 53 блока 49 ввода пассивных дискретных сигналов, в котором деошфрируется по

ступила пауза в связи с тем, что т работавшего места снизился до нулевого уровня, и следует подавать им

35615524

сигналу Вывод, поступающему с выхода 19 параллельного интерфейса 9 на вход 50 блока 49. Поступление сигнала управления Ввод с выхода

,19 параллельного интерфейса 9 на вход 51 блока 49 приводит к появлению на управляющем выходе 58 последнего управляющего импульса Ввод высокого уровня напряжения (фиг. 6).

JO Этот импульс, поступая на вход 28 блока 24 нуль-органов и регистратора полярностей фаз, стробирует по входу управления клапан 91, в результате чего байт входной информации постуJ5 пает с информационного выхода 30 блока 24 нуль-органов и РПФ на вход 54 блока 49 ввода дискретных пассивных сигналов, а затем с выхода 52 последнего на информационный вход 17 па2Q раллельного интерфейса 9. Одновременно импульс Ввод высокого уровня напряжения с входа 28 блока 24 нуль- органов и РПФ устанавливает D-триггер 93 по его S-входу (фиг. 6). Это при-

25 водит к появлению низкого уровня напряжения на инверсном выходе D-триг- гера 93 и, следовательно, на выходе 31 блока нуль-органов и . в результате восстановление низкого уровня на

зо 1 Требование параллельного интерфейса 9 и, следовательно, высо35

40

45

50

кого уровня на входе 5 (К ТИР Н) прерывания микропроцессора 4 приводит к прекращению аппаратного режима прерывания и позволяет микропроцессору перейти к выполнению следующего блока подпрограммы прерывания от нуль-органов.

Блок СЗ Ток нагрузки равен нулю

Анализируется состояние бита 07 байта входной информации (см. табл.2) по которому определяется значение в текущий момент времени переменной LC, характеризующей наличие тока нагрузки. Если , то ток в нагрузке протекает, и программа переходит к блоку Сб. Если ,. что соответствует отсутствию тока в нагрузке, то программа переходит к блоку С4.

Блок С4 Началькьй режим.

Блок работает, если ток нагрузки равен нулю. Отсутствие тока в нагрузке может быть вызвано одной из двух причин: либо в данный момент времени имеет место начальный режим и преоб разователь еще не включен,либо наступила пауза в связи с тем, что ток работавшего места снизился до нулевого уровня, и следует подавать импульсы отпирания на очередной мост, По состоянию признака начального режима программа анализирует, имеет место начальный или циклический режим. Если в словесостояния программы бит начального режима установлен, то программа переходит к блоку С6, если нет, то к блоку С5.

Блок С5 Корректирование значения угла отпирания.

Так как в предыдущих блоках установлено, что имеет место циклический режим программы и ток принял нулевое значение в связи со сменой знака, т,е. произошло внеочередное прерывание от блока 40, то ocyniecT- вляется остановка и сброс всех ранее запущенных программно-управляемых счетчиков. Так.как ток в нагрузке прекратился, то с момента прерывания от нуль-органа блока 40 регистрации нуля и полярности тока нагрузки началась пауза между включенными состояниями силовых мостов, Эта пауза продлится до включения очередного (j+l)-го моста после отработки очередного угла отпирания csi(: к , которое произойдет в момент выдачи кода управляющего слова в блок 22 на включение выбранной цары вентилей. Угол отпирания при этом вычисляется следующим образом:

(A.U j,K где о(, с1 - последнее значение угла

J) к К

отпирания, вычисленное на предьщущем интервале синхронизации;

j - переменная, характеризующая номер очередного включаемог о моста, имеет только два значения О и 1, причем при , при .

Полученное значение умножается на масштабный коэффициент К и результат записывается в.ячейку текущего угла отпирания с именем CALP . Одновременно изменяется на противоположное значение величины sign D ц. Затем в слове состояния программы устанавливается признак того, что идет от- .работка паузы, т.е. . Это нужно для того, чтобы при занесении внеочередного управляющего слова в динамический массив не произвести на- рсцдивание его указателя текущего ад- р.еса.

Таким образом, реализация задерж-1 ки включения очередного вступаюп;его , в работу моста осуществляется автоматически. При этом предусматривается,

чтобы расчетное значение текущего угла отпирания (lU-t;, к не было меньше принятого значения угла паузы rf, . Блок С6 Работает ведуьций мост. По состоянию бита 06 байта входной

информации (табл, 2) микропроцессор проверяет значение логической переменной AM, характеризующей адрес включаемого моста. Если , то требуется .включить ведусщй мост Ml,

в этом случае программа переходит к блоку С7, Если , то подлежит включению ведомый мост М2, и программа переходит к блоку С8, ,

Блок С7 Выбор вентиля моста М.

Выбор загрузка и запуск ПУС.

Блок работает, если необходимо включить вентили силового моста Ml, Микропроцессор анализирует код состояния цолярностей фаз по битам 00-05

байта входной информации (табл, 2) и по нему определяет, зона какого вентиля имеет место в данный момент времени. Далее по табл, 4 осуществляется выбор номеров включаемого и

подтверждаемого вентиля моста Ml, т.е, определяется, какой код нужно вывести из блока 2 в блок 22 после отработки соответствующим счетчиком угла «Y, Затем в соответствии с номером включаемого вентиля выбирается номер ПУС, подлежащего загрузке и запуску: для вентилей В1 и В4 выбирается ПУС (код 01), для вентилей В2 и В5 - ПУС 2 (код 10), для вентилей

ВЗ и В6 - ПУС 3 (код 11), Номер ПУС, занимающий два бита 07 и 06 в 16- битном слове управляющим вывода, при- формировывается (см. табл, 4) к 6- битному коду включаемой пары вентилей

(биты 00-05). Сформированное таким образом управляющее слово заносится в ячейку динамического массива управляющих слов вывода. Перед занесением .слова в массив программа проверяет

состояние признака 7.С в слове состояния програ Ф1ы: если ,то содержимое указателя текущего адреса наращивается и слово помещается в следующую свободную ячейку памяти; если

же , то содеру имое указателя текущего адреса не наращивается, после чего слово помещается в массив в последнюю ячейку на место предыдуп его слова, а признак ZC обн ляется.

Далее формируется и по информационному каналу 18-37 выдается код управления блоком 34 счетчиков, содержащий адрес выбранного ПУС в старших битах (07 и 06) и двоичньй код временного интервала о1 из ячейки ALC в младших битах. Одновременно по каналу 20-39 управления блоком счетчиков выдается сигнал Вывод, после получения которого выбранный ПУС запускается (фиг. 7).

Блок С8 Выбор вентиля моста Ml. Выбор, загрузка и запуск ПУС.

Блок работает, если в блоке С6 было определено, что необходимо вклю чить вентили силового моста М2. Этот блок аналогичен блоку С7, отличие его состоит только в том, что в . соответствии с номером зоны по табл. 4.осуществляется выбор очередной пары из группы вентилей Bl -Вб код которых в управляющем слове вывода занимает биты 08-13.

Блок С9 Выход из прерывания на расчет угла отпирания.

Осуществляется выход микропроцессора из режима прерывания от нуль органов, и программа переходит к блоку В6, т.е. сбрасывает признак начального режима, а затем принимает новую системную и технологическую информацию, в соответствии с которой выполняет- расчет следующего угла отпирания тл.

Блок D1 Прерывание от программно-управляемого счетчика.

После зацуска выбранный счетчик ПУС 1, ПУС 2 или ПУС 3 начинает вычитать из записанного в него в блоках алгоритма С/ или 08 начального кода по единице с приходом каждого тактового импульса от генератора 1. После отсчета соответствующего на- чальному коду интервала времени в момент обнуления он воздействует через блок приоритета (схему МОНТАЖНОЕ ИЛИ), выход 36 и вход 6 на систему прерываний микропроцессора 4. Процессор прерывает свою работу и переходит на подпрограмму D Прерывание от ПУС, т.е. на данный блок D1.

Блок D2 Считывание управляющего слова из динамического массива (ДМ)

Микропроцессор считывает очередное управляющее слово из ячейки с адресом СО М динамического массива в ОЗУ.

Блок 1)3 Включение выбранной пары вентилей.

0

5

5

О

,

5

0

0

5

В соответствии с кодом в битах 00-05 и 08-13 считанного из динамического массива управляющего слова микропроцессор выдает через блоки вывода данных 9 и 22 импульсы на отпирание выбранной пары вентилей, блок 22 распределения отпирающих импульсов усиливает их и выдает сигналы напряжения на управляющие электроды включаемого вентиля и предыдущего включенного вентиля для подтверждения проводящего состояния последнего (фиг. 7).

Блок D4 Подготовка ДМ и сброс ПУС.

В этом блоке выполняются подготовительные операции. Так как информация из первой ячейки ДМ с именем СО М использована, то содержимое всех последующих его ячеек, начиная со второй, переписывается без изменения в соседние ячейки с меньшими номерами, т.е. осуществляется сдвиг массива вперед на одну ячейку. После сдвига содержимое указателя текущего адреса уменьшается на 1 щаг.

По информации в битах 07 и 06 выведенного управляюр;его слова 3 (см. табл. 5) программа определяет, какой из трех ПУС закончил отсчет угла и вызвал текущее прерывание, после чего выполняет сброс триггера прерывания этого ПУС импульсным сигналом Ввод, выдаваемым микропроцессорным блоком по каналу 19-38.

Блок D5 Снятие импульсов отпирания.

Так kaK очередная пара вентилей включена отпираюпц1ми импульсами, выданными в блоке Dj, то микропроцессор вьщает через параллельный интерфейс 9 нулевой код в битах 00-05, 08-13, в соответствия с которым блок 22 снимает импульсы напряжения с Управляющих электродов включенной пары вентилей.

Блок D6 Выход из прерывания.

Происходит выход микропроцессора из режима прерывания от блока программно-управляемых счетчиков, и программа возвращается к той команде, перед которой произошло прерывание.

С приходом импульса синхронизация от следующего,очередного, нуль-органа блока 24 весь цикл работы микропроцессорного устройства для управления вентильным преобразователем по вторяется согласно блок-схеме алгоритма от блока С1 через подпрограм2у.1

му прерывания от нуль-органов (блоки С2-С9), далее через блоки В6-В10 основной программы и затем подпрограмму прерывания (блоки D1-D6) от блока счетчиков для зоны следующего включаемого вентиля.

. Таким образом, введение в устройство многоканального блока ввода дискретных пассивных сигналов и многоканального блока формирования заданий и коэффициентов позволяет сократить количество аппаратуры микропроцессорного вычислительного блока и суп;е- ственно расширить функциональные возможности устройства. Наличие в устройстве указанных средств ддтя ввода большого количества технологической информации в микропроцессорньй вычислительный блок дает возможность реализовать различные функции техни- ческой диагностики, осуществить ввод управляющих воздействий и изменение настроечных коэффициентов в процессе работы, а также реализовать эффективные алгоритмы оптимального управле- ния вентильным преобразователем.

.Формула изобре.тения

1. Микропроцессорное устройство для управления вентильным преобразователем, содержащее задающий ге- нератор тактовых импульсов, микропроцессорный вычислительный блок, включающий в себя микропроцессор с двумя входами прерывания, программно-задающий блок и блок ввода и вывода информации, связанные между собой каналом шин управления, адреса и данных, блок распределения и уси- ления отпирающих импульсов, выходы которого предназначены для подключения к управляющим электродам вентилей преобразователя, блок нуль-органов и регистратора полярностей фаз трехфазной питающей сети, основные входы которого предназначены для под соедин ния к клеммам питающей сети , содержащий вход считьшания, вход импульсного сигнала Нуль тока нагрузки, информационный выход и выход сигнала прерывания, блок счетчиков тактовых импульсов с входом тактирования, подключенным к выходу задающего генератора, выходом, подключенным к второму входу прерываний микропроцессора, информационным и двумя управляющими входами, блок регистрации нуля и полярности тока нагрузки

т5 30

5

Q

5

5

0

5

с тремя входами, предназначег.кыми для подсоединения к клеммам питающей сети, двумя входами, предназначенными для подключения к клеммам нагрузки преобразователя, выходом импульсного сигнала Hyjjb тока нагрузки, соединенным с входом импульсного сигнала Нуль тока нагрузки блока нуль-органов и регистратора полярностей фаз, и выходами логических сигналов Ток нагрузки и Адрес включаемого моста, и аналого-цифровой датчик сигнала обратной связи с двумя сигнальными входами, предназначенными для подключения к клеммам нагрузки, и многобитным информационным выходом, отличающееся тем, что, с целью расширения функциональных возможностей путем увеличения количества вводимых и выводимых в параллельном коде сигналов, устройство снабжено многоканальным блоком ввода дискретных пассивных сигналов с двумя входами управления, 156-битным информационным выходом, одним основным и п сигнальными 16- битными информационными входами, и п yпpaвляюpJJ ми однопроводными выходами, многоканальным блоком формирования заданий и коэффициентов с 1 информационными 16-битными выходами и 1 управляющими входами, аналого-цифровой датчик сигнала обратной связи снабжен управляю1 {м входом, блок ввода и вывода информации микропроцессорного вычислительного блока выполнен в виде параллельного интерфейса с 16- битными- информационными входом и выходом, управляюрщми выходами импульсных сигналов Ввод и Вывод и входом Требование, связанным с первым входом прерывания микропроцессора, блок нуль-органов и регистратора полярностей фаз снабжен двумя дополнительными входами логических сигналов, при этом информационные входы блока счетчиков тактовых импульсов и блока распределения и усиления отпирающих импульсов и адресный информационный вход блока ввода дискретных пассивных сигн алов подключены к 16-битному информационному выходу параллельного интерфейса, первый и второй входы управления блока счетчиков тактовых импульсов, первый и второй входы управления блока ввода дискретных пассивных сигналов подключены соответственно к выходам управляющих сигналов Ввод и Вывод па31

-13561

раллельного интерфейса, информационный 16-битный вход которого подсоединен к информационному выходу блока ввода дискретных пассивных сигналов, к сигнальным информационным входам и к соответствующим управляющим выходам которого подсоединены соответственно информационные выходы и соответствующие управляющие входы блока нуль-органов и регистратора полярностей фаз, многоканального блока формирования заданий и коэффициентов и аналого-цифрового датчика сигнала обратной связи, выходы логических сигналов Ток нагрузки и Ад- рее включаемого моста блока регистрации нуля и полярности тока нагрузки подключены соответственно к двум дополнительным входам логических сигналов Ток нагрузки и Адрес включаемого моста блока нуль-органов и регистратора полярностей фаз, выход сигнала прерывания которого подключен к входу Требование параллельного интерфейса, при этом многоканальньй блок ввода дискретных пассивных сигналов содержит q-битный дешифратор адреса канала ввода со схемой задания адреса и входом управления, 16 щин приема дискретной ин- формации, D-триггер с входом сброса и выходной регистр на D-триггерах с входом стробирования, причем основной информационный вход q-битного дешифратора адреса подсоединен к сташим 1пинам информационного входа блока, вход управления - к инверсному выходу D-триггера, а выходы - к п управляющим однопроводным выходам блока, шины приема дискретной инфор- мации подсоединены к п сигнальным информационным входам блока и к информационному входу выходного регистра, информационньй выход которого подключен к 16-битному информационно му выходу блока, а вход стробирования - к управляющему входу Ввод блока, который одновременно подсоединен к входу сброса D-триггера, D-вход которого подключен к шине сигнала Логическая 1, а вход синхронизации - к у11равляюс;ему входу Вывод блока.

Бит,№ |15Tl4ll3 12In |1о о9|о8|о7Тоб|051од|оз о2|01 00;

Содержи- Код адреса канала моевводимых данных

д

0

5532

2. Устройство по п. 1, отличающееся тем, что блок нуль- органов и регистратора полярностей фаз содержит 01есть каналов преобра- зования информации о состоянии полярностей фаз напряжений трехфазной питающей сети с последовательно соединенными нуль-органом и формирователем импульсов синхронизации в каждом из каналов, раэделительньй трансформатор, первичные фазные обмотки которого соединены в треугольник и подключены к питающей сети, а вторичные соединены в звезду и подключены к соответствующим парам нуль-орга нов, одного - для положительных, а другого - для отрицательных значений соответствующего линейного напряжения питающей сети в каждой паре, управляемый 8-битный клапан на восьми двухвходовых элементах И, .первые входы которых объединены и подсоединены к входу управления блока, семивходовый элемент И-НЕ и D-триггер с входом установки, причем выходы нуль-органов подключены соответственно к вторым входам с первого по шестой двухвходовых элементов И управляемого 8-битного клапана, 8- битный информационный выход которого подсоединен к информационному выходу блока, при этом выходы нуль-органов одновременно через соответствующие формирователи импульсов синхронизации связаны с соответствующими с первого по шестой входами семивходо- вого элемента И-НЁ, седьмой вход которого подсоединен к входу импульсного сигнала Нуль тока нагрузки блока, вход управления которого подсоединен к входу установки D-триггера, информационный вход которого подсое- динен к общей щине устройства, вход синхронизации - к выходу семивходо- вого элемента И-НЕ, а инверсный выход - к выходу сигнала прерывания блока, два дополнительных входа логических сигналов Ток нагрузки и Адрес включаемого моста которого подключены соответственно к вторым входам седьмого и восьмого двухвходовых элементов И управляемого ного клапана.

Таблица 1

Произвольный код

Номер нуль-органа (фиг. 2)78 88 868482 80

Линейное напрякениеАВ СВ САВАВСАС

Бит, № I ОуТоб 1 03 Го4 Г03 Го2То1 Гоо

Логичес-- кая переменная С AM АВ СВ СА ВА ВС АС

0 1 t О О О 1 0 J О О О I 1 О 00 О 11 1 0 О 01 1 О 00 111 00

i I I о о о

I .10 о 01 I о ,0011 000 II i о 01 I 10

0I I I о о

111000

о

1 I I I

1

2 3 4 5

6 I

2 3 4 5 6

В1

В 2

ВЗ

В4

В5

В6

В4

В5

Вй

В|

Н2

ИЗ

Примечание С- код лрограммно у1 равляемого счетчика; X - произвольный код.

Таблица 3

т А fi л и ц а 5

X .0 00 о 00 с с I о 00

X о 0000 о- с со о о о

X о о о ,0 о о с с о 00 I ХООООООССО О I 1 ХООООООССО 1 I о ХО. ОООООСС 1 100 Х001 IOOCCOOOO XOI 1000ССОООО Х110000ССОООО X 1 00001 с с о о 00 ХО о 00 1 I ССО о о о ХООО I I ОССОООО

0t

1I

I о

о о о о о о о о о о о о о о о о о о

MJ

ifez

1 взг{85 yj lyjs yj

М2

1 8Ъ

5l

BS

h.

t

1 8Ъ

5l

BS

фи.1

2S

у

o o2fi 029

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ПРОЦЕССОМ ДУГОВОЙ СВАРКИ НЕПЛАВЯЩИМСЯ ЭЛЕКТРОДОМ В СРЕДЕ ЗАЩИТНЫХ ГАЗОВ | 1988 |

|

SU1683244A1 |

| Устройство для управления вентильным преобразователем | 1980 |

|

SU1146781A1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ПРОЦЕССОМ ДУГОВОЙ СВАРКИ НЕПЛАВЯЩИМСЯ ЭЛЕКТРОДОМ В СРЕДЕ ЗАЩИТНЫХ ГАЗОВ | 1991 |

|

RU2077415C1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ВЕНТИЛЬНЫМ ПРЕОБРАЗОВАТЕЛЕМ | 1991 |

|

RU2064730C1 |

| Устройство для управления вентильным преобразователем | 1984 |

|

SU1205243A2 |

| Устройство для управления вентильным преобразователем | 1988 |

|

SU1677819A1 |

| Запоминающее устройство на цилиндрических магнитных доменах | 1987 |

|

SU1451768A1 |

| Устройство для сопряжения двух ЭВМ | 1989 |

|

SU1681307A1 |

| Способ передачи данных по шине, система связи для осуществления данного способа и устройство автоматической защиты для предотвращения аварийной ситуации на объекте управления | 2018 |

|

RU2705421C1 |

| Устройство для измерения массы и управления потоком сыпучего материала | 1987 |

|

SU1525475A1 |

Изобретение относится к электротехнике и может быть использовано для импульсно-фазового управления преобразователями частоты. Целью изобретения является расширение функциональных возможностей. Введение в устройство многоканального блока ввода дискретных пассивных сигналов и многоканального блока формирования заданий и коэффициентов позволяет сократить количество аппаратуры микг ропроцессорного вычислительного блока. Наличие в нем средств для вво- да большого количества технологической информации дает возможность реализовать функции технической диагностики, осуществить ввод управляющих воздействий, реализовать эффективные алгоритмы управления. 1 з.п. ф-лы, 8 ил., 5 табл.

LlTjd LT.d

ii

.J

фиё.7

82

C

ВБ

DZ

B7

из

68

Hit

(TJLJ

Редактор Т.Лазоренко

Составитель В.Бунаков Техред Л.Сердюкова

Заказ 5807/51

Тираж 659Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. А/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Корректор С.Шекмар

| Устройство для управления вентильным преобразователем | 1980 |

|

SU1146781A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР 1206951, кл | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1987-11-30—Публикация

1985-11-28—Подача