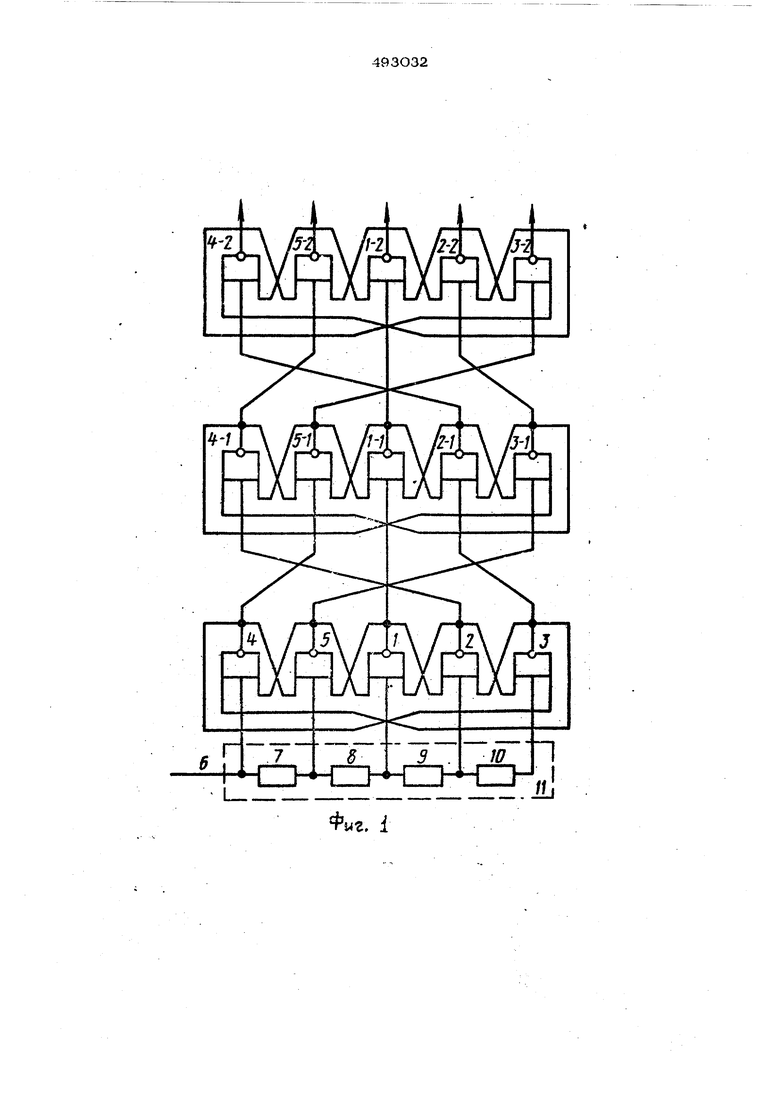

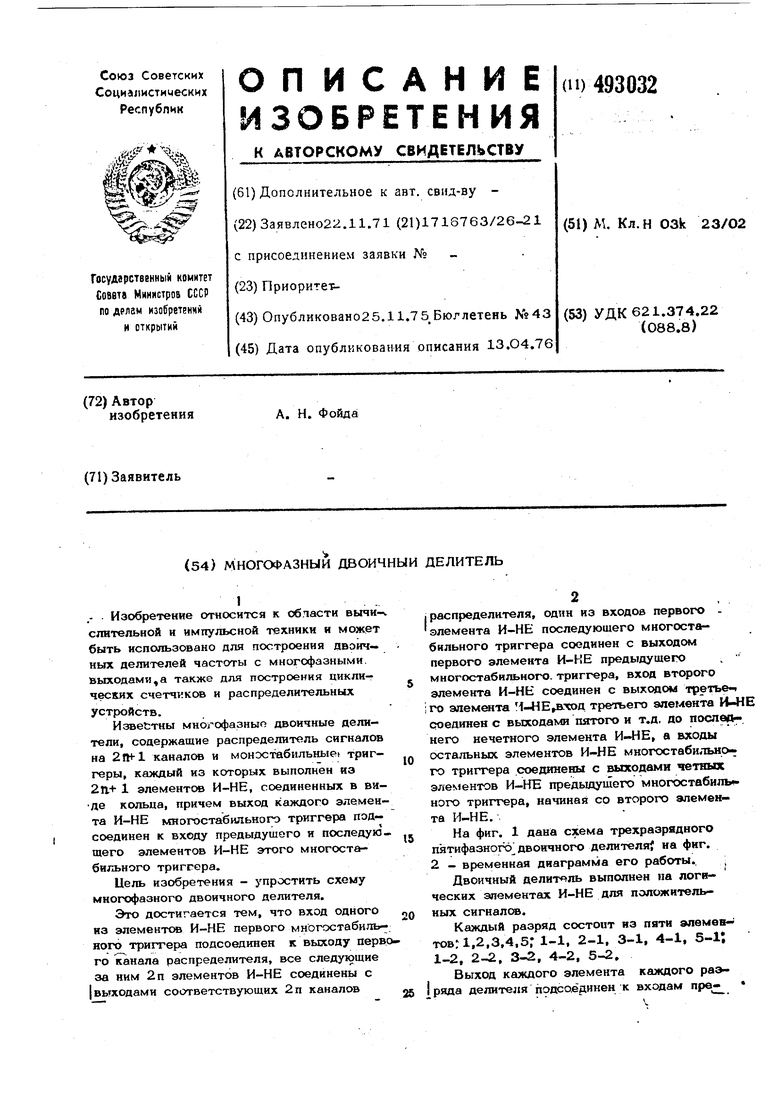

(54) МНОГОФАЗНЫЙ ДВОИЧНЫЙ ДЕЛИТЕЛЬ дыдущего и последующего элементов дан- ного разряда, Так, выход элемента 1 первого разряда подсоединен ко входу предыдущего элемента 5 и ко входу последую- щего элемента 2. Аналогично выход эле- мента 2 подсоединен ко входам элементов 1 и 3 и т.д. Вход элемента 4 первого многос,табильного триггера соединен с выходом 6 вого канала распредели.теля. Все следующие за ним 2Пг элементов многостабильного / триггера соединены со следующими соо- ветствутощими выходами распределителя, так элемент 7 соединен с выходом распредели I теля, а вход элемента 1 с выходом распре делителя и т.д. Один из входов первого элемента 1-1 И-НЕ последующего многостабильного триггера соединен с выходом элемента 1 предыдущего многостабильного триггера, вход элемента 2-1 соединен с выходом элемента 3, вход элемента 3-1 соединен с выходом элемокта 5 и т.д. до последнего н чотного элемента И-НЕ предыдущего многостабильного триггера. Входы остальных элем тов И-НЕ многостабияьного триггера соедин , ны с выходами четных элементов предыдуще многостабильного триггера, начиная со втор го элемента; Так,вход элемента 4-1 соедине с выходом элемента 2, а вход элемента 5-1 соединен с выходом элемента 4. Все следующие разряды делителя подсоединяются к предыдущему аналогично как второй разряд к первому. Положительным качеством схемы также является то, что входные тактирующие импул сы для первого разряда делителя можно получить, применяя линию задержки. Причем в ходные импульсы, управляющие первым разрядом делителя могут иметь перекрытие. Единственным условием является то, чтобы в любой момент времени в разряде делителя были два, а в следующий момент три рядом стоящие элемента, соединеГппзЮ триггерными связками,на которые в данный м мент времени не поданы входные импульсы. Предположим, что в первоначальный момент времени ti (см, фиг. 2) все раз- ряды делителя находятся в положении cf-низ- КИМ потеняиалом напряжения на выходе элементе 2 5каждого; разряда и с высокими на выходе остальных элементов. В момеит t на выходе 6 распределителя ty на выходе сигналов появится отрицательный импульс. Он не вызывает изменение состояния схемы делителя. В момент tn появляется отрипательнэй импульс на выходе 7 распределителя сигмалев, который вызывает появление на выходе элемента 5 положцтельного потендиала. Положительный потенциал с выхода элемента 5 поступает на вход элемента 4 и вызывает пояозление на выходе элемента 4 отрицательного потенциала. В момент t появляется отрицательный импульс на выходе 8 распределителя сигналов (на фиг. 2 указаны эпюры на выходах всех элементов схемы, причем эпюра номера t соответству ет эпюре напряжений на выходе соответствующего элемента). Импульс на входе элемента 1 в момент д н® изменит состояние его выхода.. I В момент / появляется отрицательный импульс на выходе 9 распределителя сигналов, который поступает на вход элемента 2 и вызывает на выходе элемента 2 положительный потенциал. Положите-. льный потенциал с выхода элемента 2 поступает на вход элемента 1 и на вькоде элемента 1 появляется отрицательный потенциал, так как на остальных входах Элемента 1 положительный потенциал. В момент „ на выходе 1О появляет ся импульс. Данный импульс изменения состояния схемы не вызывает, так. как на выходе элемента 3, на который он пОступает, был уже положительный потенциал, В момент / на выходе распределителя 11 сигналов по5тляется второй импульс и, следовательно, на выходе элемента 4 появится положительный потенциал, который поступит на вход элемента 3-1 и ьь зовет изменение его выходного потенциала на отрицательный, так как на остальных входах элемента 3 положительные потенциалы. В момент о на выходе 7 распределителя сигналов появляется импульс. Он не вызывает изменения состояния схемы. В момент выходе 8 распредели-: теля сигналов появляется очередной отри цательный импульс, который поступит на вход элемента 1 и вызовет на выходе элемента 1 положительный потенциал. Положительный потенциал с выхода, элемён - та 1, поступая на вход элемента 5, вы- зьгоает изменение потенциала на выходе элемента 5 на ртрицательный. В момент i, на выходе 9 распределителя снгг налов пояЫтяется импульс.. Данный импульс не иэмеиит состояния схемы. В момент .. .. на выходе 1О распреелителя сигналов появляется отрицательный импульс, который сызьтает на выхо- де элемента 3 положительный потенциал. Положительный потенциал с выхода элемента 3 поступает на вход элемента 2 и вызьгоает на его выходе отрицательный 5 потенциал, так как на остальных входах. элемента 2 действуют положительные потенциалы.

В момент t „ на выходе 6 распределитепя появляется отрицательный импульс. 10 Этот импульс не вызьтает никаких изменений состояния схемы.

В момент t на выходе 7 распредед. о

пителя появляется очередной отрицательны импульс, который поступает на вход элемен- а 5 и вызывает его переключение и т. д.

Аналогично будут переключаться элементы первого разряда при приходе следующих импульсов на вход первого разряда делителя.20

На вход втсрого разряда делителя поступают импульсы с выходов элементов первого разряда.

На вход третьего разряда делителя поступают импульсы с выходов элементов23 второго разряда делителя.

Работа второго и третьего разрядов делителя аналогична работе первого разряда.

С выходов элементов первого разряда 30 снимаются импульсы с периодом в два раза больше, чем период импульсов на входе делителя. С выходов элементов второго и третьего разрядов делителя снимаются ик пульсы с периодом соответственно в четыре и в восемь раз больше, чем период импульсов на входе 6 делителя.

Скважность импульсов на выходе многовыходового двоичного делителя при малом

числе разрядов можно рогулировать.с помощью линий Задержек.

С ростом числа разрядов скважность импульсов на выходе делителя стремится к величине-j 2т

т

где (П - количество элементов в разряде. Формула изобретения

Многофазный двоичный делитель, содержащий распределитель сигналов на 21 1 каналов и многостабильные триггеры, каждый из которых выполнен из 2«+ 1 элементов И-НЕ, соединениых в виде кольца, приI чем выход каждого элемента И-НЕ мно Ч стабильного триггера подсоединен к входу предыдущего и последующего элементов И-НЕ этого многостабильного триггера, отличающийся тем, что, с целью упрощения схемы, вход одного из

элементов И-НЕ первого многостабильиого триггера подсоединен к выходу первого к 1нала распределителя, все следующие за ним 2 П элементов И-НЕ соединены с выходами соответствующих 2 Я- каналов распределителя, один из входов первого элемента И-НЕ последуюшего многостабильного триггера соединен с выходом первого элемента И-НЕ предыдущего многостабильного триг|гера, вход второго элемента И-НЕ соеди- ( нен с выходом третьего элемента И-НЕ, Вход третьего элемента И-НЕ соединен с выходом пятого и т.д. до последнего нечетного элемента И-НЕ, а входы остальных элементов И-НЕ многостабильного триггера соединены с выходами четных элементов И-НЕ предыдущего многостабильяого Триггера, начиная со второго элемента И-НЕ.

40

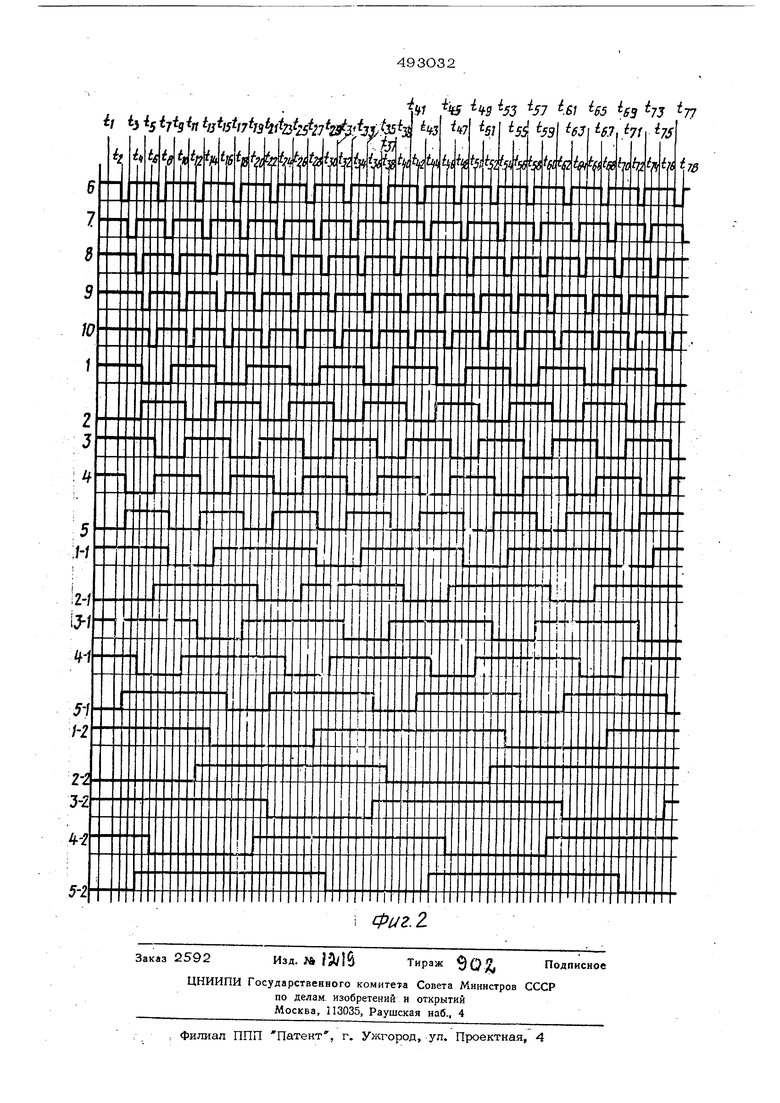

Фыг. 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофазный делитель числа импульсов | 1974 |

|

SU526080A1 |

| Распределитель импульсов | 1973 |

|

SU484652A1 |

| Двоичный делитель импульсов | 1974 |

|

SU657616A1 |

| Распределитель импульсов | 1976 |

|

SU610301A1 |

| Линия задержки импульсов | 1976 |

|

SU741466A1 |

| Распределитель импульсов на нечетное число каналов | 1985 |

|

SU1324101A1 |

| Распределитель импульсов | 1977 |

|

SU705683A2 |

| Распределитель импульсов | 1977 |

|

SU744998A1 |

| Счетчик | 1976 |

|

SU657617A1 |

| Счетчик на кольцевом регистре | 1978 |

|

SU733111A1 |

Авторы

Даты

1975-11-25—Публикация

1971-11-22—Подача