Изобретение относится к вычислительной и импульсной технике и може быть использовано для построения схем двоичных делителей импульсов. Известен двоичный делитель импуль сов, выполненный на элементах И-ffE/ ИЛИ-НЕ, первый разряд которого представляет собой Т-триггер на бднбтактном Д-триггере,выполненном на трех асинхронных R-S-триггерах одном информационном и двух установочных, каждый последующий нечетный разряд - Т- триггер на двухтактном Д-триггере с перекрывающимися тактами, состоящий из асинхронного R-S-триггера и трех элементов И-НЕ/ ИЛИ-НЕ, объединенных триггерными свя зями, выходы первого и второго из ни соединены соответственно с S- и Rвходами асинхронного R-S-триггера сво его разряда, S - выход которого подключен к входу третьего элемента И-НЕ/ИЛИ-НЕ, а каждый четный разряд состоит из асинхронного R- 8 -тригге ра и элемента И-НЕ/ИЛИ-НЕ, выход последнего соединен с 5 -входом асинхронного R-S-триггера l . Известное устройство имеет большое число входов в применяемых элементах и большое число связей между элементами, что существенно снижает надежность его работы.. Целью изобретение является повышение надежности работы устройства. Поставленная цель достигается тем, что в двоичный делитель импульсов, выполненный на элементах И-НЕ/ИЛИ-НЕ, первый разряд которого представляет собой Т-триггер на однотактном Д-триггере, выполненном на трех асинхро нных R-S-триггерах, одном информационном и двух установочных, каждый последующий нечетный разряд - Т-триггер на двухтактном Д-триггере с перекрывающимися тактами, состоящий из асинхронного Н-З гтриггера и трех элементов И-НЕ/ИЛИ-НЕ, объединенных триггерными связями, выходы первого и второго из которых соединены соответственно с 5- и R- входами . асинхронного R-S-триггера своего разряда, S - выход которого подключен по входу третьего элемента И-НЕ/ИЛИ-НЕ, а каждый четный разряд состоит из асинхронного R-S-триггера и элемента И-НЕ/ИЛИ-НЕ, выход которого соединен с S - входом псинхройноный R-S-триггер, в каждый четный разряд введен дополнительный асинхронронный Т -S-триггер. 3- вход крторого соединен с R - выходом асинхронного R-S- триггера своего разряда, R- вход - с S - входом acHHxpOHfioro триггера предыдущего разряда и с первым входом элемента И-НЕ/ИЛИ-НЕ своего разряда, второй вход которого подключен к Ц, - выходу асинхронного R-S -триггера предыдущего разряда, а третий вход- к R, -выходу дополнинительного асинхронного К-З-триггера, 5- выход которого соединен с первым входом второго элеме 1та И-ИЕ/ИЛИ-НЕ последующего разряда, при этом TJ - вход асинхронного R-Sтриггера четного разряда соединен с R-входом асинхронного R-S-триггера предыдущего разряда, а S -выход - с другими входами первого и второго элементов И-НЕ/ИЛИ-НЕ последующего разряда.

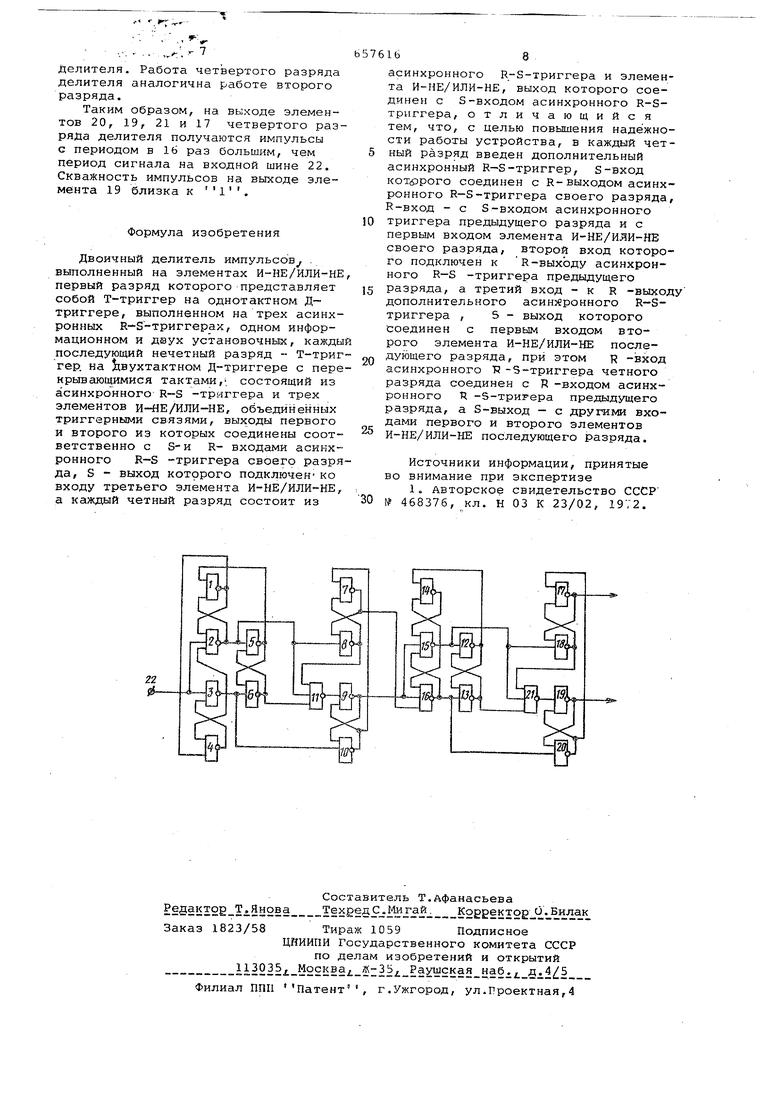

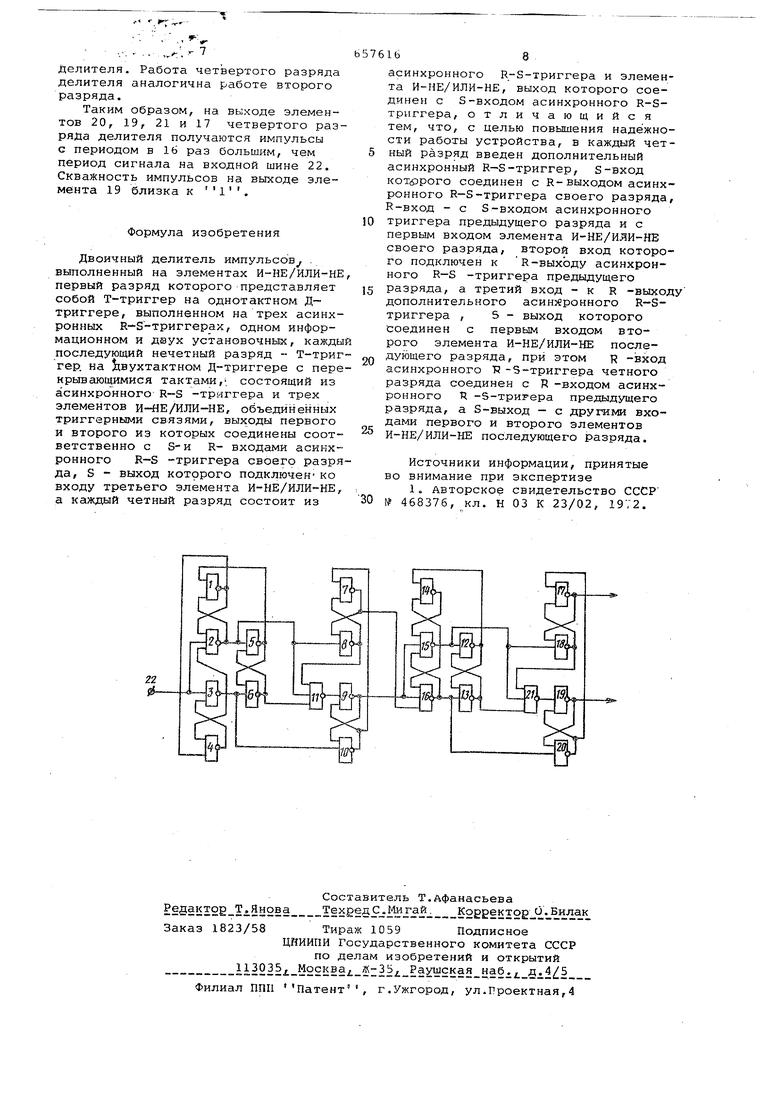

На чертеже представлена структурная электрическая схема предлагаемого двоичного делителя импульсов.

Двоичный делитель импульсов выполнен на элементах И-ПЕ для положительных сигналов на входе.

Первый разряд устройства выполнен на элементах И-НЕ 1-6 и представляет собой Т-триггер на однотактном Дтриггере, выполненном на трех асинхронных R-s-триггерах {одном информационном на элементах И-НЕ 5 и 6 и двух установочных на элементах.И-НЕ 1,2 и 3-, 4) .

г Четные разряды состоят из двух асинхронных R-S-триггеров и одного элемента И-НЕ. Так второй разряд состоит из двух асинхронных R-Sтриггеров на элементах 7, 8 и 9, 10 и элемента И-НЕ 11,

Каждый нечетный разряд, начиная с третьего, выполнен в виде Т-триггера на основе двухтактного Д-триггера с перекрывающимися тактами, состоящего из асинхронного R-S-триггера на элементах И-НЕ 12 и 13 и трех элементов И-НЕ 14,15 и 16, объединенных триггерными связями.

Четвертый разряд выполнен на двух асинхронных Тг -S-триггерах на элементах И-НЕ 17,18 и 19, 20 и элементе И-НЕ 21.

Входная шина 22 является входом двоичного делителя импульсов.

Устройство работает следующим образом. °

Допустим, что перед началом подачи положительных импульсов на входную шину 22 в момент времения t. на выходах элементов 1,2,3,6,7,10, 11, 13, 14, 15, 16, 17, 20 и 21 находится высокий потенциал, а на выходах элементов 4, 5, 8, 9, 12, 18 и 19 - низкий потенциал.

Услов-ием устойчивой работы четных разрядов данного делителя является то, что отрицательный импульс , приходящий на вход элемента 10 (20), начинается во время дейстВИЯ отрицательного импульса, приходящего с предыдущего разряда на вход элемента 11 (21), и оканчивается по окончании импульса на входе элемента 11 (21) раньше, чем начинается следующ.ий отрицательный импульс, приходящий с предыдущего разряда на вход, элемента 11 (21). Отрицательный импульс, приходящий с предыдущего разряда на вход элемента 8 (18) , должен начинаться одновременно с началом или после начала действия цательного импульса, приходящего с предыдущего разряда на вход элемента 11(21), а оканчиваться раньше, чем начинается действие отрицательного импульса с предыдущего разряда на входе элемента 10 (20).

Если подать на вход элемента 10 потенциал с выхода элемента 3, на вход элемента 8 - потенциал с выхода элемента 2 и на входы элемента 11- потенциал с выходов элементов 2 и 6,, ,то выполняется условие второго (четного) разряда. Работа второго разряда делителя происходит следующим образом.

В момент t на входе элементов 8 и 11,, появляется отрицательный потенциал, поступающий с выхода элемента 2. После времени, равного времени срабатывания одного элемента, на выходе элемента 8 в момент появляется положительный потенциал, который поступает на вход элементов 7 и 11. Так как на другом входе элемента 7 в это время тоже дейстзует положительный потенциал, то на выходе элемента 7 в момент tj появляется низкий потенциал.

В момент -1 дпоявляется отрицательный потенциал на входе элемента 10, поступающий с выхода элемента 3, но изменения потенциала на выходе элемента 10 он не вызьтает, так как на входе элемента 10 уже присутствует низкий потенциал, поступающий с выхода элемента 9.

В момент -t 2 ивается действие отрицательного потенциала навходе элемента 11, поступающего с выхода элемента 6, ив момент t на выходе элемента 11 появляется низкий потенциал, поскольку на всех входах элемента 11 в это время действуют высокие потенциалы. Низкий потенциал с выхода элемента II, поступая на выход элемента 9, вызывает на выходе элемента 9 в момент t высокий потенциал.

В момент оканчивается действие отрицательного потенциала на выходе элемента 3,а в момент Ц на выходе элемента 10 появляется низкий погенцмал. Низкий потенциал с выхода элемента 10 поступает на вход элемента 7, и на выходе элемента 7 в момент появляется высокий потенциал. Высокий потенциал с выхода элемента 7, поступая на вход элемен5та 8, вызывает в момент ttg на выхо де элемента 8 низкий потенциала, так как на другом входе элемента 8 в это время действует высокий потенциал. Низкий потенциал с выхода эле мента 8 поступает на вход элемента и вызывает на выходе этого элемента в момент t высокий потенциал. С момента на выходе эл .мента 2 появляется низкий потенциал который, поступая на входы элементов 8 и 11, вызывает на выходе элемента 8 с момента i по -tg положительный потенциал, а С момента н выходе элемента В снова находится отрицательный потенциал, так как элемент 7 удерживается в это время в положении с высоким потенциалом низким потенциалом, поступающим с выхода элемента 10. В момент i,2f на выходе элемента 3 появляется низкий потенциал, который поступает на вход элемента 10 и вызывает на его выходе в момент tgg положительный потенциал. Положитель ный потенциал с выхода 10 поступает па вход элемента 9 и вызывает на выходе элеме:1та 9 в момент низкий потенциал,,так как на другом входе элемента 9 в это время тоже действует высокий потенциал. В момент tggпоявляется низкий потэнциал на выходе элемента 2, который поступает на входы элементов 8 и 11 и вызывает переключение элемента 8 в момент положение с высоким потенциалом на выходе. Высокий потенциал с выхода элемента 8 вызывает на выходе элемента 7 в момент t 57 низкий потенциал, так как на другом входе элемента 7 в эт время действует тоже высокий потенциал. Переключения элемента 11 не происходит, так как на одном его входе до момента t действует низкий потенциал, поступающий с выхода элемента 2, а на другом входе до момента t, действует низкий потенц ал, поступающий с выхода элемента 6. в момент t44 на всех входах элемента И действуют высокие потенциалы и на его выходе в момент является низкий потенциал, который вызывает на выходе элемента 9 в момент t высокий потенциал. В момент заканчивается действие отрицательного импульса на вход элемента 10 (поступавшего с выхода элемента 3), и на выходе элемента 10 в момент появляется низкий потенциал, устанавливающий триггер на элементах 7 и 8 в положение с высоким потенциалом на вьдходе элемента 7 и низким- на выходе элемента 8. Низкий потенциал на выходе элемента 8 вызывает в момент t появление высокого потенциала на вы ходе элемента 11 и т.д. 6 На выходах элементов 9 и & в результате работы второго разряда делителя появляются импульсы, с частотой в четыре раза меньшей, чем на входной шине 22 делителя. Условием работы третьего и более старших нечетных разрядов является то, что положительный импульс, приходящий с предыдущего разряда на вход элемента 16, приходит позже и оканчивается позже, чем положительный импульс, приходящий с предыдущего разряда одновреме 1но на входы элемер1тов 15 и 16. Данным требованиям удовлетворяют сигналы, получаемые на выходах элементов 7 и 9. Рассмотрим работу третьего разряда. Так как в момент t положительный импульс, поступающий на вход элемента 15 с выхода элемента 9, вызывает срабатывание элемента 15, то на выходе элемента 15 появляется низкий потенциал, устанавливающий информационный R-S-триггер на элементах 12 и 13 в положение высоким потенциалом на выходе элемента 12 и низким- на выходе 13. По окончании действия положительного импульса в момент -tog на входе элемента 15 появляется в момент tJQ пчложительный потенциал, вызывающий переключение элемента 14 в момент в положение с низким потенциалом на выходе, так как на другом входе элемента 14 действует низкий потенциал с выхода элемента 12. Следующий положительный импульс, поступающий на вход элемента 15 с выхода 9 в момент , не вызывает срабатывания элемента 15, так как на одном из входов элемента 15 действует низкий потенциал, поступающий с выхода элемента 14. В момент на выходе элемента 7 появляется положительный импульс, который, поступая на вход элемента 16, вызывает появление на выходе элемента 16 в момент низкого потенциала, так как на всех входах элемента 16 действуют высокие потенциалы. Низкий потенциал с выхода элемента 16 устанавливает информационный R S-триггер в положеНизкий потенциал с единичного плеча данного триггера (с выхода элемента 12) вызывает срабатьшание элемента 14, и на выходе элемента 14 в момент t53 появляется высокий потенциал. Следующий положительный импульс, поступающий на вход элемента 15 в момент tyg вызывае его срабатывание и переключение и-Sтриггера в состояние и т.д. Временные соотношения между импульсами, получаемые на выходе элемента 16, элементов 13 и 15 и элемента .14 такие, которые удовлетЕОряют устойчивой работе четного ряда - .. :-. . ..,.,; -7 делителя. Работа четвертого разряда делителя аналогична работе второго разряда. Таким образом, на выходе элементов 20, 19, 21 и 17 четвертого разряда делителя получаются импульсы G периодом в 16 раз большим, чем период сигнала на входной шине 22. Скважность импульсов на выходе элемента 19 близка к . Формула изобретения Двоичный делитель импульсов . выполненный на элементах И-НЕ/ИЛИ-НЕ первый разряд которого представляет собой Т-триггер на однотактном Д триггере, выполненном на трех асинхронных Н-5-триггер ах, одном информационном и двух установочных, кажды последующий нечетный разряд - Т-триг гер. на двухтактном Д-триггере с пере крывающимися тактами, состоящий из асинхронного R-S -триггера и трех элементов И-ЯЕ/ИЛИ-НЕ, объединенных триггерными связями, выходы первого и второго из которых соединены соответственно с S-и R- входами асинхронного R-S -триггера своего разря да, S - выход которого подключен ко входу третьего элемента И-НЕ/ИЛИ-НЕ а Кс1ждый четный разряд состоит из 16 асинхронного R-S-триггера и элемента И-НЕ/ИЛИ-НЕ, выход которого соединен с S-входом асинхронного R-Sтриггера, отличающийся тем, что, с целью повышения надёжности работы устройства, в каждый четный разряд введен дополнительный асинхронный К-S-триггер, S-вход котбэрого соединен с R-выходом асинхронного R-S-триггера своего разряда, R-вход - с S входом асинхронного триггера предыдущего разряда и с первым входом элемента И-НЕ/ИЛИ-НЕ своего разряда, второй вход которого подключен к R-выходу асинхронного R-S -триггера предыдущего разряда, а третий вход - к R -выходу дополнительного асин «ронного R-Sтриггера , S - выход которого соединен с первым входом второго элемента И-НЕ/ИЛИ-НЕ последующего разряда, при этом R -вход асинхронного Р-S-триггера четного разряда соединен с R -входом асинхронного U -S-тригера предыдущего разряда, а S-выход - с другими входами первого и второго элементов И-НЕ/ИЛИ-НЕ последующего разряда. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 468376, кл. К 03 К 23/02, 1972.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофазный делитель числа импульсов | 1974 |

|

SU526080A1 |

| Двоичный делитель импульсов | 1972 |

|

SU468376A1 |

| Многофазный двоичный делитель | 1971 |

|

SU493032A1 |

| Кольцевой распределитель импульсов | 1981 |

|

SU978349A1 |

| Линия задержки импульсов | 1976 |

|

SU741466A1 |

| Счетчик на кольцевом регистре | 1978 |

|

SU733111A1 |

| Счетчик на кольцевом регистре | 1977 |

|

SU738177A1 |

| Формирователь импульсов | 1981 |

|

SU966878A1 |

| Распределитель импульсов | 1977 |

|

SU705683A2 |

| ДВОИЧНЫЙ СЧЕТЧИК | 1972 |

|

SU336815A1 |

Авторы

Даты

1979-04-15—Публикация

1974-04-04—Подача