1

Изобретение относится к области импульсной и вычислительной техники и может быть использовано для построения линий задержки импульсов (ЛЗИ),

Известна линия задержки импульсов, каждый разряд которой выполнен на трех логических элементах И-НЕ (ИЛИ-НЕ), образующих друг с другом триггерные структу1Ж1. Выход одного из логических элементов И-НЕ (ИЛИ-НЕ) каждого предыдущего триггера соединен со входами двух логических элементов И-НЕ (ИЛИ-НЕ) каждого последующего разряда, а входы третьего логичес1«эго элемента И-НЕ (ИЛИ-НЕ) последующих разрядов соединены со входами одноименных логических элементов И-НЕ (ИЛИ-НЕ) предыдущего разряда, при этом источник тактовых импуль.сов подключен ко входам логических элементов И-НЕ (ИЛИ-НЕ), выходы которых соединены со входом двух логических элементов И-НЕ (ИЛИ-НЕ) каждого последующего разряда 1. Данная ЛЗИ на каждый разряд использует три элемента И-НЕ, два из которых трехвходовые, а один двухвходовой. Недостатком данной ЛЗИ является большое чис.пю элементов.

требуемых для ее построения и вследствие этого ма.лая надежность.

Известна линия задержки импульсов, содержащая T-fc -триггер, и П разрядов, каждый из которых содержит .триггер на двух элементах И-НЕ, вход установки в единицу каждого и триггера соединен с инверсным выходом n-l триггера, выход элемента

10

Ti -триггера соеустановки в

динен с шиной обнуления триггеров нечетных разрядов, а- выход элемен ь,. триггера

О

та установки в

соединен с шиной обнуления тригге15 .ров четных разрядов.

Недостатком данной линии задержки является большая сложность, выражающаяся в наличии на выходе каждого разряда ее ди(1 ференцирующих

20 .ВС-и.епочек. Наличие КС-цепочек усложняет выполнение данной линии задержки по интегральной технологии, уменьшает максимальную частоту работы линии задержки. Уход параметров

25 резисторов и конденсаторов приводит к ненадежной работе линии задержки.

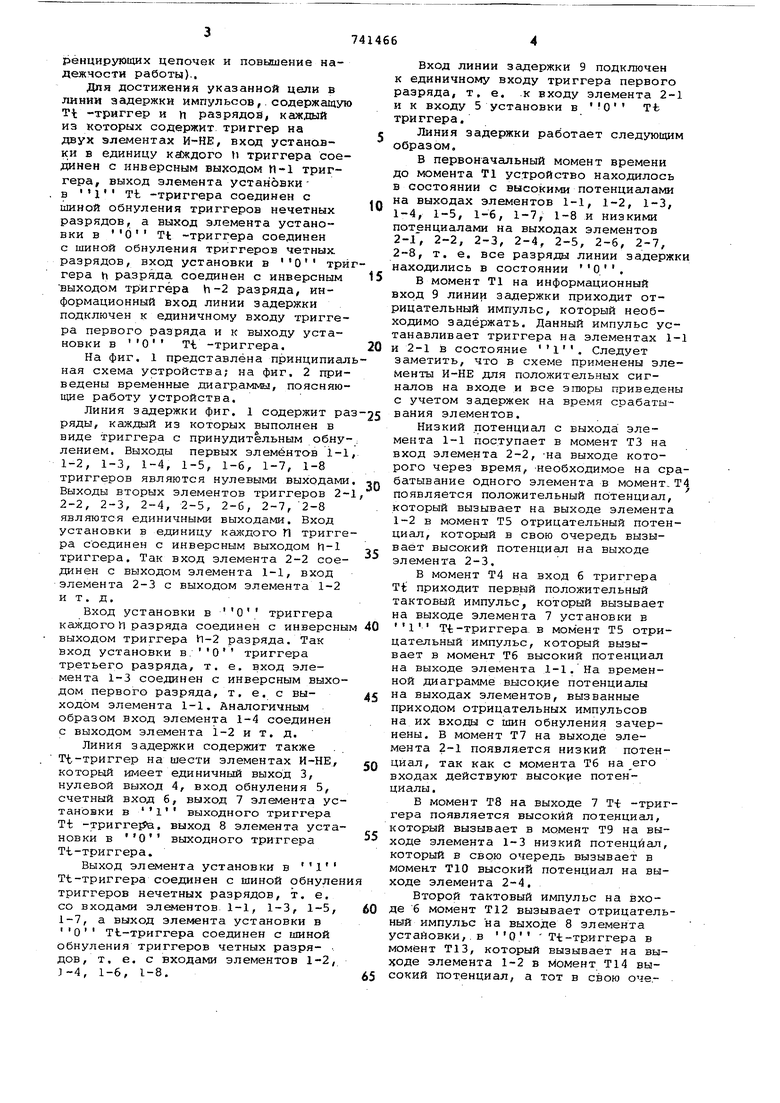

Целью изобретения является упрощение устройства (исключение дифференцирующих цепочек и повышение надежности работы).. Для достижения указанной цели в линии задержки импульсов,. содержащу Tt -триггер и п разрядой, каждый из которых содержит триггер на двух элементах И-НЕ, вход устанавки в единицу касждого я триггера сое динен с инверсным выходом И-1 триггера, выход элемента установкив Tt -триггера соединен с шиной обнуления триггеров нечетных разрядов, а выход элемента установки в О Tt -триггера соединен с шиной обнуления триггеров четных. разрядов, вход установки в О тр гера h разряда соединен с инверсным ВЫХОДОМ триггера h-2 разряда, информационный вход линии задержки подключен к единичному входу тригге ра первого разряда и к выходу устаTi -триггера. новки в На фиг, 1 представлена принципиа ная схема устройства; на фиг. 2 при ведены временные диаграммы, поясняю щие работу устройства. Линия задержки фиг. 1 содержит р ряды, каждый из которых выполнен в виде триггера с принудительным обн лением. Выходы первых элементов 11-2, 1-3, 1-4, 1-5, 1-6, 1-7, 1-8 триггеров являются нулевыми выходам Выходы вторых элементов триггеров 2 2-2, 2-3, 2-4, 2-5, 2-6, 2-7, 2-8 являются единичными выходами. Вход установки в единицу калсдого П тригг ра соединен с инверсным выходом n-l триггера. Так вход элемента 2-2 сое динен с выходом элемента 1-1, вход элемента 2-3 с выходом элемента 1-2 и т. д. Вход установки в О триггера каждого П разряда соединен с инверсн выходом триггера Vi-2 разряда. Так вход установки в. триггера третьего разряда, т. е. вход элемента 1-3 соединен с инверсным выхо дом первого разряда, т. е. с выходом элемента 1-1. Аналогичньлм образом вход элемента 1-4 соединен с выходом элемента 1-2 и т. д. Линия задержки содержит также Tt-триггер на шести элементах И-НЕ которЕяй имеет единичный выход 3, нулевой выход 4, вход обнуления 5, счетный вход 6, выход 7 элемента ус T-fc -триггера, выход 8 элемента уста выходного триггера новки в Tt-триггера, Выход элемента установки в Tt-триггера соединен с шиной обнуле триггеров нечетных разрядов, т. е. со входами элементов 1-1, 1-3, 1-5 1-7, а выход элемента установки в IIQI1 Tt-TpHrrepa соединен с шиной обнуления триггеров четных разрядов, т. е. с входами элементов 1-2 J-4, 1-6, 1-8. Вход линии задержки 9 подк.шочен к единичному входу триггера первого разряда, т.е. .к входу элемента 2-1 и к входу 5 установки в О Tt триггера. Линия задержки работает следующим образом. В первоначальный момент времени до момента Т1 устройство находилось в состоянии с высокими потенциалами на выходах элементов 1-1, 1-2, 1-3, 1-4, 1-5, 1-6, 1-7, 1-8 и низкими потенциалами на выходах элементов 2-Г, 2-2, 2-3, 2-4, 2-5, 2-6, 2-7, 2-8, т. е. все разряды линии задержки находились в состоянии В момент Т1 на информационный ход 9 линии задержки приходит отицательный импульс, который необходимо задержать. Данный импульс устанавливает триггера на элементах 1-1 и 2-1 в состояние . Следует заметить, что в схеме применены элементы И-НЕ для положительных сигналов на входе и все эпюры приведены с учетом задержек на время срабатывания элементов. Низкий потенциал с выхода элемента 1-1 поступает в момент ТЗ на вход элемента 2-2, на выходе которого через время, необходимое на срабатывание одного элемента в момент, Т4 появляется положительный потенциал, который вызывает на выходе элемента 1-2 в момент Т5 отрицательный потенциал, который в свою очередь вызывает высокий потенциал на выходе элемента 2-3. В момент Т4 на вход 6 триггера Tt приходит первый положительный тактовый импульс, который вызывает на выходе элемента 7 установки в T-t-триггера в момент Т5 отрицательный импульс, который вызывает в момен-т Т6 высокий потенциал на выходе элемента 1-1. На временной диаграмме высокие потенциалы на выходах элементов, вызванные приходом отрицательных импульсов на их входы с шин обнуления зачернены. В момент Т7 на выходе элемента 2-1 появляется низкий потенциал, так как с момента Т6 на его входах действуют высокие потенциалы . В момент Т8 на выходе 7 T-t -триггера появляется высокий потенциал, который вызывает в момент Т9 на выходе элемента 1-3 низкий потенциал, который в свою очередь вызывает в момен-т Т10 высокий потенциал на выходе элемента 2-4. Второй тактовый импульс на входе 6 момент Т12 вызывает отрицательный импульс на выходе 8 элемента устайовки, .в О T-fc-триггера в момент Т13, который вызывает на выходе элемента 1-2 в момент Т14 высокий потенциал, а тот в свою очередь вызывает в момент Т15 низкий потенциал на выходе элемента 2-2. 3 момент Т 15 оканчивается второй тактовый импульс на входе 6 и на выходе элемента 1-4 в момент Т17 появляется низкий потенциал. Аналогичным-обраэом после окончания действия третьего тактового импульса на входе 6, на выходе элемента 1-5 появляется в момент Т25 низкий потенциал. Таким образом,после окончания о редного тактового импульса на вход 6 инверсном; выходе очередного триг гера иэ м-триггеров линии задержки появляется отрицательный импульс. Благодаря соединению .входа уста триггера И разряда с новки в инверсным выходом триггера h-2 разряда, а также подключению информационного входа к единичному входу триггера первого разряда и к входу установки в О Tt -тригге ра удалось упростить Линию задержки, исключить дифференцирующие ЯСцепочки и тем самым повысить надеж ность работы устройства. Формула изобретения Линия зёшержки импульсов, .содержсодая Tt-триггер и fi разрядов, каждйй из которых содержит триггер на двух элементах И-НЕ, вход установки в единицу каждого п- триггера соединен,с инверсным выходом п-1 триггера, выход элемента установки в 1 Tt-триггера соединен с шиной обнуления триггеров нечетных разрядов, а выход элемента установки в Tt-триггера соединен с шиной обнуления триггеров четных разрядов/ отличающая с.я тем, что, с целью упрощения, вход устатриггера hразряда соеновки в динен с инверсным выходом триггера И-2 разряда, информационный вход линии задержки подключен к единичному входу триггера первого разряда и к входу установки в О T-tтриггера. Источники информсщии, принятые во внимание при экспертизе 1. Шляпоберский В.И. Элементы дискретных систем связи. Военное издательство министерства обороны СССР. М., 1965, с. 111-112 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Регистр | 1981 |

|

SU1024989A1 |

| Счетчик на кольцевом регистре | 1977 |

|

SU738177A1 |

| Счетчик на кольцевом регистре | 1978 |

|

SU733111A1 |

| Регистр сдвига | 1975 |

|

SU631992A1 |

| Функциональный цифроаналоговый преобразователь | 1988 |

|

SU1647902A1 |

| Устройство для формирования импульсных сигналов | 1990 |

|

SU1758858A1 |

| Устройство для формирования импульсных сигналов | 1990 |

|

SU1800599A1 |

| Двухтактный регистр сдвига | 1975 |

|

SU744732A1 |

| Генератор псевдослучайной последовательности | 1985 |

|

SU1305837A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки /ЭЛТ/ | 1989 |

|

SU1633387A1 |

5 TfS

ГЗО

Г2В

Авторы

Даты

1980-06-15—Публикация

1976-03-09—Подача