О5

«35

09

Изобретение относится к приборостроению g а именно к технике магнитной записИд и может быть использовано в аппаратуре для оценки макси- мальвой фазовой ошибки цифрового сигнала воспроизведения с носителя магнитной записи.

Целью изобретения является обеспечение контроля максимальной вели- чины фазовых искажений сигнала вое-, произведения«

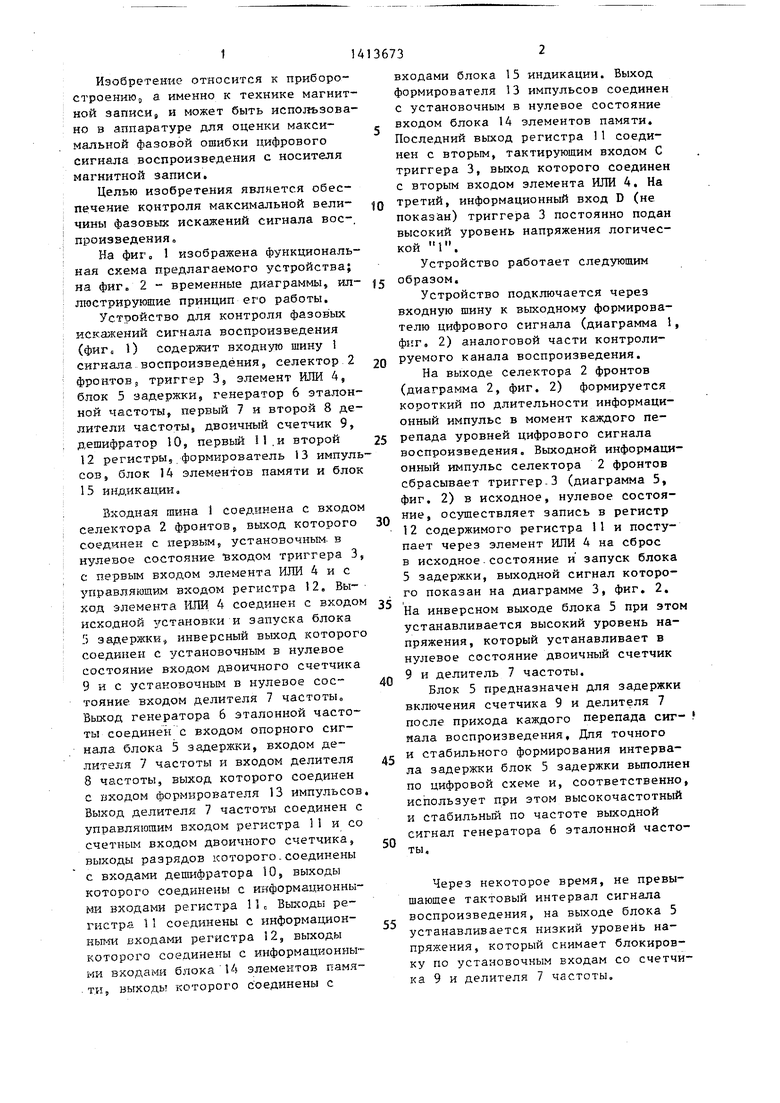

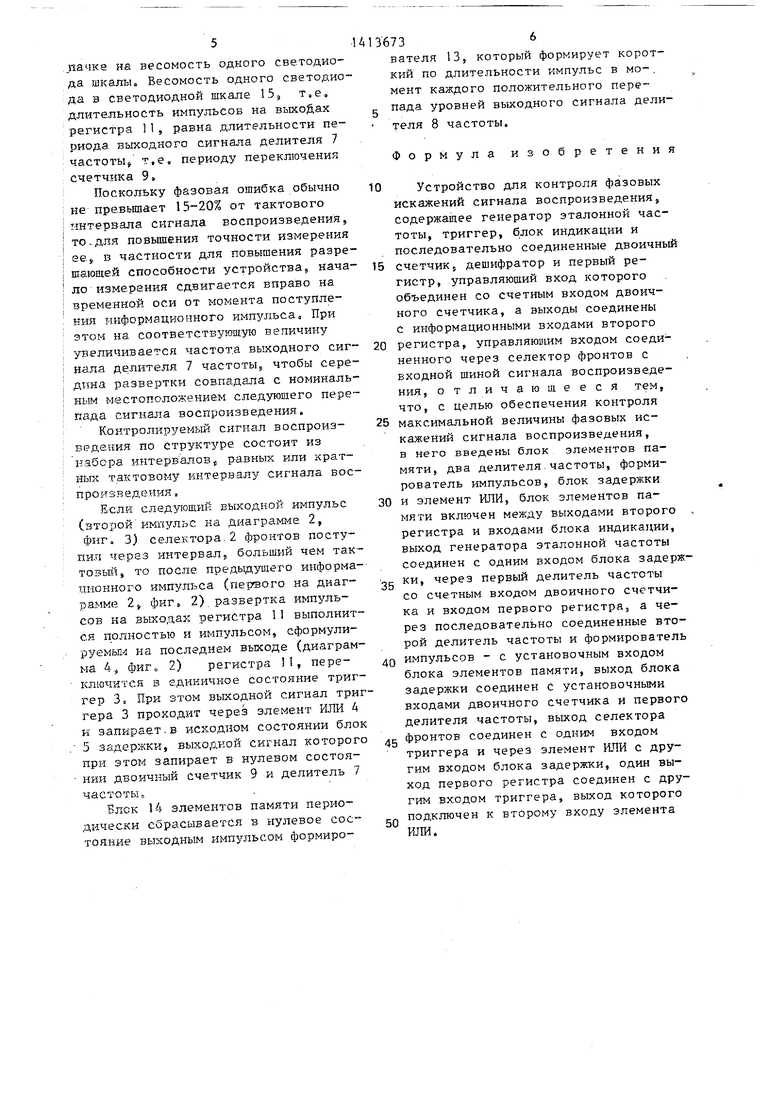

На фиг о 1 изображена функциональная схема предлагаемого устройства; на фиГе 2 - временные диаграммы, ил- люстрирующие принцип его работы.

Устройство для контроля фазовых искажений сигнала воспроизведения (фиг« 1) содержит входную шину 1 сигнала воспроизведения, селектор 2 фронтов, триггер 3, элемент ИЛИ 4, блок 5 задержки, генератор 6 эталон- ной частоты, первый 7 и второй 8 делители частоты, двоичный счетчик 9, дешифратор 10, первый П.и второй 12 регистры, формирователь 13 импульсов, блок 14 элементов памяти и блок 15 индикации.

Входная шина 1 соединена с входом селектора 2 фронтов, выход которого соединен с первым$ установочным, в нулевое состояние твходом триггера 3, с первым входом элемента ИЛИ 4 и с управляющим входом регистра 12, Вы ход элемента ЖГИ. 4 соединен с входом исходной установки и запуска блока 5 задержки, инверсный выход которого соединен с установочным в нулевое состояние входом двоичного счетчика 9 и с установочным в нулевое сое- тояние входом делителя 7 частоты Выход генератора 6 эталонной частоты соединен с входом опорного сигнала блока 5 задержки, входом делителя 7 частоты и входом делителя 8 частоты, выход которого соединен с входом формирователя 13 импульсов. Выход делителя 7 частоты соединен с управляющим входом регистра П и со счетным входом двоичного счетчика, выходы разрядов которого.соединены с входами дешифратора 10, выходы которого соединены с информационными входами регистра 11 с Выходы регистра 1 1 соединены с информацион- НЫ1-1И входами регистра 12, выходы которого соединены с информационными входами блока 14 элементов памяти, выходы которого Соединены с

входами блока 15 индикации. Выход формирователя 13 импульсов соединен с установочным в нулевое состояние входом блока 14 элементов памяти. Последний выход регистра 11 соединен с вторым, тактирующим входом С триггера 3, вьксод которого соединен с вторым входом элемента ИЛИ 4, На третий, информационньй вход D (не показан) триггера 3 постоянно подан высокий уровень напряжения логической 1.

Устройство работает следующим образом.

Устройство подключается через входную шину к вькодному формирователю цифрового сигнала (диаграмма 1 фиг, 2) аналоговой части контролируемого канала воспроизведения.

На выходе селектора 2 фронтов (диаграмма 2, фиг. 2) формируется короткий по длительности информационный импульс в момент каждого перепада уровней цифрового сигнала воспроизведения. Выходной информационный импульс селектора 2 фронтов сбрасывает триггер-3 (диаграмма 5, фиг. 2) в исходное, нулевое состояние, осуществляет запись в регистр 12 содержимого регистра 11 и поступает через элемент ИЛИ 4 на сброс в исходное - состояние и запуск блока 5 задержки, выходной сигнал которого показан на диаграмме 3, фиг. 2. На инверсном выходе блока 5 при это устанавливается высокий уровень напряжения, который устанавливает в нулевое состояние двоичный счетчик 9 и делитель 7 частоты.

Блок 5 предназначен для задержки включения счетчика 9 и делителя 7 после прихода каждого перепада сиг- нала воспроизведения. Для точного и стабильного формирования интервала задержки блок 5 задержки вьшолне по цифровой схеме и, соответственно использует при этом высокочастотный и стабильный по частоте выходной сигнал генератора 6 эталонной частоты.

Через некоторое время, не превы- шаюшее тактовый интервал сигнала воспроизведения, на выходе блока 5 устанавливается низкий уровень напряжения, который снимает блокировку по установочным входам со счетчика 9 и делителя 7 частоты.

Счетчик 9, дешифратор 10 и регистр II образуют распределитель импульсов. За каждый период выходного сигнала делителя 7 частоты формируется по одному импульсу поочередно на всех 16-ти выходах дешифратора 10 и на всех 16-ти выходах регистра П.

Регистр 11 предназначен для зашит работы устройства от импульсов, формируемых на некоторых выходах дешифратора 10 и обусловленных логикой внутренней работы дешифратора 10. Каждым положительным перепадом выходного сигнала делителя 7 частоты вначале осуществляется запись в регистр I1 выходного состояния дешифратора 10, а затем происходит переключение счетчика 9.

Наличие делителя .7 частоты связано с обеспечением точной привязки начала работы распределителя импульсов к выходному сигналу блока 5 задержки.

Таким образом, начало развертки, т.е. начало поочередного формирования импульсов на всех выходах регистра I1 соответствует отрицательному перепаду уровней сигнала на выходе блока 5 задержки. Середина развертки соответствует номинальному местоположению следующего тактового перепада уровней сигнала воспроизведения.

Выходная информация регистра П (высокий уровень напряжения на каком-то одном выходе и низкий уровень напряжения на остальных выходах регистра П) поступает на информационные входы регистра 12 и записывается в этот регистр в момент поступления очередного информационного импульса с выхода селектора 2 фронтов.

Этот очередной информационный импульс селектора 2, вследствие фазовых искажений сигнала воспроизведе- НИН, занимает на временной оси мес- то, отличное от его номинального местоположения. Поэтому сигнал (высокий уровень напряжения) будет записан в тот разряд регистра 12, который соответствует выходу регистра 11, выходной сигнал которого (высокий уровень напряжения) совпал во времени с данным информационным импульсов. При этом формируется сигнал на соответствующем выходе регистра 12, который переключает соот73

ветствующий элемент памяти блока 14. Выходной сигнал этого элемента памяти включает соответствующий светодиод блока 15 индикации. Данный информационный импульс проходит также через элемент ИЛИ 4 и устанавливает в исходное состояние блок 5 задержки, на выходе которого при

этом устанавливается высокий уровень напряжения, который устанавливает в нулевое состояние двоичный счетчик 9 и делитель 7 частоты. Блок 5 начинает отсчитывать задержку. После установления на его выходе низкого уровня напряжения начинается развертка импульсов на выходах регистра 11.

Следующий выходной информационный

импульс селектора 2 фронтов производит запись сигнала в соответствующий разряд регистра 12. Под соответствующим разрядом регистра -1 2 понимается такой его разряд, который связан

с тем выходом регистра 11, формирование импульса на котором совпадает по времени с данным перепадом сигнала воспроизведения. Сигнал с выхода соответствующего разряда регистра 12 переключает соответствующий элемент памяти блока 14. Выходной сигнал этого элемента памяти включает соответствующий светодиод блока 15 индикации. Данный информационный импульс сбрасывает в исходное состояние блок 5 задержки, после: чего двоичный счетчик 9 и делитель 7 частоты запираются на время задержки, вырабатьгоаемое блоком 5 в нулевом состоянии.

Таким образом, регистр 12 осуществляет формирование сигналов текущего значения фазовых искажений сигнала воспроизведения, а блок 14 элементов памяти запоминает на опреде- . ленное время, удобное для наблюдения, эти сигналы, т.е. все значения фазовых искажений, в том числе и максимальную их величину, В результате

блок индицирует все значения фазовых искажений за определенный промежуток времени и удвоенная максимальная величина этих искажений будет определяться протяженностью ciee- тящейся пачки светодиодов светодиодной щкалы 15.

Максимальная величина фазовой ошибки вычисляется путем умножения числа светодиодов в светящейся

.,пачке на весомость одного светодио- да шкалы Весомость одного светодио- да в светодиодной шкале 15j т,е, длительность импульсов на выхоДах регистра 11, равна длительности периода выходного сигнала делителя 7 частоты т.е. периоду переключения счетчика 9,

Поскольку фазовая ошибка обычно I не превышает от тактового ннтерззала сигнала воспроизведения, то.для повышения точности измерения {ее, в частности для повышения разре- 1 шающей способности устройства, нача- ло измерения сдвигается вправо на временной оси от момента поступления информационного импульса. При этом на соответствуюшуи величину ; увеличивается частот.а выходного сиг- : нала делителя 7 частоты5 чтобы сере- : дина развертки совпадала с номиналь- ньм местоположением следующего пере- : пада сигнала воспроизведения, Контролируемый сигнал воспроизведения по структуре состоит из : набора интервалов( равных или кратньк тактовому интервалу сигнала вос- : произведения.

Если следуюашй выходной импульс (второй импульс на диаграмме 2, фиг. 3) селектора.2 фронтов поступил tepeз интервал, больший чем тактовый, то после, предыдуще х о инфррма7ДИОННОГО импульса (пе-ргвого на диаграмме 2 фиг 2) развертка импульсов на выходах регистра 11 выполнится полностью и импульсом, сформули- руемьи на последнем выходе (диаграмма 4., фиг„ 2) регистра 11, переключится в единичное состояние триггер 3, При зтом выходной сигнал триггера 3 проходит через элемент ИЛИ 4 к запирает.в исходном состоянии блок . 5 задержки, выходкой сигнал которого

при этом запирает в нулевом состоя- НИИ двоичный счетчик 9 и делитель 7 частоты.

Блек 14 элементов памяти периодически сбрасывается в нулевое состояние выходным импульсом формироП 6736

вателя 13, который формирует короткий по длительности импульс в мо-. мент каждого положительного пере- с пада уровней выходного сигнала делителя 8 частоты.

Формула изобретения

10 Устройство для контроля фазовых искажений сигнала воспроизведения, содержащее генератор эталонной частоты, триггер, блок индикации и последовательно соединенные двоичный

15 счетчикJ дешифратор и первый регистр, управляющий вход которого объединен со счетным входом двоичного счетчика, а выходы соединены с информационными входами второго

20 регистра, управляющим входом соединенного через селектор фронтов с входной шиной сигнала воспроизведения, отличающе еся тем, что, с целью обеспечения контроля

25 максимальной величины фазовых искажений сигнала воспроизведения, Б него введены блок элементов памяти, два делителя.частоты, формирователь импульсов, блок задержки

30 и элемент ИЛИ, блок элементов памяти включен между выходами второго регистра и входами блока индикации, выход генератора эталонной частоты соединен с одним входом блока задерж25 ки, через первый делитель частоты со счетным входом двоичного счетчика и входом первого регистра, а через последовательно соединенные второй делитель частоты и формирователь

40 импульсов - с установочным входом блока элементов памяти, выход блока задержки соединен с установочными входами двоичного счетчика и первого делителя частоты, выход селектора

с фронтов соединен с одним входом триггера и через элемент ИЛИ с другим входом блока задержки, один выход первого регистра соединен с другим входом триггера, выход которого

,. подключен к второму входу элемента ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля воспроизведения цифровой информации с носителя магнитной записи | 1985 |

|

SU1282213A1 |

| Устройство для контроля аппарата магнитной записи | 1988 |

|

SU1607012A1 |

| Устройство для контроля многоканального аппарата магнитной записи | 1986 |

|

SU1420615A1 |

| Устройство для контроля воспроизведения цифровой информации с носителя магнитной записи | 1986 |

|

SU1408456A1 |

| УСТРОЙСТВО ДЛЯ СИНТЕЗА РЕЧЕВЫХ СИГНАЛОВ | 1991 |

|

RU2020608C1 |

| Способ маркирования информационных комбинаций в системах последовательной записи с двухчастотным кодированием и устройства записи и воспроизведения для его осуществления | 1987 |

|

SU1543445A1 |

| Устройство магнитной записи и воспроизведения двухчастотных сигналов | 1983 |

|

SU1129648A1 |

| Устройство для контроля синхронизма воспроизведенных сигналов | 1988 |

|

SU1585833A1 |

| Многокоординатное устройство для управления | 1989 |

|

SU1777121A2 |

| Устройство для индикации расхода магнитной ленты | 1981 |

|

SU1007132A1 |

Изобретение относится к приборостроению и может быть использовано в аппаратуре магнитной записи для оценки максимальной фазовой ошибки цифрового сигнала воспроизведения. Для этого блоком 14 памяти запоминают все текущие значения фазовой ошибки, формируемые регистром 12, с последующей индикацией блоком 15. Начало развертки, т.е. поочередного формирования импульсов на выходах регистра 11, связанных с регистром 12, сдвинуто с помощью элемента 5 задержки относительно выходных информационных импульсов селектора 2 фронтов воспроизводимых импульсов устройства на величину, при которой середина развертки совпадает с номинальным положением во времени следующего тактового перепада сигнала воспроизведения, а длительность развертки, задаваемой периодом сигнала делителя 7 от генератора 6, устанавливается немного превышающей удвоенное значение максимальной фазовой ошибки. 2 ил. ( С

Фиг. 2

| Устройство для контроля фазовыхиСКАжЕНий СигНАлА ВОСпРОизВЕдЕНия | 1979 |

|

SU853671A1 |

| G | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для контроля воспроизведения цифровой информации с носителя магнитной записи | 1985 |

|

SU1282213A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1988-07-30—Публикация

1987-01-28—Подача