Изобретение относится к электроизмерительной технике и может быть йспользрв ано в измерителе разности низких частот.5

Известно устройство дли измерения отклонения частоты от номинального значения, содержащее блок измерения абсолютного значения отклонения периода, счетчик,формирующий код откло-10 нения и блок сравнения кода счетчика с кодом регистра максимального отклонения 1 .

Недостатком устройства является наличие в блоках линий защержки, огра-.з ничивающих диапазон рабочих частот.

Известно устройство для цифрового измерения разности частот электрических колебаний.

Устройство построено на принципе 20 дискретного измерения фазового сдвига между двумя сигнсшами с дальнейшей обработкой в реверсивном счетчике и получении цифрового результата, пропорционгшьного разности частот. 25 этих сигналов.

Устройство содержит реверсивный счетчик, входы которого связаны с выходнымк клеммами через логические схемы ИЛИ, временные селекторы, триг- О

гер управления, формирователи импульсов и выходные триггеры, а выход - с цифроЪым индйкатором, формирователь временного измерительного .интервала, генератор эталонных импульсов, компаратор длительности пачки, образованный счётчйьсбм Т1мпу льс6вТ дешифраторами, элементами задержки и схемой НЕ.

В устройстве применены элементы задержки, расчитанные на определенные величины (1/6 Т2, 5/6 Tg, 1/2 Tg, где Tj, - период сигнала второго канала) 2 .

Недостатком этого устройства является наличие линий задержки, существенно сужающих частотный диапазон сигналов, так как для нормальной работы требуется ва.рьированйе величинами задержек при изменении частоты. Кроме того, устройство не позволяет производить накопление peзyльтata измерения для повышения точности измерения.

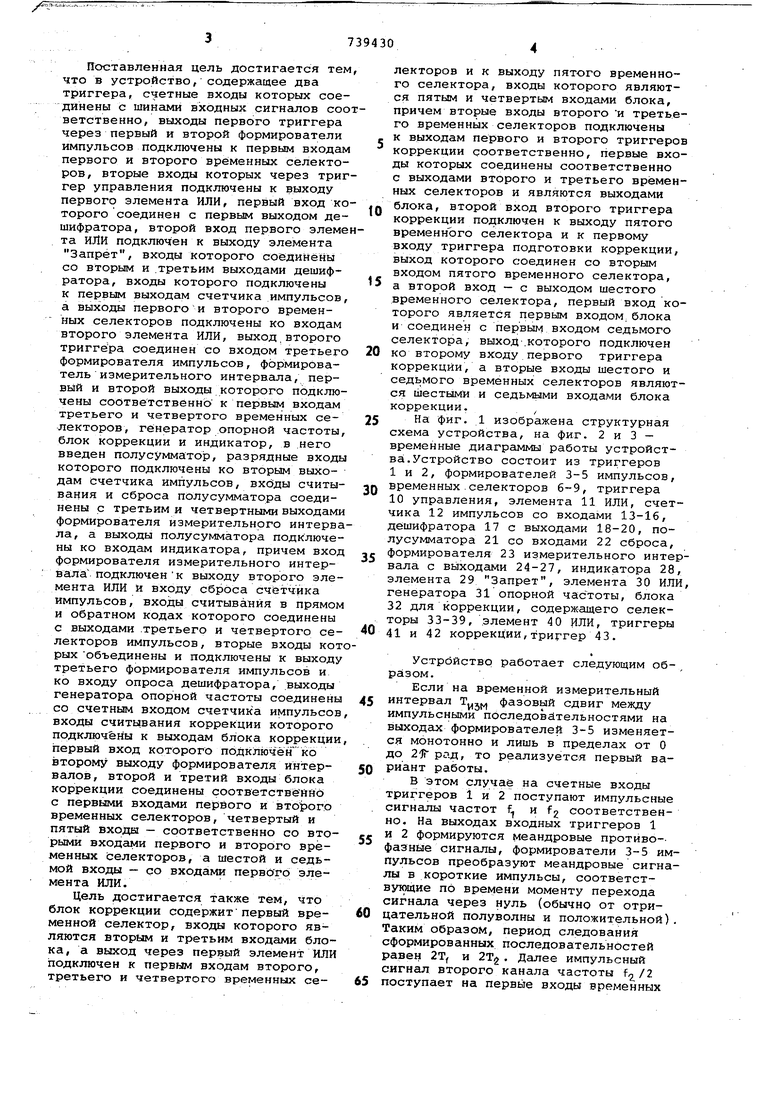

Цель изобретения - расширение частотного диапазона входных сигнешов, при этом дополнительно достигается повышение точности измерения разности частот электрических колебаний. Поставленная цель достигается тем что в устройство,содержащее два триггера, счетные входы которых соединены с шинами входных сигналов соо ветственно, выходы первого триггера через первый и второй формирователи импульсов подключены к первым входам первого и второго временных селекторов, вторые входы которых через триг гер управления подключены к выходу первого элемента ИЛИ, первый вход ко торого соединен с первым выходом дешифратора, второй вход первого элеме та ИЛИ подключен к выходу элемента Запрёт, входы которого соединены со вторым и .третьим выходами дешифратора, входы которого подключены к первым выходам счетчика импульсов а выходы первого и второго временных селекторов подключены ко входам второго элемента ИЛИ, выход,второго триггера соединен со входом третьего формирователя импульсов, формирователь измерительного интервала, первь1й и второй выходы которого подклю чены соответственно к первым входам третьего и четвертого временных селекторов, генератор опорной частоты блок коррекции и индикатор, в него введен полусумматор, разрядные входы которого подключены ко вторым выходам счетчика импульсов, вхбды считывания и сброса полусумматора соединены с третьим и четвертными выходами формирователя измерительного интерва ла, а выходы полусумматора подключены ко входам индикатора, причем вход формирователя измерительного интервала подключен к выходу второго элемента ИЛИ И входу сброса счетчика импульсов, входы считывания в прямом и обратном кодах которого соединены с выходами .третьего и четвертого селекторов импульсов, вторые входы кот рых объединены и подключены к выходу третьего формирователя импульсов и ко входу опроса дешифратора, .выходы генератора опорной частоты соединены со счетным входом счетчика импульсов входы считывания коррекции которого подключены к выходам блока коррекции первый вход которого подключён ко второму выходу формирователя интервалов, второй и третий входы блока коррекции соединены соответствёйНо с первыми входами первого и второго временных селекторов, четвертый и пятый входш - соответственно со вторыми входами первого и второго временных селекторов, а шестой и седьмой входы - со входами первого элемента ИЛИ. Цель достигается также тем, что блок коррекции содержитпервый временной селектор, входы которого являются вторым и третьим входами блока, а выход через первый элемент ИЛИ подключен к первым входам второго, третьего и четвертого временных се739430лекторов и к выходу пятого временного селектора, входы которого являются пятым и четвертым входами блока, причем вторые входы второго и третьего временных селекторов подключены к выходам первого и второго триггеров коррекции соответственно, первые входы которых соединены соответственно с выходами второго и третьего временных селекторов и являются выходами блока, второй вход второго триггера коррекции пoJCtключeн к выходу пятого временнЪго селектора и к первому входу триггера подготовки коррекции, выход которого соединен со вторым входом пятого временного селектора, а второй вход - с выходом шестого временного селектора, первый вход которого является первым входом,блока и соединен с первым входом седьмого селектора, выход .которого подключен ко второму входу первого триггера коррекции, а вторые входы шестого и седьмого временных селекторов являются шестыми и седьмыми входами блока коррекции. , На фиг. 1 изображена структурная схема устройства, на фиг. 2 и 3 - временные диаграммы работы устройства. Устройство состоит из триггеров 1 и 2, формирователей 3-5 импульсов, временных.селекторов 6-9, триггера 10 управления, элемента 11 ИЛИ, счетчика 12 импульсов со входами 13-16, де-шифратора 17 с выходами 18-20, полусумматора 21 со входами 22 сброса, формирователя 23 измерительного интервала с выходами 24-27, индикатора 28, элемента 29 Запрет, элемента 30 ИЛИ, генератора 31 опорной частоты, блока 32 для коррекции, содержащего селекторы 33-39, .элемент 40 ИЛИ, триггеры 41 и 42 коррекции,триггер 43. Устройство работает следующим образом. Если на временной измерительный интервал Фазовый сдвиг между импульсными последовательностями на выходах формирователей 3-5 изменяется монотонно и лишь в пределах от О до 2Jf рад, то реализуется первый вариант работы. В этом случае на счетные входы триггеров 1 и 2 поступают импульсные сигналы частот fj и fg соответственно. На выходах входных триггеров 1 и 2 формируются меандровые протйво-фазные сигналы, формирователи 3-5 импульсов преобразуют меандровые сигналы в короткие импульсы, соответствуквдие по времени моменту перехода сигнала через нуль (обычно от отрицательной полуволны и положительной). Таким образом, период следования сформиров анных последов атель нос те и равен 2т, и . Далее импульсный сигнал второго канала частоты поступает на первые входы временных

селекторов 6 и 7, 35 и 34, а сигнал первого канала частоты f//2 на вход временных селекторов 8 и 9 и одновременно на вход опроса 18 потенциальноимпульсного дешифратора 17. В зависимости от фазы управляющего напряжения на вторых входах временных селекторов 6 и 7, 35 и 34, поступающего с прямого и инверсного выходов тригге;ра

10управления, импульсные последовательности частоты f2/2, сдвинутые

на f рад, пропускаются через схему

11ИЛИ на вход сброса счетчика ичпульсов 12 и на вход формирователя

23 временного измерительного интервала, который состоит из делительных декад и схемы автоматики, С прямого и инверсного выходов 24 и 25 первого триггера декадного делителя частоты управляющее напряжение поступает на вторые входы временных селекторов .8 и 9, которые в зависимости от фазы этого напряжения пропускают импульсы частоты f/ /2 на вход считывания счетчика 12, если в прямом коде - на вход 13, если в обратном - на вход 14. С выходов 26 и 27 схемы автоматики формирователя 23 импульсы с периодом Tyj поступают на входы 22 сброса полусумматора 21, а на вход считывания счетчика 12 с генератора 31 поступают импульсы, следующие с периодом Tj в течение времени между двумя срабатывающими импульсами. Информация о фазовом рассогласовании (двоичный код) в параллельной форме снимается со счетчика 12 в моменты прихода импульсов первого канала частоты f /2 и поступает на. обработку в накопительный полусумматор 21.

Операция вычитания двоичных кодов осуществляется в накопительном полусумматоре 21 за счет инверсии кода одного из слагаемых и присвоения знака каждому слагаемому. Двоичный код в накопительном полусумматоре 21 в конце измерительного периода пропорционален разности частот входных сигналов, то есть N Af К, где К - коэффициент пропорциональности.

Если дополнительно Тц fj T/-10 , то N д f Ю . Причем величина кода разности частот зависит от величины измерительного интервала, что позволяет различать близкие по своему значению частоты..

Если за время измерительного интервала Tyj, разность фаз двух входных сигналов достигает значений близких к О или , то реализуется второй вариант работы. Информационные выходы счетчика 12 соединены с потенциальными входами потенциально-импульсного дешифратора 17, на вход опроса которого поступают импульсы первого канала частоты f, /2. В момент прихода импульса опроса на импульсных выходах 18-20 появляется импульс

причем, если в этот момент число в счетчике 12 меньше минимального порога срабатывания N N,-, , то импульс ;появится на выходе 18, если К,; N N, то импульс - на выходах 18 и 19, если N , то импульс - на выходах 18-20.

Следовательно, если число в счетчике 12 в момент опроса потенциальноимпульсного дешифратора 17 N ,

то импульс с выхода 18 через логический элемент 29 Запрет, схему 30 ИЛИпоступает на счетный вход триггера 10 управления, который переключает селекторы 6, 7, 35, 34 и меняет фазы сигналов второго канала на f, далее процесс изменения фазового сдвига продолжается до следующего переключения. Одновременно, импульс с выхода схемы 29 Запрет поступает в устройство

32 коррекции результата на вход временного селектора 36 управления коррекцией и в зависимости от фазы управляющего напряжения на втором его входе устанавливает триггер 43 в состояние единица, который .своим выходом

открыв.ает временной селектор 33 коррекции. Через временной селектор 33 коррекции проходит сигнал с выхода схемы 40 ИЛИ на вход 15 считывания данных коррекции в прямом коде счетчика 12. Таким образом, осуществляется коррекция на величину равную Tg /Тэт. Импульс коррекции с выхода селектора 33 коррекции одновременно устанавливает триггер 43 в состояние ноль.

Если число в счетчике 12 в мо.мент опроса,потенциально-импульсного. дешифратора 17 N , то импульс с выхода элемента 29 через схему

30 ИЛИ, триггер 10 управления и временные селекторы 6, 7, 35, 34 переключает фазу сигналов второго канала на Jf и одновременно через временной селектор 36 управления коррекцией установит триггер 43 в состояние единица. Первый же импульс противофаз:ной последовательности через временной селектор 38 установит триггер 41 в единицу и одновременно закроет

триггер 42, второй импульс с выхода схемы 40 ИЛИ через временной селектор 39 коррекции поступает на вход считывания данных коррекций в обратном коде 16 и одновременно устанавливает

в ноль триггер 41, так осуществляется коррекция на величину В N,Qp -Тг /Тзт- .

Если число в счетчике 12 в момент опроса потенциально-импульсного дешифратора 17 М„,(„ N Мгг,ах,то иа выходе элемента 29 Запрет импульса не будет и, следовательно, осуществляется первый вариант работы устройства.

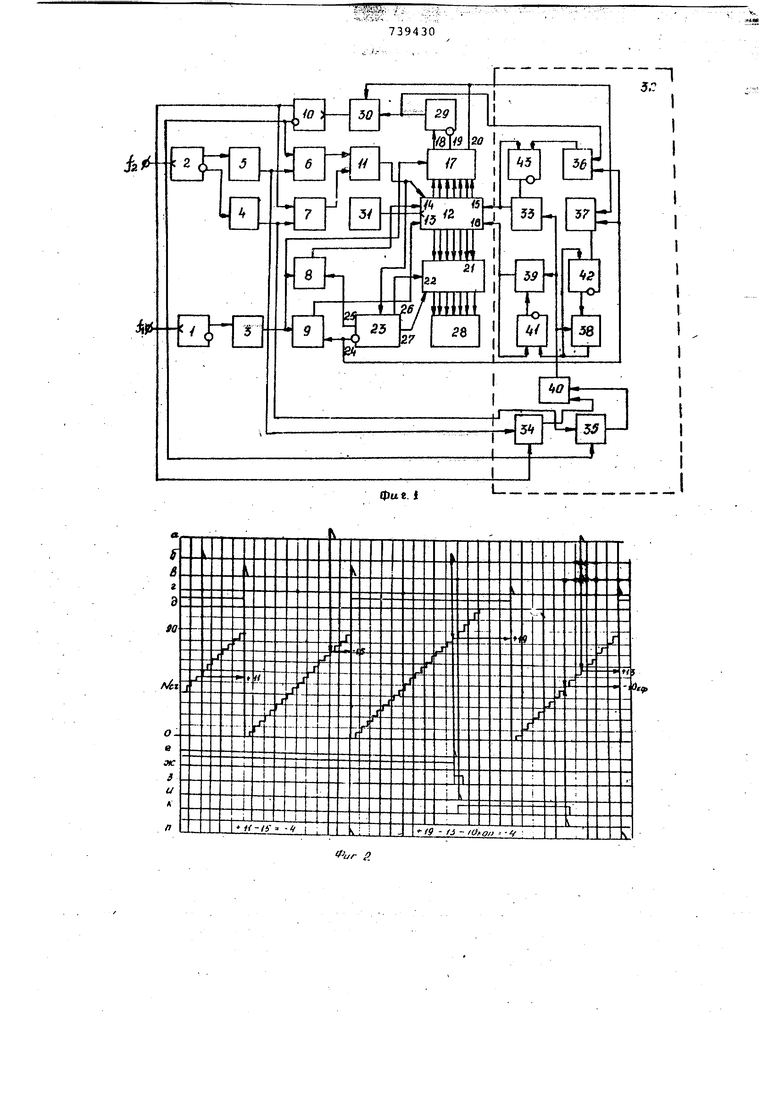

На фиг. 2 приведены эпюры сигналов в различных точках схемы, отмеченных буквами (а,б,в,...) для случая f, 7 (т, Tj, ) . Для наглядности выбрано оп ределенное соотношение между Т. и TL (Та,/Туг 20) и в соответствующем масштабепоказаны значения кодов в счетчике 12 импульсов (Например: +1, -15,...). Временные диаграммы (см. фиг. 3) поясняют работу предлагаемого устрой ства при соотношении f, fj . ( Тг ) Как видно из диаграммы, устройствр позволяет накапливать результат измерения за п периодов частоты, что повышает точность измерения разности близких частот. Формула изобретения 1. Устройство для цифрового измерения разности частот электр ч ских колебаний, содержащее два триггера, счетные входы которых соединены с ши нами входных сигналов соответственно, выходы первого триггера через первый и второй формирователи импуль сов подключены к первым входам перво го и второго временных селекторов, входы которых через триггер управления подключены к выходу перво го элемента ИЛИ, первый вход которого соединен с первым выходом дешифра тора, второй вход hepBoro элемента ИЛИ подключен к выходу злемента Запрет, входы которого соединены со вторым и третьим выходами дешифратора, входа которого подключены к первым выводам счетчика импульсов, а выходы ггёрвого и второго временных селекторов подключены ко ШШЙНЙ втЬрого злемента ИЛИ, выход второго триггера соединен со входом третьего формирователя импульсов; формирователь измерительного интервала, первый и второй выходы которого подключены соответственно к первым входам третьего и четвёртого временных селекторов, генератор опорной частоты, блок коррекции и индикатор, о т л и ч ающе е с я тем, что, с целью расширения частотнйго дйапазсзяа вход ных сигналов и повышения точности измерения, в него введен полусумматор, разрядные входы которого подклю чены ко вторым выходам счетчика импульсов, входы считывания и сброса полусумматора соединены с третьим и четвертыми выходами формироёателя измерительного интервала, а выходы полусумматора подключены ко входам индикатора/причем вход формирователя измерительного интервала подключен к выходу второго элемента ИЛИ, и к счетному входу счетчика импульсов, входы считывания в прямом и обратном кодах которого соединены с выХодами третьего и четвертого-селекторов импульсов, вторые входы которых объединены и подключены к выходу третьего формирователя импульсов и ко входу опроса дешифратора, выходы генератора опорной частоты соединены со счетным входом счетчика импульсов, входы считывания коррекции которого подключены к выходам блока коррекции, первый вход которого подключен ко второму выходу формирователя измерительных интервалов, второй и третий входы блока коррекции соединены соответственно с первыми входами первого и второго временных селекторов, четвертый и пятый входы - соответственно со вторыми входами первого и второго временных селекторов, а шестой и седьмой входы. - со входами первого эл емента ИЛИ. 2. Устройство по п. 1, о1;ли4 а К1 ад е ее я тем, что блок коррекции содержит первый временной селектор, входы которого являются вторым и третьим входами блока, а выход через первый злемент ИЛИ подключен к первым входам второго, третьего и четвертого временных селекторов и к выходу пятого временного селектора, входы которого являются пятьом и четвертым входами блока, причем вторые входы второго и третьего временных селекторов подключены к выходам первого и второго триггеров коррекции . соответственно, первые входы которых соединены соответственно с выходами второго и третьего временных селекторов и являются выходами блока, второй вход второго триггера коррекции подключен к выходу пятого временного селектора и к первому входу TpTirrepa подготовки коррекции, выход которого соединен со вторым входом пятого временного селектора, а второй вход - с выходом шестого временного селектора, первый вход которого является первым входом блока и соединен с первым входом седьмого селектора, выход которого подключен ко второму входу первого триггера коррекции, а вторые входы шестого и седьмого временных селекторов являются шестыми и седьмыми входами блока коррекции. Исто 1ники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 535522, кл. G 01 R 23/10. 2. Авторское свидетельство СССР 495616, клГС ОТ R 23/10, 15,12.75.

I

фие. i

§

vta Ч) N

04/ С

| название | год | авторы | номер документа |

|---|---|---|---|

| Многопрограммный регулятор температуры | 1983 |

|

SU1087951A1 |

| Устройство для считывания графической информации | 1982 |

|

SU1164752A1 |

| Устройство для измерения частоты гармонического сигнала | 1987 |

|

SU1525607A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1990 |

|

RU2020565C1 |

| Устройство для считывания графической информации | 1985 |

|

SU1372343A1 |

| Цифровой частотомер | 1981 |

|

SU1049820A1 |

| Устройство для считывания графической информации | 1980 |

|

SU1038955A2 |

| Цифровой измеритель динамических температурно-частотных характеристик кварцевых резонаторов | 1981 |

|

SU976402A1 |

| Запоминающее устройство | 1983 |

|

SU1115105A1 |

| УСТРОЙСТВО ДЛЯ РЕГИСТРАЦИИ БЫСТРОМЕНЯЮЩЕГОСЯ ПРОЦЕССА | 1990 |

|

RU2007756C1 |

Авторы

Даты

1980-06-05—Публикация

1977-06-20—Подача