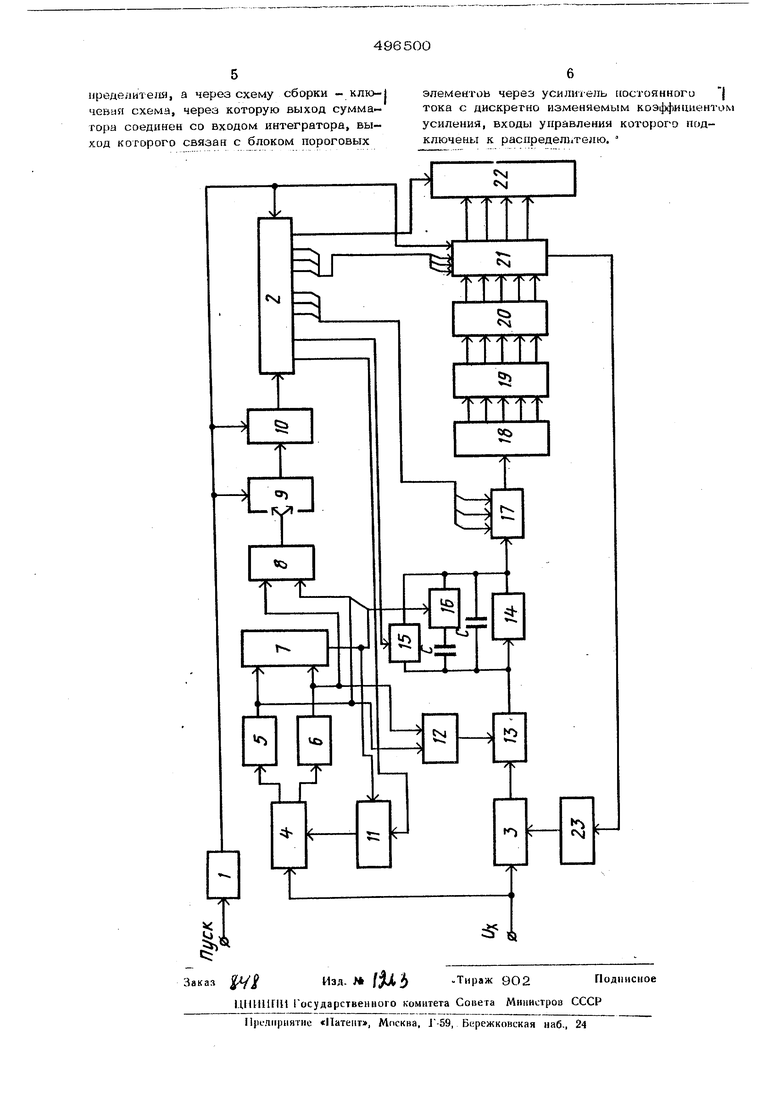

Изобретение относится к области электроизмерительной техники. Известны интегрирующие цифровые воль метры, содержащие сумматор измеряемо1о и компенсирующего напряжений, интегратор блок выделения периода помехи, распредеШ1тель, задатчики временных тактов, ключевые схемы, блок пороговых элементов, преобразователь Код-напряжение и логические схемы. Цель изобретения - повьпиение точности измерения при максимально допустимой амплитуде помехи и быстродейстьия при повышении частоты помехи. S-iO достигается тем, что в предложенном устройстве к выходам задатчиков временнрях тактов, входы которых подключены к выходам блока выделения периода помехи связанного через переключатель с входом прибора, подсоединены: схема И-ИЕ, выход которой связан с входом удвоения крутизны преобразования интегратора, а через три1Ч ер - с входом Разрешение запуска блока выделения периода помехи; через схе му сборки задних фронтов импульсов и триггер со счетным входом - формирователь строб-импу тьсов, выход которого соединен со входом распределителя, а через схему сборки - ключевая схема, через которую выход сумматора соединен со входом ивтетратора, выход которого связан с блоком поро1овых элементов через усилитель по- стоянно1о тока с дискретно изменяемым коэффициентом усиления, входы уиравлуния которого подключены к распределителю. На чертеже изображена структурная схема вольтметра. Вольтметр содержит схему 1 сброса, распределитель 2, сумматор 3, блок 4 выделения периода помехи, задатчики 5, в временных тактов, схему 7 И-НЕ, ( хему 8 сборки, триггер 9, схему 10 формирования строб-импульсов, триггер 11, схему 12 ИЛИ, ключевую схему 13, инге1)атор, состоящий из усилителя 14 постоянного ччжа, ключевых схем 15, 16 и равных по величине конденсаторов С, ус:илитель 17 постоянного тока (УНТ) с дискретно измен1и: мым коэффициентом усиления, блок J8 ii;i - роговых элементов, схему 19 выборки старшего сработавшего порогового элемента, шифратор 20, блок 21 запоминающих устройств (ЗУ), блок 22 цифрового отсчета, преобразователь 23 Код-напряжение Прибор работает следующим образом. Под воздействием импульса Пуск осуществляется возврат в исходное положение триггера 9, блока ЗУ 21, триггера 11, с выхода которого выдается сигнал Запрет на запуск блока 4 выделения помехи. Импульсом Пуск одновременно запускается схема 10 формирования стробимпульса, по заднему фронту которого срабатывает ключевая схема 15, разряжаю|Щая конденсатор в цепи обратной связи интегратора и устанавливающая распределитель 2 в положение, соответствующее оценк первого разряда. Распределитель 2 устанав ливает значение коэффициента усиления УПТ 17, необходимое для оценки первого разряда. Срабатывает триггер 11, снимая сигнал Запрет с блока 4 выделения пери да помехи, и сигналы с его выходов поступают на входы задатчиков 5, 6 временныхтактов. Сигнал на запуск задатчика 5 временны тактов будет выдан в момент начала положительного полупериода сигнала помехи, а в момент начала отрицательного полупериода будет выдан сигнал на запуск задатчи- ка 6 тактов, и начнется второй такт интегрирования. По заднему фронту второго временного такта через схему 12 ИЛИ выдается сигна и ключевая схема 13 переходит в состояни Выключено. По этому же фронту через схему 8 сбор ки выдается сигнал, вызывающий повторнее сршбатывание трип-ера 9, на его выход появляется сигнал, который запускает схем Ю формирования строб-импульса. В момент окончания второго такта напряжение на выходе интегратора не зависит от периодической помехи. I I Перепись показаний блока пороговых элементов, подключенного к выходу УПТ 17 производится строб-импульсом через схему 19 выборки старшего сработавшего порогового элемента и шифратор 2О в старший разряд блока ЗУ 21. Блок 21 через преобразователь Код-напряжение включает ком- пенсируюшее напряжение, соответствующее коду старшего разряда. По заднему фронту строб-импульса происходит разряд емкости интегратора, перевод распределителя 2 на оценку следующего разряда. В свою очередь распрс;и лнт8ль 2 изменяет величину коэффициента усиления УПТ 17 для оценки еле- дающего разряда, срабатывает триггер 11, в результате чего сигнал Запрет с блока 4 выделения периода помехи снимается. Оценка следующих разрядов происходит аналогично. После оценки последнего разряда по заднему фронту строб-импульса происходит включение блока 22цифрового отсчета, : В случае наводки от сети 50 rii информация о периоде помехи может быть выде- : лена непосредственно из сети. Если частота помехи увеличивается, то возможно перекрытие тактов интегрирования. В этом случае для сохранения помехоустойчивости, крутизну интегратора на время перекрытия тактов необходимо удвоить. Для этого с выхода схемы 7 И-НЕ выдается сигнал, который переводит ключевую схему 16 в состояние Выключено, один из конденсаторов С отключается, в результате чего крутизна интегратора на время перекрытия тактов удваивается. Одновременно тот же сигнал вызывает срабатывание триггера 11, и на блок 4 выделения периода помехи выдается сигнал Запрет на запуск, который снимается только в начале следующего такта измерения. По заднему фронту задатчика временного такта через схему 8 сборки выдается сигнал, вызывающий срабатывание триггера 9. По этому же фронту сигналом с выхода схемы 7 И-НЕ ключевая схема 16 переводится в состояние Включено, и интегрирование продолжается с первоначальной крутизной. Формула изобретен ия Цифровой интегрирующий вольтметр, содержащий сумматор измеряемого и компенсирующего напряжеЕшй, интегратор, блок выделения периода помехи, распределитель, задатчики временных тактов, ключевые схемы, блок пороговых элементов, преобразователь Код-напряжение и логические схемы, отличающийся тем, что, с целью повыщения точности измерения при максимально допустимой амплитуде помехи и быстродействия при повышении частоты помехи, в нем к В1 1ходам задатчиков временных i-актов, входы которых подключены к выходам блока выделения периода помехи, связанного через переключатель с входом прибора, подсоединешл: схема И-НЕ, выход которой связан с Входом удвоения крутизны преобразования интегратора, а через тригг-ер - с входом Разреигение запуска блока выделения периода помехи; через схему сборки задних фронтов импульсов и триггер со счетным входом - формирователь строб-импульсов, выход которого соединен со входом рас

| название | год | авторы | номер документа |

|---|---|---|---|

| Измеритель времени установления выходного напряжения цифроаналоговых преобразователей | 1984 |

|

SU1236612A1 |

| УСТРОЙСТВО ДЛЯ РАННЕЙ ДИАГНОСТИКИ ПАТОЛОГИЧЕСКИХ НАРУШЕНИЙ ЧАСТОТЫ СЕРДЕЧНОГО РИТМА | 1993 |

|

RU2082314C1 |

| Оптикоэлектронный координатор для автоматического вождения мобильных агрегатов | 1986 |

|

SU1378086A1 |

| Устройство для измерения времени установления выходного сигнала цифроаналогового преобразователя | 1990 |

|

SU1716601A2 |

| Устройство для динамической балансировки лучом лазера роторов | 1983 |

|

SU1130753A2 |

| Устройство для синхронизации системы управления преобразователем | 1988 |

|

SU1658316A1 |

| Аналого-цифровой преобразователь | 1978 |

|

SU748863A1 |

| УСТРОЙСТВО ДЛЯ РАЗЛИЧЕНИЯ ЛИНЕЙНО-ЧАСТОТНО-МОДУЛИРОВАННЫХ СИГНАЛОВ | 1984 |

|

SU1841016A1 |

| Устройство для автоматической разрывно-импульсной идентификации дактилоскопических отпечатков | 1959 |

|

SU133278A1 |

| РАДИОДАТЧИК ВЫСОТЫ | 2007 |

|

RU2336540C1 |

Авторы

Даты

1975-12-25—Публикация

1972-01-05—Подача