(54) ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения взаимной корреляционной функции | 1983 |

|

SU1108463A1 |

| Генератор многомерных случайных величин | 1982 |

|

SU1084791A1 |

| Устройство для медианной фильтрации двумерных массивов | 1987 |

|

SU1524067A1 |

| Устройство для моделирования систем массового обслуживания | 1986 |

|

SU1388886A1 |

| Вычислительное устройство | 1982 |

|

SU1040493A1 |

| Коррелометр | 1979 |

|

SU783799A1 |

| Генератор случайного процесса | 1983 |

|

SU1111159A1 |

| Устройство для распознавания типа движущихся вагонов | 1982 |

|

SU1050947A1 |

| Устройство для умножения частоты следования импульсов | 1986 |

|

SU1410027A1 |

| Устройство для моделирования систем массового обслуживания | 1984 |

|

SU1275459A1 |

1

Изобретение относится к вычислительной j технике и может быть использовано в уст|ройствах обработки информации.

i Известны устройства, выполняющие ариф1метнческие операции, содержащие , Дешифраторы, элементы задержки, счетчик ;результатов, генератор тактовых импульсов, 1 выход которого соединен с первым входом ;первого элемента И, выход которого соединен раздельным входом первого счетчика, :разрядные входы которого подключены к вы. I-ходам первой группы элементов И первые входы которых соединены с регистром, а вторые входы - к выходу первого счетчика и к раздельному входу второго счетчика, выход которого через первый дешифратор подключен ко второму входу первого р&лемента И и к первому ,входу второго элемента И, выход которого подключен к перi вым входам второй группы элементов и не- посредственно, а через первый элемент за- I держки - к первому входу счетчика резупь- татов, выходы которого соединены со вто,рыми входами. Второй группы элементов И,

выходы которых подключены к разрядным :входам второго счетчика.

Такие устройства, однако, могут i нять tonbKo отдельные арифметические оп« ,рации.

I Целью изобретения является расширение I функциональных возможностей устройства, I Это достигается тем, что устройство со Iдержит допол)Штельный элемент И, элемент 1ИЛИ и блок памяти, вход которого соеди |нен с первым входом счетчика результатов, i второй вход которого подключен к выходу ; первый вход которого соединен с выходом

I первого элемента И, втор ей вход - с выхо дом дополнительного элемента И и с раздельным входом третьего счетчика, разряд ные входы которого соединены с блоком, п мяти, в выход через второй дешифратор со4 единен со вторым входим второго элемента

Икс первым входом допол1ютельного эле

: мента И второй вход которого через второй элемент задержки соединен с выходом генр«

; ратора тактовых импульсов.

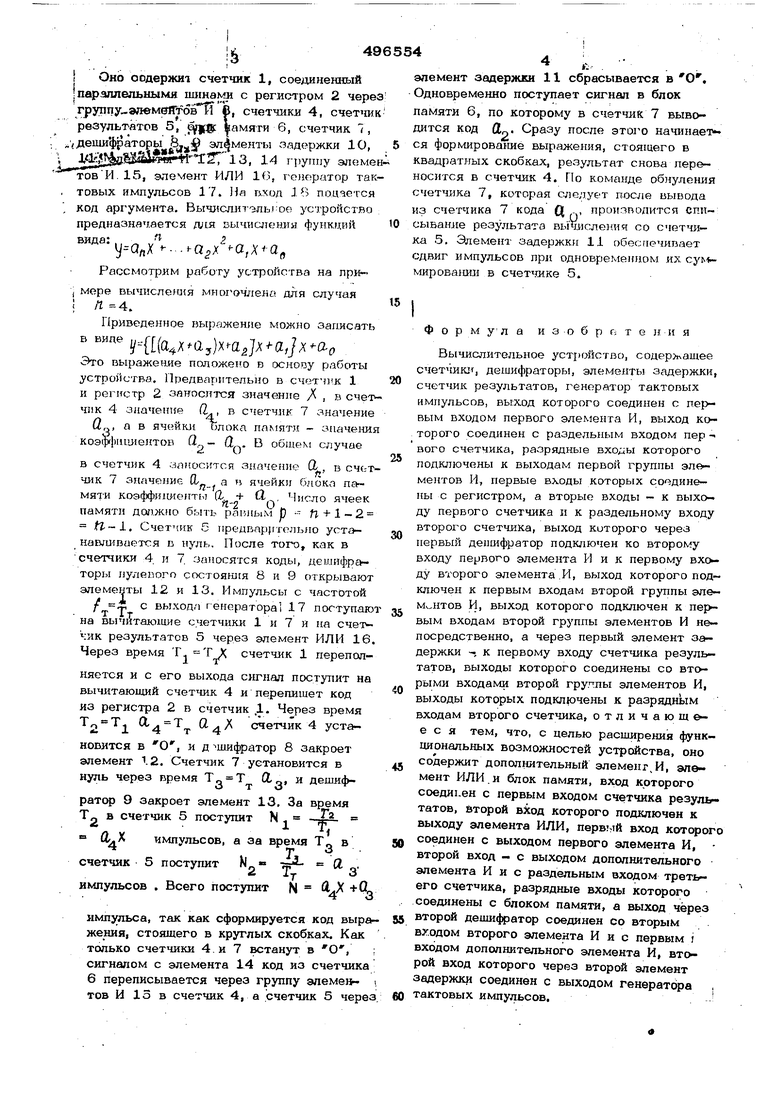

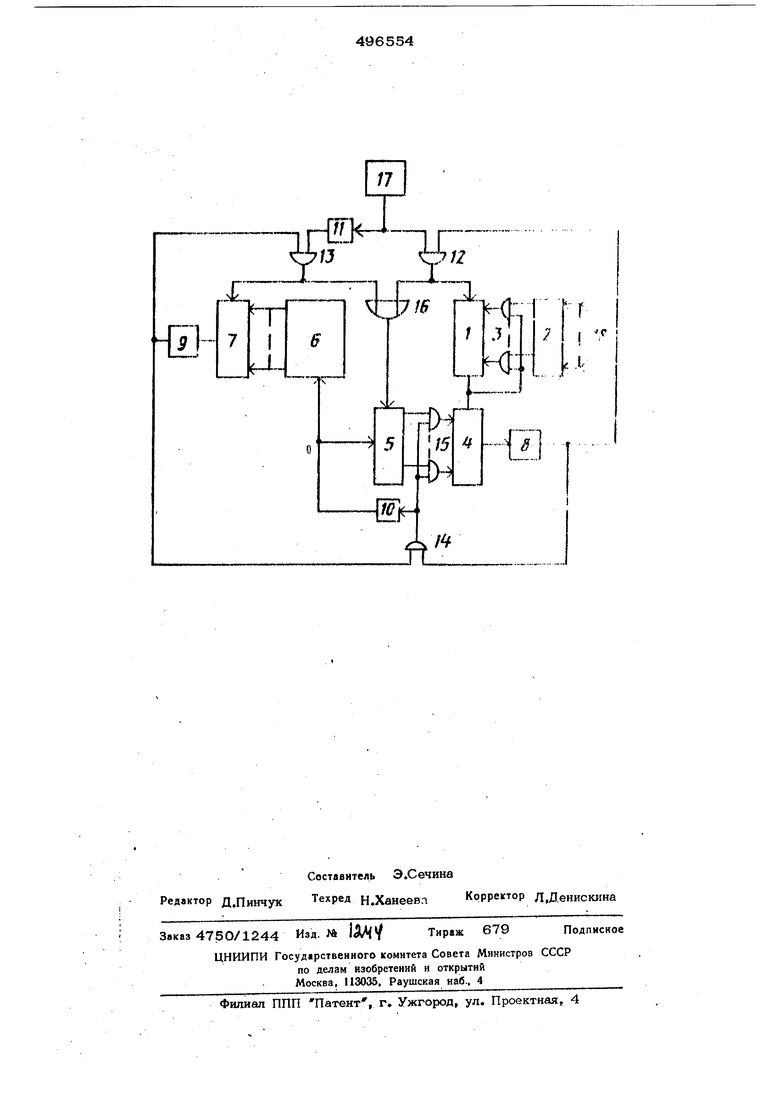

На чертеже представлена схема ycTpoflrГства.. I Оно оодержит счетчик 1, соединенный I параплельнымя шинами с регистром 2 через группу элемеЯГтов И в, счетчики 4, счетчик результатов 5, ё намяти 6, счетчик 1, //дешифраторы « элементы задержки 10, i Jj |aS2i№BrtIT27l3, 14 группу элеме товИ. 15, элемент ИЛИ 16, генератор так товых импульсов 17. На аход 18 подается код аргумента. Вычлслитэльгое устройство предназначается ддя Бычислешгя функций Qnx-. .as)(-a, Рассмотрим работу устройства на приj мере вычисле тля миогочлена для случая . Приведенное выражение можно записать KI(,),A ajA-a., Это выражение положено в основу работы устройства. Предварительно в счетчи.к 1 и регистр 2 заносится значение /X , в счет чпк 4 значение (1 , в счетчик 7 значение Й„, а в ячейки олока памяти - зпачения 2 О общем случае коэ(}х|)111шентов в счетчик 4 заносится значение d , в СЧ(;Т чик 7 значение . а в ячейки блока мяти коэффищгенты (I. + ft -Ьюло ячеек памяти должно быть равнь1М р ft + 1 - 2 . Счетчик Б Г1редвар)гтельно уста- нав/швается в нуль. После того, как в счетчики 4 и 7. заносятся коды, дешифраторы пулепого состояния 8 и 9 открывают элементы 12 и 13. Импульсы с частотой / с выхода генератора 17 поступаю Читающие счетчики 1 и 7 и на счетчик результатов 5 через элемент ИЛИ 16 Через время Т Т Л счетчик 1 переполняется и с его выхода сигнал поступит на вычитающий счетчик 4 и перепишет код из регистра 2 в счетчик 1. Через время счетчик 4 устаО, и д -шифратор 8 закроет новится Б элемент 1.2. Счетчик 7 установится в нуль через время Я-о дешифратор 9 Закроет элемент 13. За время N. -12. Т„ в счетчик 5 поступит -Т а за время Т„ в импульсов т.J .счетчик 5 поступит ,- - w . лJ.-J-о импульсов , Всего поступит N йдХ +0„ импульса, так как сформируется код выра жения, стоящего в круглых скобках. Как только счетчики 4 и 7 встанут в О, сигналом с элемента 14 код из счетчика 6 переписывается через группу элемеитов И 15 в счетчик 4, а счетчик 5 чере лемент задержки 11 сбрасывается в О, дновременно поступает сигнал в блок амяти 6, по которому в счетчик 7 вывоится код Сразу после этого начинает я формирование выражения, стоящего в вадратных скобках, результат снова переосится в счетчик 4. По комавде обнуления четчика 7, которая следует п.осле вывода з счетчика 7 кода 0 ., производится спиывание результата вычисления со счетчиа 5, Элемент задержки 11 обеспечивает двиг импульсов при одновременном их сумирова1ши в счетчлке 5. Формула и 3 о б р о т е ни я Вычислительное устройство, содержащее счетчик , дцщифраторы, элементы задержки, счетчик результатов, генератор тактовых имнульсов, выход которого соединен с первым входом первого элемента И, выход которого соединен с раздельным входом пер - вого счетчика, разрядные входы которого подключены к выходам первой группы элементов И, первые входы которых соединены с регистром, а вторые входы - к выходу первого счетчика и к раздельному входу второго счетчика, выход которого через первый дешифратор подключен ко второму входу первого элемента Р и к первому входу второго элемента .И, выход которого подключен к первым входам второй группы элеМч нтов И, выход которого подключен к перовым входам второй группы элементов И непосредственно, а через первый элемент задержки -, к первому входу счетчика результатов, выходы которого соединены со вторыми входами второй группы элементов И, выходы которых подключены к разрядным входам второго счетчика, отличающееся тем, что, с целью расщирения функциональных возможностей устройства, оно содержит дополнительный элемент,И, элемент ИЛИ и блок памяти, вход которого соедикен с первым входом счетчика результатов, второй вход которого подключен к выходу элемента ИЛИ, первт тй вход которого соединен с выходом первого элемента И, второй вход - с выходом дополнительного элемента Икс раздельным входом трет его счетчика, разрядные входы которого соединены с блоком памяти, а выход через второй дешифратор соединен со вторым входом второго элемента И и с первым i входом дополнительного элемента И, второй вход которого через второй элемент задержки соединен с выходом генератора тактовых импульсов.

Авторы

Даты

1975-12-25—Публикация

1973-06-26—Подача