(54) УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ВЫЧИСЛИТЕЛЬНЫХ ОПЕРАЦИЙ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления @ -фазным реверсивным вентильным преобразователем | 1989 |

|

SU1837378A1 |

| Цифровой измеритель активных сопротивлений | 1985 |

|

SU1308936A1 |

| Интегратор | 1978 |

|

SU748438A1 |

| Цифровой инфранизкочастотный широкополосный фазометр мгновенных значений | 1986 |

|

SU1368806A2 |

| Цифровой измеритель температуры | 1980 |

|

SU947654A1 |

| Интегрирующий аналого-цифровой преобразователь | 1988 |

|

SU1594695A1 |

| Анализатор спектра | 1985 |

|

SU1345132A1 |

| ЦИФРОВОЙ ДИФФЕРЕНЦИАЛЬНЫЙ ФАЗОМЕТР | 1973 |

|

SU361447A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ ЭФФЕКТИВНЫХ ЗНАЧЕНИЙ ПЕРЕМЕННЫХ НАПРЯЖЕНИЙ | 1971 |

|

SU415797A1 |

| Система управления подъемником | 1977 |

|

SU622737A1 |

1

Изобретение относится к вычислительной

.технике.

Известн.. вычислительные устройства, содержащие интеграторы, входы которых соединеиы с нереключателями, выходы интеграторов через нуль -органы соединены с входами блока управления, одни входы переключателей соединены с источниками вход;ных сигналов, а другие входы - с аыхоI дом источника опорного напряжения, подклю ченного к блоку управления, соединенному

ic распределителем импульсов. Эти устройства решают ограниченный класс задач.

Цель изобретения - расширение класса :

.выполняемых вычислительных операций.

Достигач тся это благодаря тому, что устройство содержит наборное поле, через . которое выходы распределителя импульсов соединены с управ)шкицими входами переключателей, генератор импульсов, схему И-, счетчик, цифро-аналоговьгй преобразователь. к последовательно соединенные допопни.тельнью интеграторы, вход первого из соединен с выходом цифро-аналогово го преобразователя и с одним из входов .

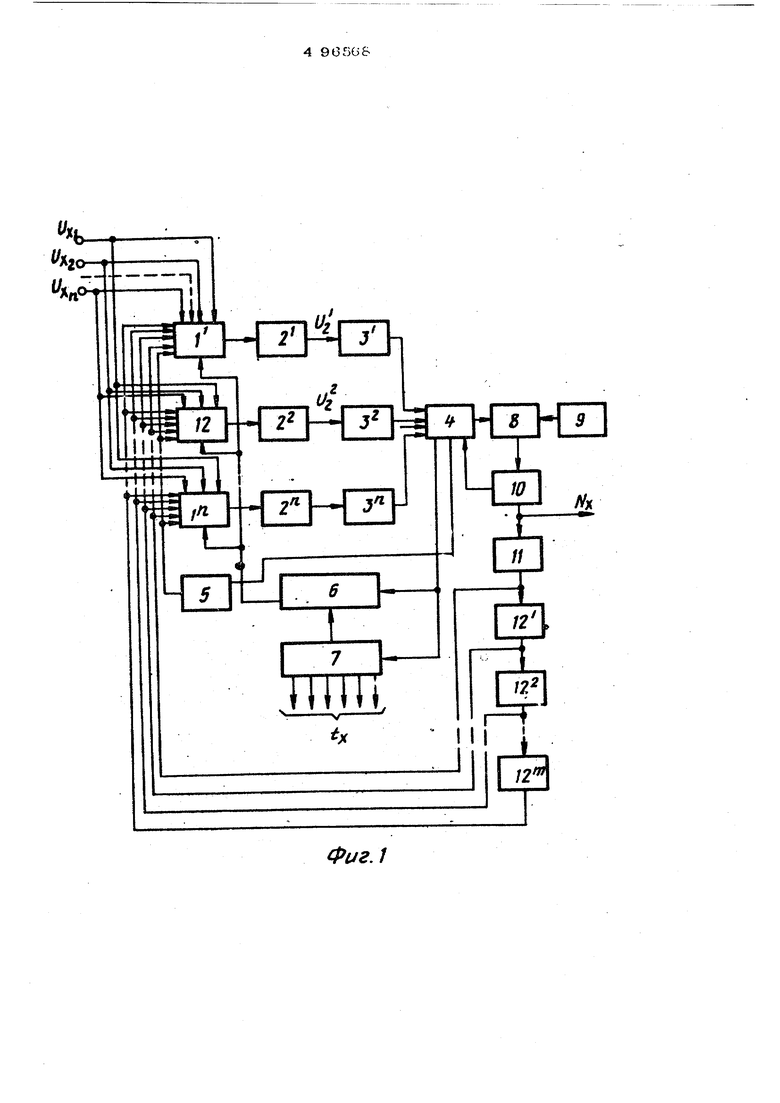

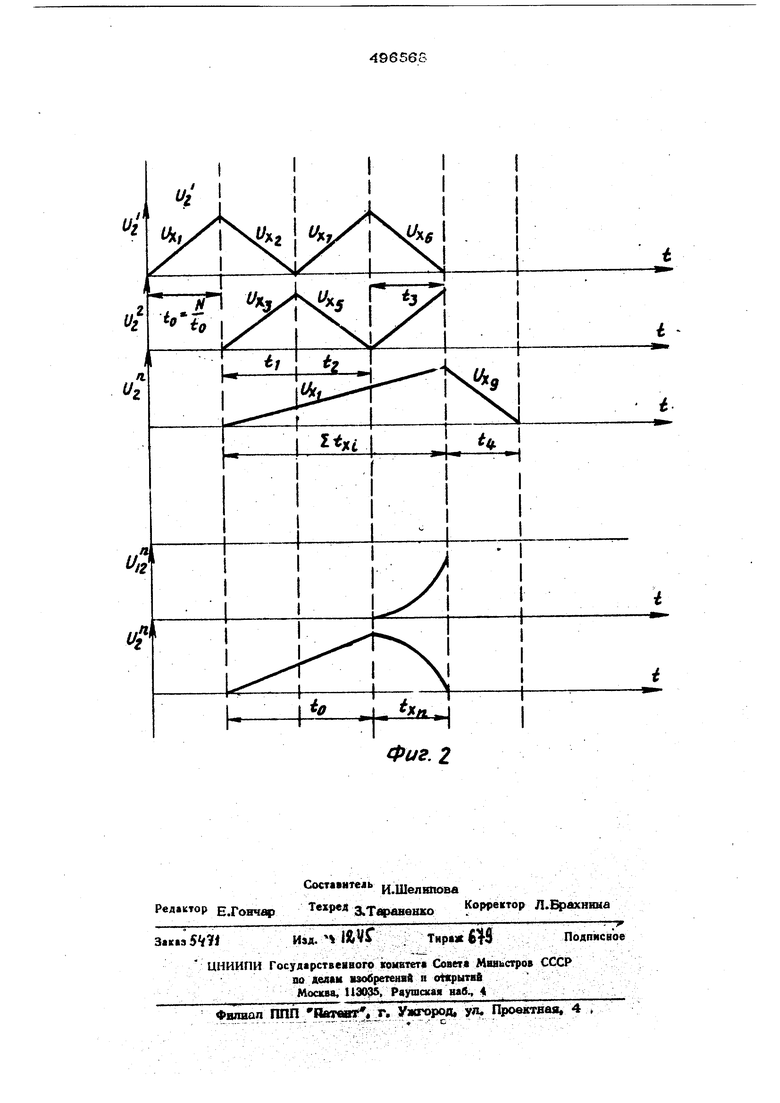

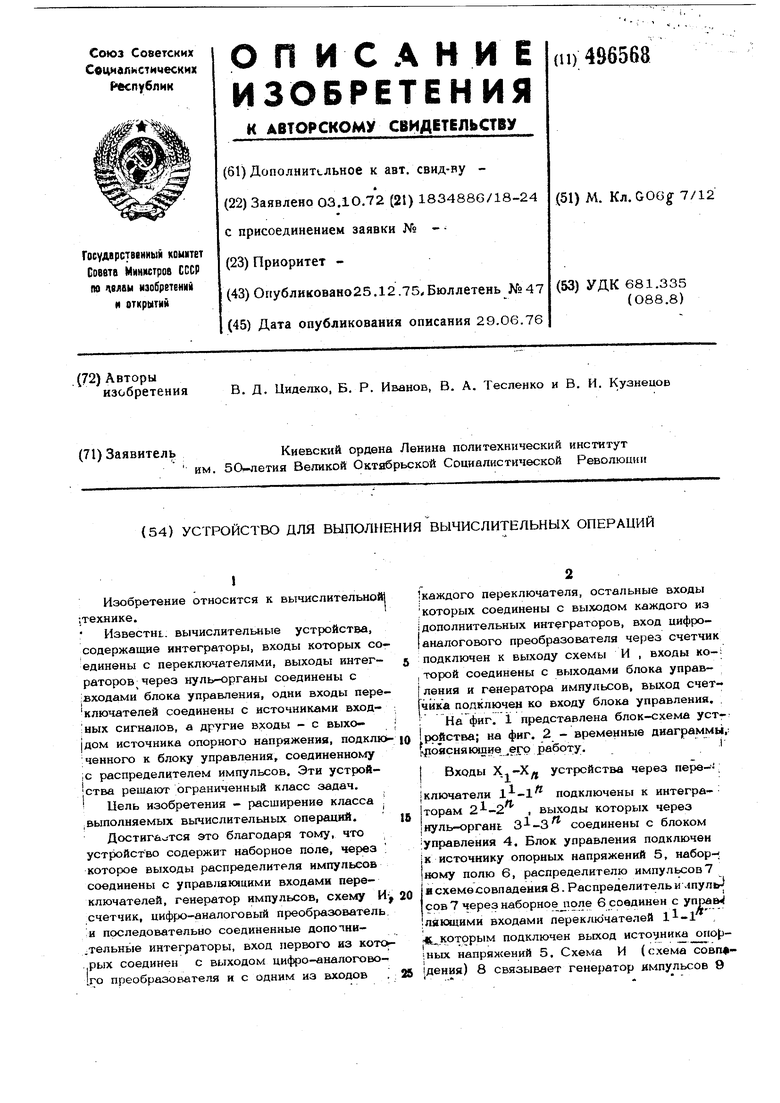

|каждого переключателя, остальные входы которых соединены с выходом каждого из i дополнительных )аторов, вход цифро аналогового преобразователя через счетчик подключен к выходу схемы И , входы ко-; I торой соединены с выходами блока управj ления и генератора импульсов, выход счетГчйка подключен ко входу блока управления. : На фиг. 1 представлена блок-схема устI ррйства; на фиг. 2 - временные диаграммы,; Ь|1оясняк пие его работу.

Входы X, устройства через пере--;

|ключатели l--- подключены к интеграторам 2 --2 , выходы которых через нуль-органь соединены с блоком |управления 4. Блок управления подключен к источнику опорных напряжений 5, наборному полю 6, распределителю импульсов 7 в схеме совпадения 8. Распределитель и лпушР сов 7 через наборное поле 6 соединен с управ«( лающими входами переключателей I- -HBL-KOTOpbiM подключен выход источника опорных напрянсений 5. Схема И (схема совпц|дения) 8 связывает генератор импульсов 9 со счетчиком 10, который подключен к блоку управления 4 и к преобразователю код-аполог 11. Выход преоб аэователя код-аналог 11 соединен с переключателя ми и с входом последоватрельной ; .-- « л цепи дополнительных интеграторов 121-12 выход каждого из которых соединен с переключателями 1 -1 . Устройство работает следукшнм образом Блок управления 4 открывает схему совпадення 8 и устанавливает переключатель 1 в одно из положений. Напряжение И подается на вход ннтегратора 2 , а в счетчик 10 проходят импульсы с частотой Д. от гено()атора импульсов 9. В момент пере полнения емкости N счетчика Ю последНИИ через блок уп|:)авления 4 перебрасывает переключатель 1 в следующее попоже нме и устанавливает переключатель 1 в положение, при котором на вход интеграто Ж 2 поступает напряжение фиг. 2). Выходное напряжение интег)атора f K-U, f равное и ) начинает уменьшаться, посколь ку на вход интегратора 2 в течение времени с подается напряжение U раз,1.xj, нополярное с и В момент установлени .1,1 нуля на выходе интегратора 2 срабатывает нуль-орган 3 и через блок управления 4 перебрасывает контакты переключателей ll и 1 в очередное положение. На вход интегратора 2 при этом подается напряжение О i аэнополярное с -- и , и выходное иапряжение интеграто-J -1ра2 уменьшается. Интегратор 2 в интервал t интегрирует напряжение U В момен установления нуля на выхаде интегратора 2 срабатывает нуль-ррган, и блок управления 4 подключает к входам 1штеграторов 12 2 и 2 следующие напряжения. Величина интегралов щ емвШ1 1.., tn ... tj при этом определввтся (яитл . tr.ib.,. f-. При заполнений интервала времеи С импульсами с частотой f в счетчике Ю запишется чэсло м - ./7 Ш ... - « П Uj,, чястном случле, когда вместо УХ или h , подеется нлпрйженис U oi источника порных напряжений 5, в счетчике запишет ;/.-i/:, я число, равное и-. тг я 1 П Jj,. ft . W J: где К U0 N .J При Ux, const , либо и j.- const , соответственнс) .A л Таким образом, с помощью распределнгелй импульсов 7, который управляет наборным полем б, задается любая последователы ость подключения входных напряжений к входам интеграторов и число, записанное в Счетчике 10, в общем случае оп(юделяется выражением:yj . yj , 7; %:,-u3,../ где К i , т, , р, , г Q, 1, 2,... Предлагаемое устройство может применяться для получения интервала времени или кода, пропорциональных отношению или проведению сумм входных напряжений U. При этом на вход интегратора 2 подается напряженке И (см. фиг. 2) в интервале . фиг. 2) в 1 3 в рремени 2iл; после чего конденсатор интегратора 2 разряжается напряжением ffvn Д° нулевого уровня. Интервал време Х 3 ни разряда й- f,- или л в общем виде tx Для получения интервала времени блок управления 4 открыва-время 2 ix; ет схему совпадения 8 на при том на выходе преобразователя коданалог в конце интервала ваярвженке рав-, но,1 , -Л.. где tJQ - опорное напряжение ареобраэова-j теля код-аналог 11. К,-ко8ффшшент преобразователя код-аналог 11. Напряжение1/.,- подается для разряда конденсатора интегратора 2 , выходн напряжение которого пропорционально - ., 1 тогда интервал разряда определится выраже нием iiliiL --- . к коэффициент пропорциональности. Предлагаемое функциональное устройств позволяет производить извлечение корня frt -ой степени из напряжения. Напряжение, из которого нужно извлечь .корень, подается на интегратор 2 через переключатель 1 в течение фиксированно интервала времени f. Л- . После заполIOfнения емкости счетчика Ю блок управления 4 открывает схему совпадения 8 и подключает к входу интегратора 2 либо ли нейно-нарастающее напряжение с выхода преобразователя код-аналог {для извлечения квадратного корня) либо напряжение .с выхода интегратора -2 (для извлечения корня ffi-ой степени). Поскольку напряжение, из ко|ррого нужно извлечь корень f7l-oй степени, может быть пропорционально как отношению суммы так и отношению произведений входных величин, то предлагаемое устройство обладаi ет широкими функциональными возможностя тями при высокой точности и быстродействии. р е л м е т и з о б р т е н и я ; Уст{юйсТ|ВО для вытюлнения 1м.числигел «.;Ных операций, соде1 жя1цее интеграторы, входы которых соединены с переключателяI ми, выходы интеграторов через нуль-орга|ны соединены со входами блока управления, одни входы переключателей соединены с источниками входных сигналов, а другие входы - с выходом источника опорного нд-« пряжения, подключенного к блоку управления, соединенному с распределителем им- ; пульсов, отлича. ющееся teM, i Гчто, с целью расширения класса выполнявjMbix вычислительных операций, оно содер-; жит наборное поле, через которое выходы распределителя импульсов соединены с уп-« равляюшими входами переключателей, гвнв«ратор импульсов, схему И , счетчик, циф1:ю-аналоговый п{зеобразователь и последовательно соединенные дополнительные интеграторы, вход первого из которых соединен с выходом цифро-аналогового преобразователя и одним из входов каждого переключателя, остальные входы которых соединены с выходом каждого из дополнительных интеграторов, вход цифро-аналогового преобразователя Через снетчик подключен к выходу схемы И , входы которой со.единены с выходами блока управления и ге.нератора импульсов, выход счетчика Г1одклк чен к входу блока управления.

Фиг.1

Фиг. 2

Авторы

Даты

1975-12-25—Публикация

1972-10-03—Подача